みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、キオクシアが2024年のIEDMで発表する「OCTRAM」について調べてみます。

(完全に趣味で書いているので、間違っている部分があれば教えてください。かつ、公開情報をなるべく集めていますが、事実と異なる部分があればご指摘いただけると幸いです。)

OCTRAMの発表内容

IEDMでの発表タイトルは、「Oxide-semiconductor Channel Transistor DRAM (OCTRAM) with 4F2 Architecture」です。

要は、酸化物半導体をチャネルにしたトランジスタで、DRAM作って、しかも4F2構造ですよ、ということです。

abstractの部分だけ引用します。

We demonstrated the world’s first 4F2 gate-all-around Oxide-semiconductor Channel Transistor DRAM (OCTRAM). The InGaZnO VCT achieved Ion=15uA/cell (Vg=2V) and Ioff=1aA/cell (Vg=-1V). A 275Mbit OCTRAM array was fabricated with WL 54nm/BL 63nm pitches and showed successful operation in the designed voltage range, making it a breakthrough technology for future 4F2 DRAM.

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?ScheduleID=340

細かい内容はあとから見ていきますが、こんな感じのことが書いてあります。

セッションの冒頭部分も引用してみます。

DRAM utilizing oxide semiconductor (OS) channel cell transistor has been an interesting topic since OS channel provides promising device properties such as high current and low leakage, as well as great scalability and future extendability for 3-dimensional DRAM structures. In this session, seven papers focusing on the recent progress in DRAM with OS channel will be presented. In the first paper, Kioxia demonstrates the 4F2 gate-all-around OS channel transistor integrated IGZO vertical channel transistor on top of a high aspect ratio capacitor.

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?ScheduleID=60&

酸化物半導体にはIGZOが使われていて、デバイス特性としてはオン電流が高くオフリーク電流が小さいことが謳われています。

また、トランジスタが縦型構造なので、3D DRAMの構造に適用しやすいようです。

着目する部分

てなわけで、今回の記事で着目するのは、こちらの部分です。

・トランジスタのオンオフ特性

・4F2構造

・酸化物半導体の特性

キオクシアの過去の発表

細かいところを見る前に、キオクシアが過去に学会発表している内容を見てみます。

キオクシアの先端技術トピックスのページで、過去に学会発表された成果がまとめられています。

今回着目したのは、この2つです。

フッ素添加による高耐熱性と高オン電流を両立する酸化物半導体FETチャネル材料の設計

新規酸化物半導体InAlZnOをチャネルに用いた短チャネル(Lg=40nm) 立体ゲート縦型トランジスタの動作実証

フッ素添加の方が2020年のIEDMで、酸化物半導体の縦型トランジスタの方が2020年のVLSIでそれぞれ報告されていたようです。

OCTRAMの発表を見ると、過去の2件がつながっているように見えます。

フッ素添加の発表は、IGZOに対してFGA(フォーミングガスアニール)を掛けた時にVT(閾値電圧)がシフトしていた問題を、高濃度のフッ素イオン注入によって改善できますという内容です。

酸化物半導体の縦型トランジスタの発表は、チャネル材料にIAZO(InAlZnO)を使うことで、縦型トランジスタを形成することができ、閾値電圧変動もほとんどないという内容です。

おそらく、酸化物半導体チャネルを使ったトランジスタでDRAMを作ったという発表は、前の2件の発表を合わせてDRAMまで実装しましたよ、という内容になるのではなかろうかと推察されます。

リンク先を見ていただくと、デバイス構造の断面も載っていて、なんとなく構造が推測できます。

4F2構造

次に、今回推されている、4F2の構造について簡単に見ていきます。

DRAMの専門家ではないので、wikipediaを参考にしています。

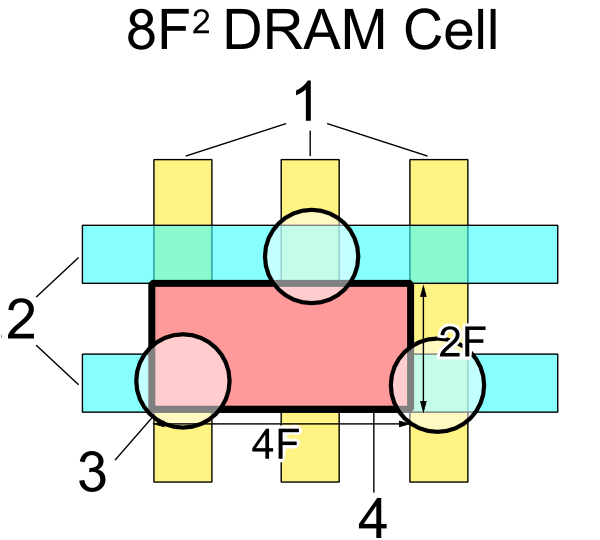

一般的なDRAMの構造は、8F2のようです。

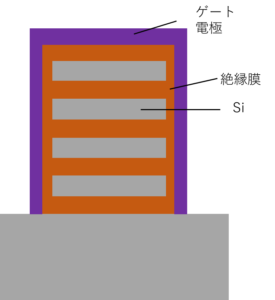

図のような構造で、トランジスタとキャパシタが並ぶ形になっています。

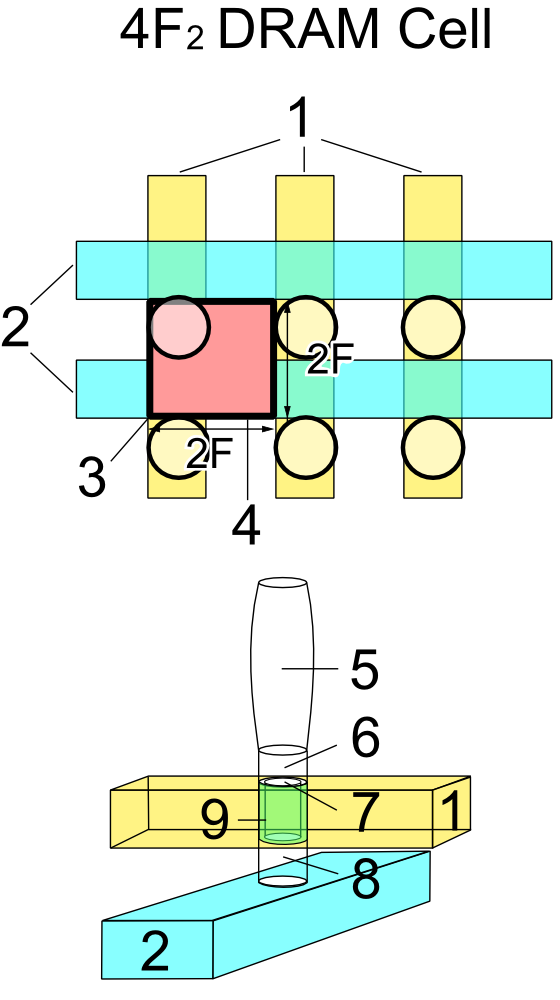

一方で、今回考えている4F2はこの図のような構造を取っていて、トランジスタとキャパシタを縦型に積層したような形になっています。

黄色い線がワードラインで、水色の線がビットラインです。

4F2にできると、1セルあたりの面積を縮小できるので、高集積化には有利です。

ただ、4F2の構造を取ろうとすると、トランジスタを縦型に形成する必要があります。セルへのアクセスを制御するトランジスタは、一方はビット線に、もう一方はキャパシタにつながっている必要があります。

また、トランジスタのゲートはワード線につながっている必要があります。

このような構造を取ろうとすると、トランジスタをシリコン基板上に形成するのは困難です。

すると、トランジスタのチャネルを単結晶シリコン以外の材料で形成する必要が出てきます。

単純に縦型のトランジスタを作るだけであれば、poly-Siでチャネルを形成することは可能ですが、poly-Siだとどうしても多結晶になるので、移動度が低くリーク電流が増えてしまいます。

DRAMの特性上、トランジスタのリーク電流が増えるとキャパシタから出ていく電荷が増えます。

1セルあたりの面積を縮小するためには、キャパシタの基板上に占める面積(フットプリント)を小さくしないといけないので、キャパシタの容量は小さくなりがちです。

キャパシタの容量を小さくしようとしているのに、トランジスタのリーク電流が増えてしまうと、キャパシタが電荷を保持できなくなるので、リーク電流が増えるのは許容できません。

というわけで、DRAMのトランジスタは、リーク電流をできる限り減らす必要があります。

データを図にしてみる

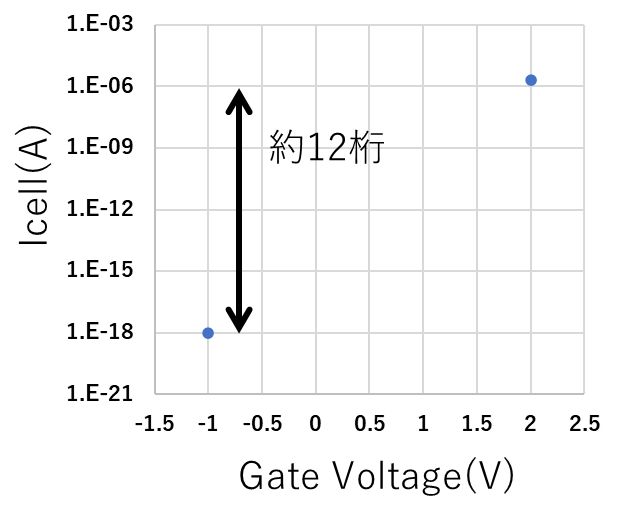

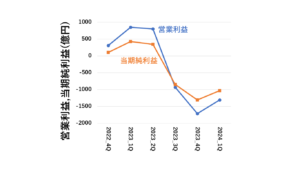

DRAMはリーク電流を減らす必要があるという前提をもとに、キオクシアがabstractで出しているデータを見てみましょう。オン電流とオフ電流はこのように書かれています。

Ion=15uA/cell (Vg=2V) and Ioff=1aA/cell (Vg=-1V)

文字で書かれても理解しにくいので、図にしてみます。

各Vg(ゲート電圧)におけるIcellを図にするとこのようになります。

3Vので、約12桁変わってるんですね。1aAは、1×10-18Aです。(アトアンペアなんて測定できるんですね・・・)

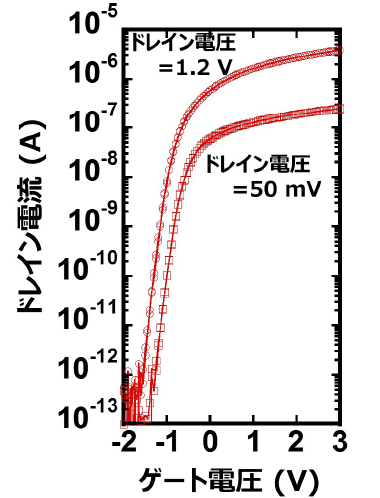

参考として、キオクシアの縦型トランジスタのId-Vg特性の図を載せています。(下記リンク先から引用)

新規酸化物半導体InAlZnOをチャネルに用いた短チャネル(Lg=40nm) 立体ゲート縦型トランジスタの動作実証

Vgが2Vと-1Vを比較しても、約5桁のオンオフ比なので、この図の倍くらいオンオフ比が大きいことがわかります。

というか、オフ電流が極端に低いです。

今回のIEDMの発表のとおりであれば、オフ電流が非常に小さいので、DRAMのセルのリークを減らすのには効果的だと考えられます。

オフリークの小ささが衝撃的なので、本当なのかな?と思うところはありますが、IEDMに出すくらいなので本当なんでしょう。

構造としては面白い

オフリーク電流の小ささと、4F2構造のメリットを書いてきました。

一応、キオクシア曰はく、4F2のDRAMは世界で初めてだそうです。(他社のDRAMの発表を調査できているわけではないので、字面を信じて書いているだけです)

発表内容を見たわけではありませんが、abstractから読める部分だけを見ても、非常に技術的には面白いと感じます。

一方で、課題として考えられるのは、この3つです。

・キャパシタ性能とトランジスタ性能の両立

・IGZOチャネル加工の安定性

・ビットコストが既存のDRAMと比較してどうか

キオクシア自体も発表していますが、IGZOをチャネルに用いるとFGA時に閾値電圧が負側にシフトするようなので、どの程度の高温熱工程にIGZOチャネルが耐えうるかというのは、ポイントになると考えられます。

また、IGZOチャネルの加工を安定的に行うことができるかどうかも課題になると考えられます。(SiO2やSiのように、容易にドライエッチングできればいいんですが。)

最後に、特性が出たとしてもDRAMとして売り出すためには、既存DRAM製品とのコスト比較が必ず出てきます。

IGZOをチャネルに用いているので、既存DRAMと比較してコストが安くなるかと言われると微妙なところです。

性能と面積縮小の効果が、どの程度出せるか?と言う点と、製品化するのであればどの市場を狙うのか?というところがポイントでしょう。

どれだけ性能が高くても、世界一の高集積化ができたとしても、DRAMの市場で需要が無ければ売れません。

一つ思い出すのは、Intel-Micronが過去に作っていたOptaneです。相変化メモリを使ったメモリで、NANDより速くDRAMより遅い不揮発性メモリの立ち位置でした。

結果的に、不揮発性メモリの用途では価格でNANDに勝てず、揮発性メモリとしてはDRAMの方が速いので、大きな需要が生まれず、コスト高であったこともあって、生産中止となってしまいました。

相変化メモリを集積する技術は非常に高かったと考えられますが、市場が出来ず消えてしまったメモリの一つです。

OCTRAMも、技術的には非常に面白いと思うので、求められる市場を開拓できるかが、今後広がっていくかどうかのキーになると考えられます。

もしかすると、IEDMで対外的に成果を出すことが一つの目的なのかもしれないですが、学会発表でストップではなく非常に面白いのでDRAMへキオクシアが攻勢をかける一つの手段になれば面白いなと思っております。

まとめ

この記事では、キオクシアが2024年のIEDMで発表する「OCTRAM」について書きました。

まだ、abstractを読んだだけですが、非常に面白い内容だと思っています。私はIEDMには行けないですが、どんな内容の発表なのか楽しみです。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント

コメント一覧 (2件)

記事、ありがとうございます。NANYAと一緒に開発しているようですね。各社とも三次元構造のDRAMにはやはり注目しているようですが、NANDと同様2Dから3Dへの転換には時間(設備というよりも製品化自体)がかかりそうですね。

通りすがり様

コメントありがとうございます。東急三崎口です。

記事読んでいただいてありがとうございます。

DRAMの3D化に際して、各社着目しているのは間違いないと思います。

製品化自体には時間がかかると思いますが、いずれやってくる転換点ではあるので、

技術的に先んじておきたいところではあると思います。

今後ともよろしくお願いいたします。