みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、n-Geのフェルミレベルピニングを解消できる方法として出ていた論文について、書いていきます。

内容としては、かなりマニアックで、Geの界面・電気物性に詳しい方向けに書いているので、御了承下さいませ。(一般の読者の方が読んでも、何が書いてあるかちんぷんかんぷんだと思います。)

Geのフェルミレベルピニング

本題に入る前に、Geのフェルミレベルピニングの強烈さについて、簡単に触れておきます。

一般的に、半導体の教科書では金属と半導体を接合すると、金属の仕事関数によってオーミック接触になったり、ショットキー接触になったりすると書かれていますが、現実はそうはなりません。

教科書通りになってくれればうれしいんですが、金属と半導体を接合すると、フェルミレベルピニングが多かれ少なかれ起こります。

その中でも、Geはフェルミレベルピニングが強烈に起こります。

接触させる金属種を変えても、基本的に金属とGeの接合界面では金属のフェルミレベルがGeの価電子帯近傍にきます。

このせいで、P型では基本的にオーミック接触となりますが、N型では基本的にショットキー接触になってしまいます。

ある意味、P型へのコンタクトはどんな金属種を使ってもオーミックになるので都合がいいです。

一方、N型へのコンタクトは、どんな金属を使ってもショットキーになるので、良好なコンタクトを取るのが困難であるという大前提があります。

論文の内容のすごさ

n-Geに対して、基本的に金属種を変えてもショットキー接合が形成されることは、よく知られていますが、今回の論文ではn-Geに対してBiTeを積み、積んだ後アニールを行うことで、オーミックライクな接触が取れることが述べられています。

論文のリンク先は下記です。オープンアクセスのようなので、誰でも読むことができます。

https://pubs.aip.org/aip/apm/article/13/7/071117/3352347

結果的に、BiTe中にGeが入ったGBT層は、Ge界面に対してファンデルワールス結合を形成していて、結果的にMIGSを抑えてコンタクトがオーミックライクになるようです。

正直な感覚、半導体デバイス屋さんから見ると、GeはともかくBiTeはゲテモノに見えるでしょうから、試してみようという気持ちも起こらないのではないでしょうか。

また、BiTeを使っている人から見ても、BiTeを400℃に加熱するのは、基本的にやりません。

融点が585℃と言われており、400℃近くまでBiTeの温度を上げるような用途で使われることは、ほとんどないからです。

もっと言うと、BiTeは熱電発電やペルチェ素子の材料として使われますが、BiTeのゼーベック係数は200℃を超える領域では室温と比較してかなり性能が落ちてくるので、実用的に使われることはほとんどありません。

つまり、GeにBiTeを接合して400℃まで温度を上げると言うのは、「どちらの世界でも一般的ではないことをやってみたらうまくいきました」という感覚に私は見えます。だからこそ、今まで発見されていないようなデータが見えたのでしょう。

絶縁膜を挿入する先行論文

今回取り上げている論文以外にも、n-Geに対して、オーミックな接合を実現しようという取り組みは、過去から行われています。

非常にわかりやすいのが、鳥海先生が中心にやられていた研究です。

応用物理 第86巻 8号 (2017)に載っている、解説記事がわかりやすいです。(リンク先は下記です。)

https://www.jstage.jst.go.jp/article/oubutsu/86/8/86_673/_pdf/-char/ja

Geに対して、極薄GeO2層を挿入することで、n-Geはオーミックに、p-Geはショットキーに接合が変化することが示されています。

この結果から、GeのフェルミレベルピニングにはMIGSが効いているであろうことは、予測できると考えられます。かつ、浅学ながら私もこの応用物理の記事を読んだ時に、MIGSが効いているのだろうと、思っていました。

極薄GeO2層を挿入することでn-Geのコンタクトがオーミックに変わることは示されていますが、絶縁膜を挿入することで直列抵抗は増えるので、完全なオーミックコンタクトにはなりきっていないです。

つまり、従来の研究結果からすると、GeのフェルミレベルピニングはMIGSが原因だと考えられているものの、MIGSを抑制しようとして金属の波動関数が半導体中に流れ込むのを抑えようと絶縁膜を挿入すると、直列抵抗が上がってしまうので、なかなか難しいという感覚だったはずです。

n-Geのフェルミレベルピニングが解消できるのは画期的

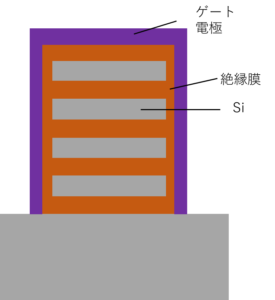

今回取り上げた論文では、n-Ge上にBiTeを堆積し400℃で加熱することで、GBT層(GeとBiTeの混晶)を形成しています。

GBT層とGeの界面にTeが並ぶことで、Ge界面をパッシベーションした形になり、オーミックコンタクトが取れているようです。

なぜこんなことが起こるのか?について考えてみます。

まず、BiTeの結晶構造は、少しマニアックです。ネットで出てくる構造のリンク先は下記のとおりです。

https://www.salesio-sp.ac.jp/papers/sotsuken/2006/pdf/documents/ec/4332.pdf

基本の格子構造は六方晶で、BiとTeが結合しており、Te-Te間の結合はファンデルワールス結合をしています。

このため、Te-Te間の結合が非常に弱く、この面では簡単にへき開します。

逆に言うと、BiTeの材料はTe-Te間界面は非常に結合が弱く、この面でファンデルワールス結合を取りうる結晶構造を元々しているのがポイントです。

かつ、BiTeの結晶だと、c軸方向に対して5原子ごとに周期構造を取っていますが、GeがBiTe中に入ったGBTでは周期構造の単位が7原子に変化したようです。(これが驚きです。)

結果的に、GBT層のTeがGeの表面をパッシベーションする形で、MIGSの形成が起こらなかった結果、n-Geに対してオーミックコンタクトが取れるようになったのではないかと考えられます。

本当はバンド構造まで予測できればよかったんですが、BiTeがゲテモノ材料すぎて、簡単に描けませんでした。

バンド構造はどうあれ、n-Geに対してオーミックライクなコンタクトが取れるようになったことは、非常に画期的だと言えるでしょう。

デバイス導入に出てくるであろう課題

さて、n-Geに対するオーミックライクなコンタクトがBiTeを使うことで本当に取れるとした時に、デバイスに導入しようとしたときに生じうる課題をさらっと考えてみます。

・コンタミ問題

・GBT/Ge界面の熱安定性

・BiやTeのデバイス中での拡散

1つ目のコンタミ問題は簡単で、BiやTeをスパッタする以上、ベベルやエッジ部に付着したBiTeを除去する必要があります。

薬液で処理できるのかわかりませんが、不要部についたBiTeを除去できるように対応する必要があります。

2つ目の、GBT/Ge界面の熱安定性は、結構シビアな問題です。GBT/Ge界面だけを考えたときにオーミックコンタクトが取れたとしても、オーミックコンタクトの形成後には金属配線を形成する必要があります。

金属配線等の形成プロセスでかかる熱工程で、GBT/Ge界面の特性がショットキーに変化してしまう場合、実デバイスへの適用は困難を極めます。

High-k/Metal Gate構造のように、ゲートスタック形成を熱工程のあとに持っていくような大技が使われたこともありますが、コンタクトの形成後に金属配線を形成する流れを変えるのは厳しいので、GBT/Ge界面の熱安定性は実用上は非常に重要であると言えます。

3つ目は、BiやTeのデバイス中の拡散です。

BiやTeは、シリコンデバイスではあまり使われている材料でしょうから、デバイス形成時の熱工程などを通して、他の場所へ拡散してしまうリスクがあります。

SiやGe中での拡散係数が、非常に小さいのであれば問題ないですが、Geの上にBiTeを堆積して加熱しただけで、GeがBiTeに拡散していくのを考えると、拡散係数が小さいわけはないだろうという見立てです。

ぱっと考えただけでも、3つくらいの課題は思いつきます。

やはり、コンタミに関しては手の打ちようがありますが、GBT/Ge界面の熱安定性が無いと、クリティカルな問題になるので、どんな特性なのか是非見てみたいものです。

まとめ

この記事では、n-Geのフェルミレベルピニングを解消できる方法として出ていた論文について書きました。

Geのフェルミレベルピニングに悩まされた経験のある方は、非常に興味深い内容だったのではないでしょうか。

GBT/Ge界面を形成することでMIGSを抑制するのは、学術的には非常に興味深い内容です。

実デバイスへの応用という面では、GBT/Ge界面の熱安定性がキーになると思われます。

EE Timesで出ていて、見た瞬間驚愕してつい記事を書いてしまいました。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント