みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、NANDフラッシュメモリの動作原理について、二次元NANDフラッシュの構造を例にとって基礎的な部分を解説します。

フラッシュメモリの現在の開発は三次元NANDに移っているので、本当は三次元NANDの技術解説をやりたかったんですが、二次元NANDの仕組みがわからないと三次元NANDの仕組みは絶対に理解できないです。そこで、まずは二次元NANDの動作原理を解説しようというのが、この記事の目的です。

NANDフラッシュメモリの構造的な特徴

最初に、NANDフラッシュメモリのメモリセルの構造的な特徴を見ていきます。

構造的な特徴を一言で表すと、「トランジスタ+フローティングゲート」です。

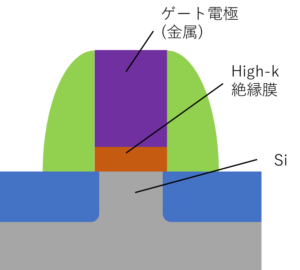

トランジスタの構造は、先端ロジック半導体で開発されている、GAA(2nmプロセス)やFinFET(~22nmプロセス)ではなく、昔からあるプレーナー型のトランジスタです。

プレーナー型のトランジスタの構造と動作については、こちらの記事で解説しています。ご存じない方は、こちらの記事を読んでからこの記事を読み進めていただけるとわかりやすいです。

トランジスタ(Tr)+フローティングゲート(FG)

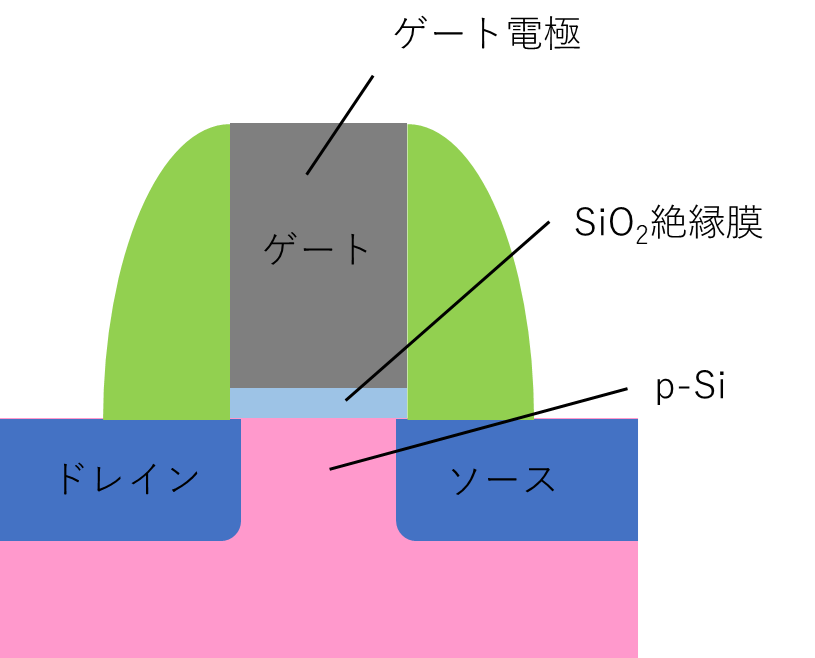

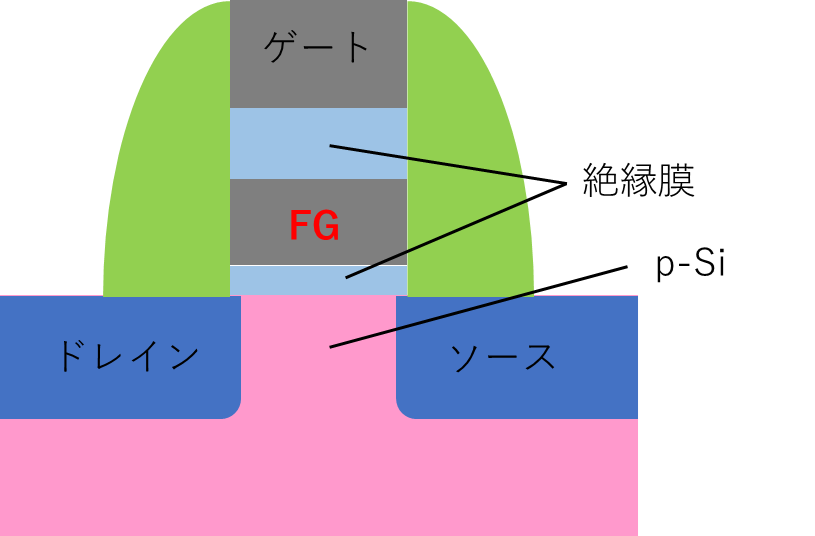

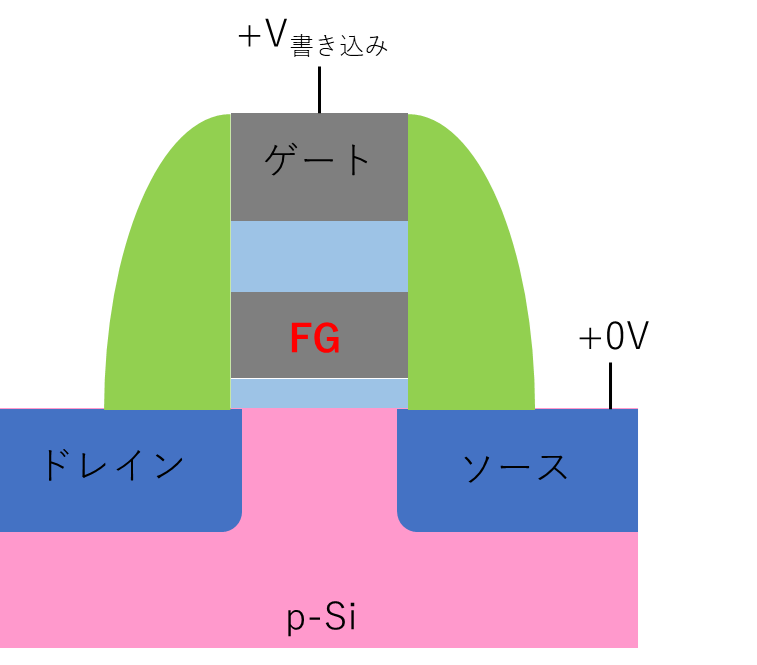

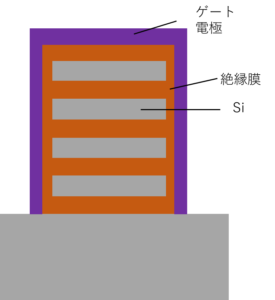

二次元NANDフラッシュメモリの構造的な特徴は、トランジスタ+フローティングゲートだと書きました。文章で書くとわかりにくいので、まずは図を見てみてください。

プレーナー型トランジスタの模式図は、このようになっています。

一方、二次元NANDフラッシュメモリのセルの構造は、プレーナー型トランジスタにフローティングゲート(FG)を付け足した形になっています。

プレーナー型トランジスタのゲートと基板の間に、FGと書かれたものが追加されています。このFGに電子を注入したり、電子を抜いたりして二次元NANDフラッシュメモリはデータを記憶しています。

フローティングゲートと呼ばれる理由は、構造に由来しています。図の中では省いていますが、ドレイン・ソース・ゲートは電極が付けられていて、それぞれのが必要な電位になるように電気的に接続されています。

しかし、フローティングゲートは、基板側とゲート側両方が絶縁膜になっていて、電気的に接続されていません。(日本語で浮遊ゲートと書かれることもあります。)FGは電気的に浮いている状態なので、フローティングゲートと呼ばれているわけです。

NAND型フラッシュメモリの構造の特徴をまとめると、「基本構造はプレーナー型トランジスタ」であり「ゲート部分にフローティングゲートが追加されている」ことです。

主な動作

NANDフラッシュメモリの構造的な特徴を解説したので、次は主な動作について解説します。

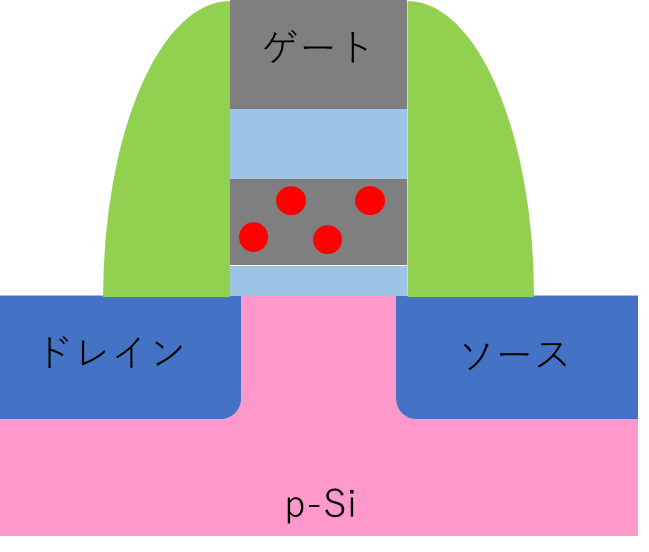

フラッシュメモリは、FGに電子を入れたり出したりすることで、データを記憶しています。(どうやってFGに電子を出し入れするのかは、のちほど解説します。) FGは他の部分と電気的につながっていないので、FGの電子は逃げることができず、メモリの電源を切ったとしてもデータは保持できます。

NANDフラッシュメモリは、電源を切ってもデータが保持できることが一番大きな特徴です。電源を切ってもデータが保持できるメモリのことを、不揮発性メモリと言います。一方、DRAMのように電源を切るとデータが消えてしまうメモリを揮発性メモリと言います。

2023年現在で、不揮発性メモリとして一番メジャーなのはNANDフラッシュメモリなので、「不揮発性メモリ」=「NANDフラッシュメモリ」だと思っていただいて構いません。(厳密なことを言うと、NOR型フラッシュメモリも不揮発性メモリですし、生産が終わってしまったIntel-MicronのOptaneや3D XPなんかも不揮発性メモリです。)

不揮発性メモリの王様であるNANDフラッシュメモリの動作は、大きく分けて3つあります。

・書き込み

・読み出し

・消去

新しいデータを書き込めて、書き込まれたデータを読むことができて、書き込んだデータを消すことができるというものです。それぞれについて、簡単に解説していきます。

書き込み

まずは書き込みです。NANDフラッシュメモリの動作原理を理解するうえで、ここが一番重要です。

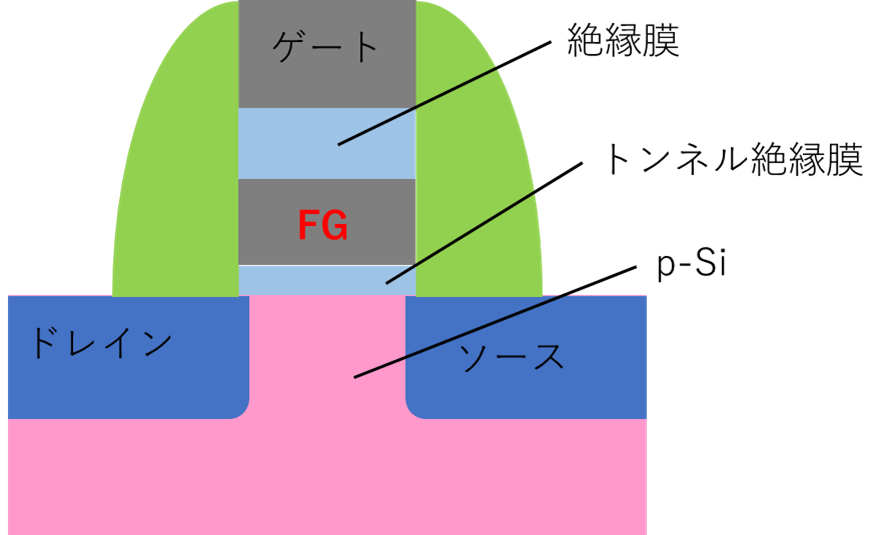

書き込みを行う時のゴールは、FGに電子を注入することです。順を追って説明します。データを書き込む前の状態は、このようになっていて、FGには電子がいない状態です。ゲート部分の絶縁膜で、FGと基板の間にあるものを、トンネル絶縁膜と書いています。

結論を言うと、ゲートに高い電圧をかけてやると、トンネル絶縁膜を電子が通り抜けることができるようになり、FGに電子を注入することができます。

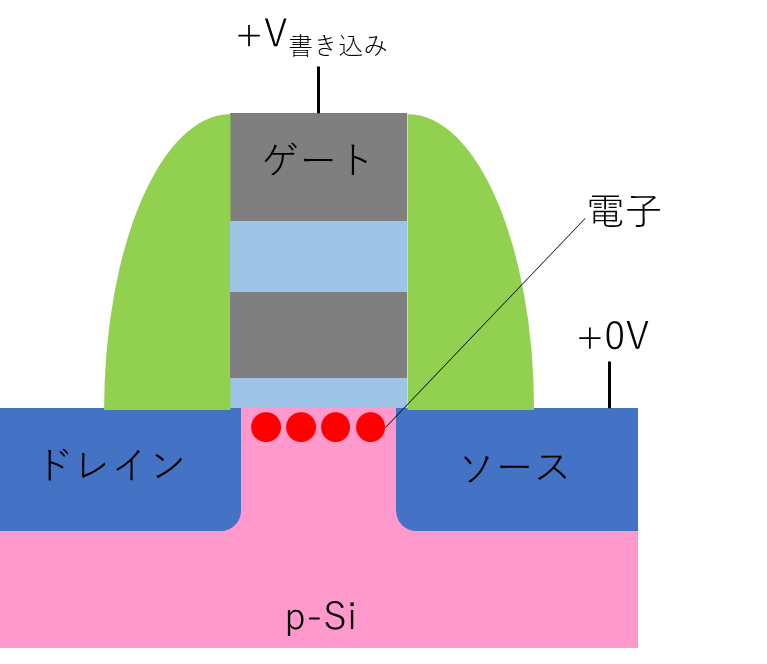

書き込み動作を行うときは、ゲートに書き込み用の電圧(V書き込み)を掛けて、ソースとドレインを0V(グラウンド)にします。そうすると、基板とゲートの間にFGへ高い電圧をかけることができます。

基板とFGの間に高い電圧が掛かると、基板側に電子が発生します。

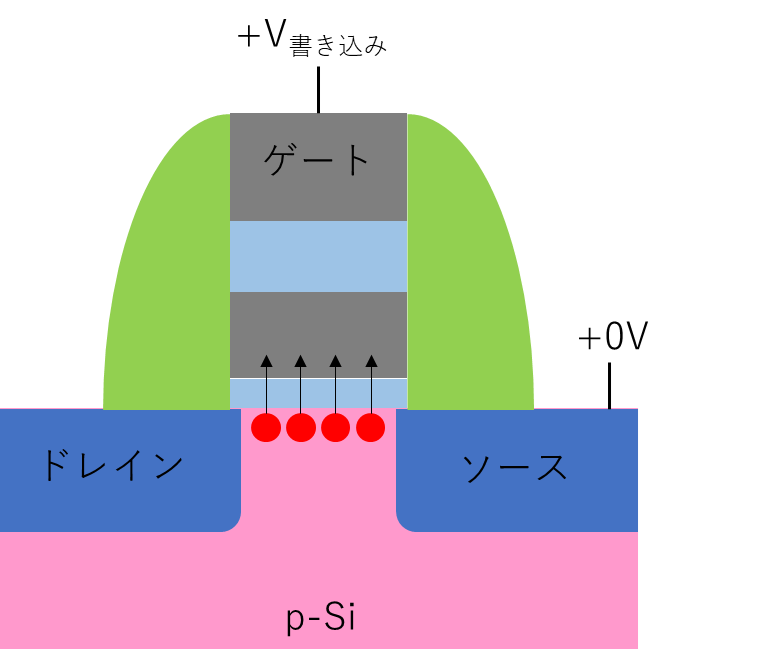

そして、基板側の電子がトンネル絶縁膜を通り抜けて、FGに移動することで書き込みが完了します。

書き込み完了後は、このような形になります。FGの中に電子が注入されました。FGは、他の部分と電気的につながっていないので、一度注入された電子はそのままFGの中にとどまります。

書き込みの簡単な流れを解説しました。書き込み時に、トンネル絶縁膜を電子が通り抜けていました。通常の状態では、絶縁膜が存在すれば基板からFGに電子が通り抜けることはできません。しかし、トンネル絶縁膜の厚さを非常に薄くして、かつ高電圧を掛けてやると、「トンネル効果」と呼ばれる現象を利用することができるようになります。

トンネル効果をちゃんと理解しようとすると量子力学を学ばないといけませんが、簡単に言うと絶縁膜が非常に薄くなると量子力学的な効果が出てくると考えてください。(トンネル効果について詳しく知りたい方は、こちらのリンク先で詳しく解説されているので読んでみてください。)

http://www.cmpt.phys.tohoku.ac.jp/open-campus/2020/quantum_tunnel/

読み出し

次に書かれたデータを読み出す方法を解説します。

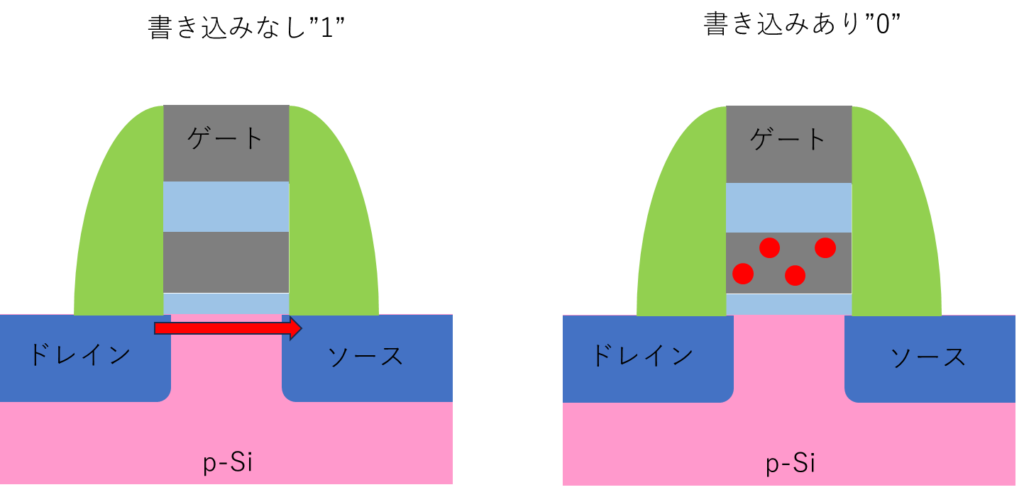

読み出しの時には、メモリセルに電流が流れるかどうかで判断されます。NANDフラッシュメモリは、電子が書き込まれていない状態(書き込まれていない状態)の時に、電流が流れるように設計されています。

メモリセルに電流が流れる状態を”1″、電流が流れない状態を”0″として考えてみます。つまり、これは01のデジタルデータを各セルのFGに電子が注入されているか、されていないかに置き換えています。

0の状態と1の状態のメモリセルを並べると、このようになっています。

つまり、各セルに書き込まれているデータが”0″なのか”1″なのかは、それぞれのセルに電流が流れるかどうかを判定すればいいわけです。セルに電流が流れれば1、流れなければ0と判断することで、データを読み出すことができます。

個別のセルの読み出しに関しては、電流が流れるかどうかで判断していると考えてもらって構いません。NANDフラッシュに詳しい方は、大事な部分の説明を省略していることにお気づきかもしれませんが、次の章でもう少し詳しく説明します。

消去

最後に、書き込まれたデータを消去する方法を解説します。

書き込まれたデータを消去するということは、構造的な観点で言い換えると、FGに注入された電子を引き抜くことになります。FGに注入された電子を引き抜くということは、簡単に言うと書き込みと逆のことをします。

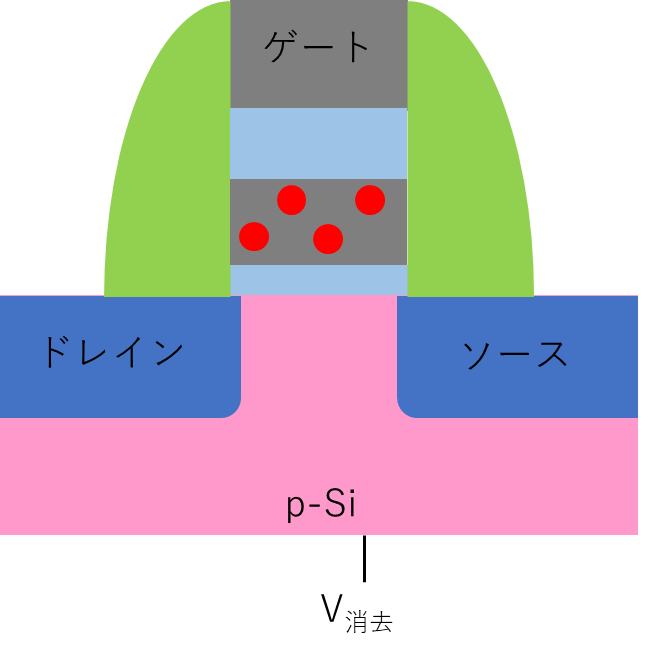

消去する前の状態(FGに電子が注入されている状態)のメモリセルはこのようになっています。

この状態から、基板側にFGから電子を引き抜くための電圧を掛けてやります。(図中ではV消去と書いています。)

消去するための電圧も、電子がトンネル絶縁膜を通り抜けられる程度の、それなりに高い電圧が掛かります。

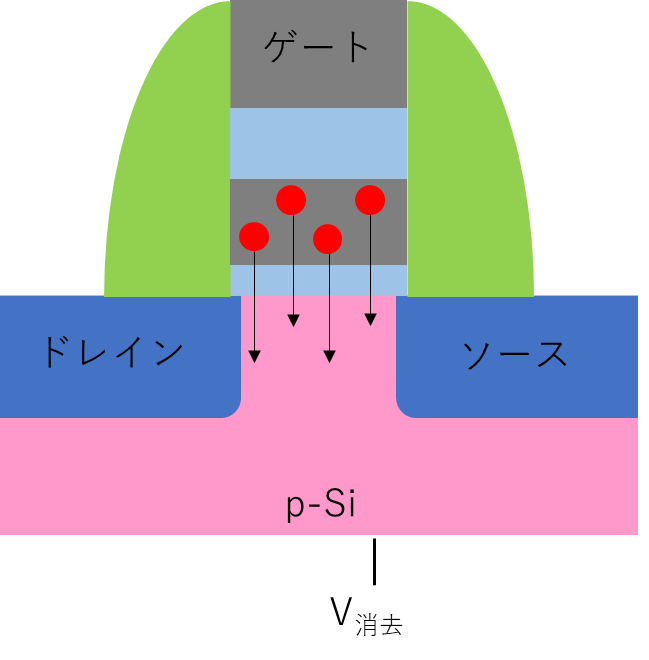

そうすると、FGから電子を引き抜くことができます。

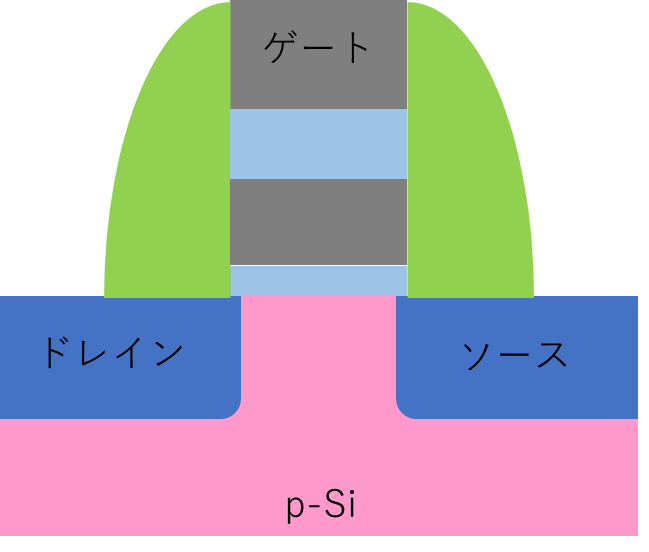

FGから電子を引き抜いてやると、書き込み前の状態に戻るというわけです。

個別のセルの消去は、このようにして行われます。ポイントは、FGから電子を抜くために、基板側に電圧をかけるところです。

NAND型の特徴

ここまで、二次元NANDフラッシュメモリの、動作原理を簡単に解説しました。

実は基本的な動作原理は、ネットで調べれば簡単に出てくるもんなんですよね。私が本当に書きたかったのはここからです。

NANDフラッシュメモリの大きな特徴は、ある程度の数のセルが直列に接続されていることです。

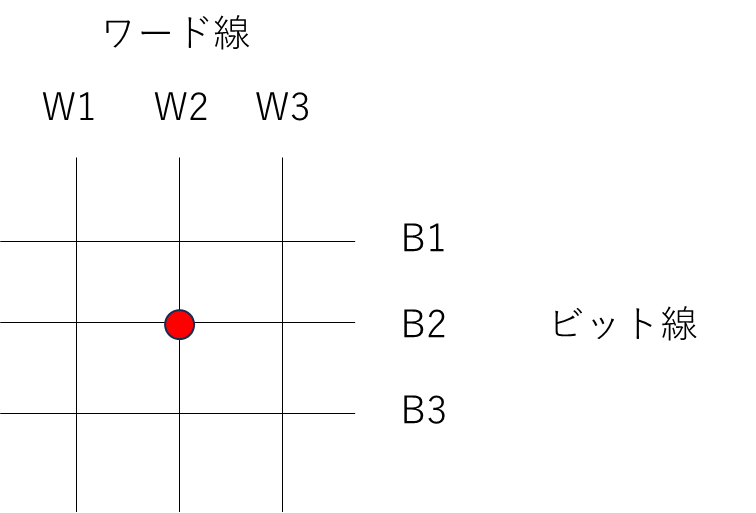

多くのメモリセルの中から、1つのセルを指定するためには、ワード線とビット線が使われます。イメージ的にはこんな感じです。

図の中では、簡単な解説のためにワード線とビット線が3本ずつある場合を考えています。この時、2つの線の交点がメモリセルです。例えば、図の中の赤い点の場所のセルを指定したい場合、ワード線はW2を、ビット線はB2を選べばいいわけです。

半導体メモリの中でも、DRAMやNOR型フラッシュメモリは、それぞれのセルに対してワード線とビット線が接続されています。それぞれのセルにワード線とビット線が接続されている場合は、セルの場所を指定したい時、必要なワード線とビット線を指定してやればそれで済みます。

しかし、NANDフラッシュメモリの場合はそう簡単にはいかないんですよ、という話です。

セルが直列接続

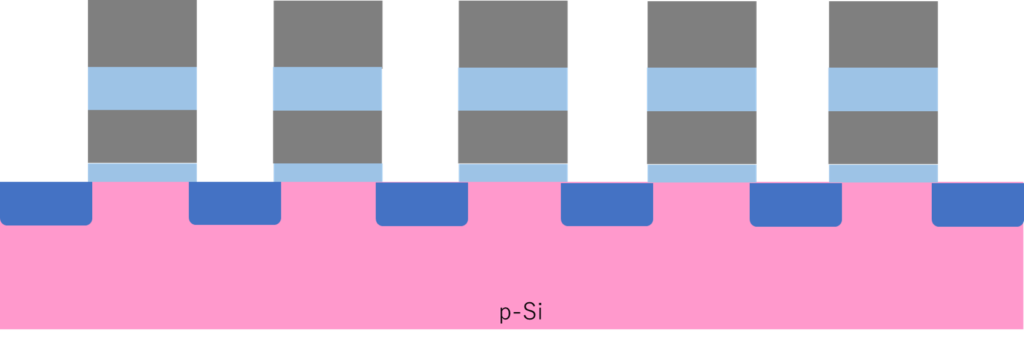

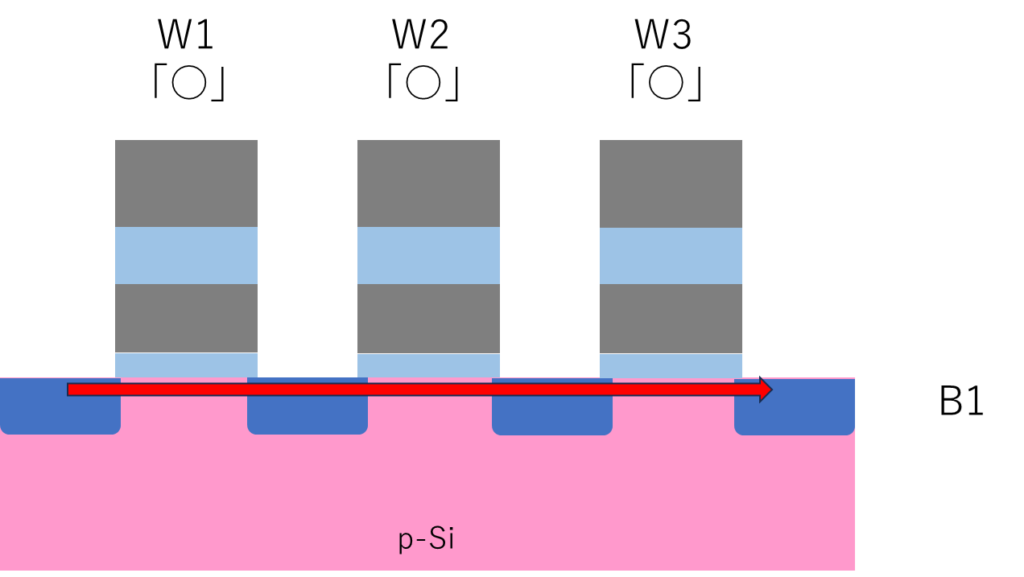

NANDフラッシュメモリの特徴は、各セルのソースとドレインが共有されていて、セルが直列でつながっています。横から見た図にすると、こんな感じです。

灰色の部分のゲートには、ワード線がつながっていて、ビット線はセルが直列につながることで導通するようになっていまっす。

この構造になっていても、書き込みや消去はそれほど問題にならないんですが、読み出しの時に問題が出てきます。

1つ1つのセルを読みだすには?

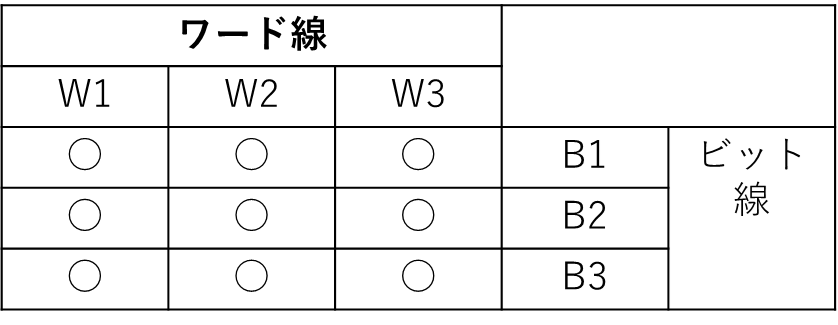

先ほどの、ワード線3本、ビット線3本の例を考えてみます。書き込みが行われていない場合、すべてのセルはFGに電子が注入されていない状態なので電流を通します。わかりやすさのために、FGに電子が注入されておらず電流が流れるセルを「○」、FGに電子が注入されて電流が流れないセルを「×」と書きます。

この状態であれば、すべてのセルに電流が流れるので、B1~B3のビット線に電流が流れて全てのセルが○であることがわかります。

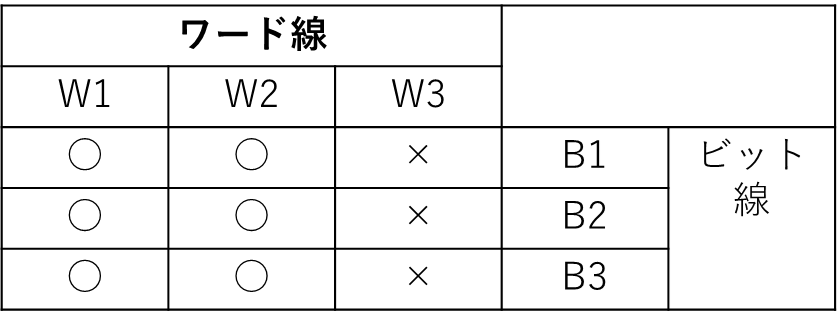

ここで、ワード線のW3のセルが全て×の状態を考えてみます。図にするとこのようになります。

各セルは、ビット線の列に対して直列に接続されています。つまり、同じビット線上にあるセルのうち、1つでもFGに電子が書き込まれてしまうと、書き込まれたセルがあるビット線は電流が流れなくなってしまいます。

図にすると、このようになります。

これだと、個別のセルのデータが0なのか1なにかを読み取ることができません。

この問題を解消するために、個別セルを読み出す時には一手間かけています。

まず、読み出したいセルがあるビット線を1つ選びます。(図中ではB2)次に、選んだビット線上の読み出したいセルのワード線(図中ではW2)を指定します。そして、読み出したいセル以外のワード線に電圧を掛けて強制的にセルに電流が流れるようにします。図にすると、こんな感じです。

読み出したいセルが赤い点で示したセルです。読み出したいセルがあるビット線(B2)上の他のセル(緑色の点)は、強制的にオンされた状態にして、赤い点が0なのか1なのかを読み取ります。

強制的にセルをオンにする方法は、ワード線に対してFGに電子が注入されない状態で、かつセルに電流は流せるような電圧を掛けてやります。

多値化する方法

さて、ここからは動作原理の解説というよりは、おまけです。動作原理の解説では、1セルあたりに0と1だけを書き込む場合を使いました。現代のNANDフラッシュでは、1つのセルに複数のビットを書き込む技術が使われています。

一般的には多値化と言われていて、1ビットを書き込む場合をSLC(SIngle Lebel Cell)、2ビットの場合をMLC(Multi Level Cell)、3ビットの場合をTLC(Triple Level Cell)、4ビットの場合をQLC(Quadruple Level Cell)と呼ばれます。

1つのセルあたりに書き込めるビット数が増えれば増えるほど、単位面積当たりの記憶容量は増えます。どんどん多値化していけば、記憶容量を増やせるように思えますが、そんなに簡単な話ではないんです。

多値化すると何が難しくなるのかを、SLCとMLCの場合で具体的に考えていきます。

SLCの場合

動作原理の解説で、セルのFGに電子を注入してデータを書き込むことを説明しました。物理的には、電子の注入を行っています。FGに電子を注入すると、電流が流れる状態だったセルに電流が流れなくなると書いたんですが、これはSLCの場合は正しいです。

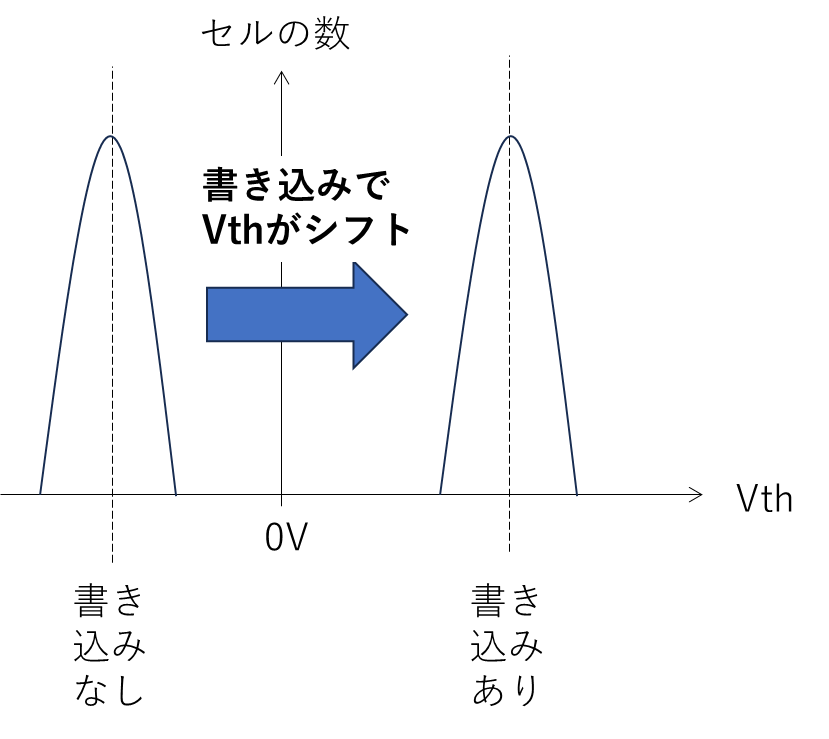

というのは、FGに電子を注入して動かしているのは、セルが電流を流し始める電圧なんです。(セルが電流を流し始める電圧のことを閾値(しきいち)電圧と呼びます。記号だとVth(ブイティーエイチ)が使われることが多いです。)

書き込みなしの場合と、書き込みありの場合でセルのVthが変わるのを模式的に示すと、このようになります。

そして、SLCの場合は0か1かを判別できればいいので、FGへの電子注入による書き込みでVthを上昇させることができれば、問題ありません。また、高い側のVthも1種類だけあればいいわけです。

MLC以上の場合

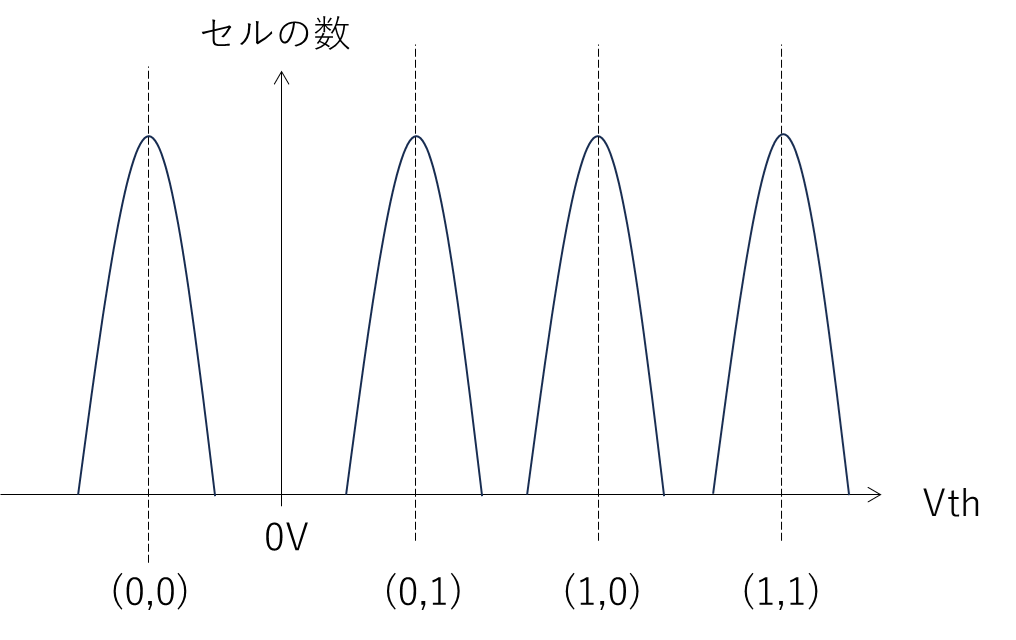

SLCと比較して、MLCの場合は少し話が変わってきます。MLCの場合は、1つのセルに対して2ビットの情報を書き込む必要があります。

1つのセルに2ビットの情報、つまり(0,0)(0,1)(1,0)(1,1)の4つのデータを書き込む必要が出てきます。そうすると、0V以下の場合も含めて、Vthを4つに分ける必要があります。

Vthを4つに分けるのは、模式的にはこのように書けます。

SLCの場合と比較して、書き込まなければいけないVthが増えたので、複雑になっていることがお分かりいただけると思います。

MLCだとVthは4つで良いですが、TLCだと8個、QLCだと16個のVthを制御しないといけないので、多値になればなるほどVth設定が難しくなります。

また、VthはFGに注入される電子の量で決まるので、注入される電子の量が少しずれただけで、別のVthだと認識される確率が上がります。

設定できるVthにも上限がありますし、書き込んだあとVthがずれてしまうと、データが破損してしまうので(もちろん修正するようなプログラムは入っていますが)、多値化だけに頼って記憶密度を上げるのは難しいです。

まとめ

この記事では、NANDフラッシュメモリの動作原理について、二次元NANDフラッシュの構造を例にとって基礎的な部分を解説しました。

図を多めにしたので、ある程度二次元NANDフラッシュメモリの動作原理については、理解していただけたのではないかと思います。内容でわからない部分があれば、コメント等でお知らせください。随時修正・追記していきます。

また、内容が間違っている部分がある場合も、ご連絡いただけると嬉しいです。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント