みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、三次元NANDフラッシュメモリの構造をついて簡単に解説します。

三次元NANDフラッシュメモリについて知るためには、二次元のNANDフラッシュメモリの動作原理を知っていることが前提になってきます。

過去記事で、二次元NANDフラッシュメモリの動作原理を解説しているので、こちらの記事を先に読んでいただけるとわかりやすいと思います。

3D NANDの構造

3D NANDフラッシュメモリの構造は、簡単に言うと2D NANDフラッシュメモリを縦にたくさん並べた形になっています。

2D NANDを縦にする

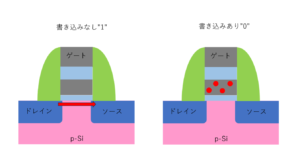

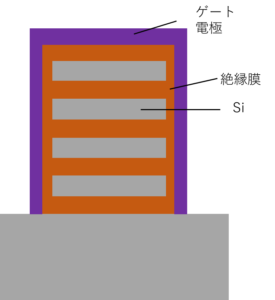

2D NANDを縦にするのは、図にするとこのようなイメージです。

単純に90°回転させると、このような見た目になります。とはいえ、単純に縦にした構造を作ることはできないので、少し工夫がいります。

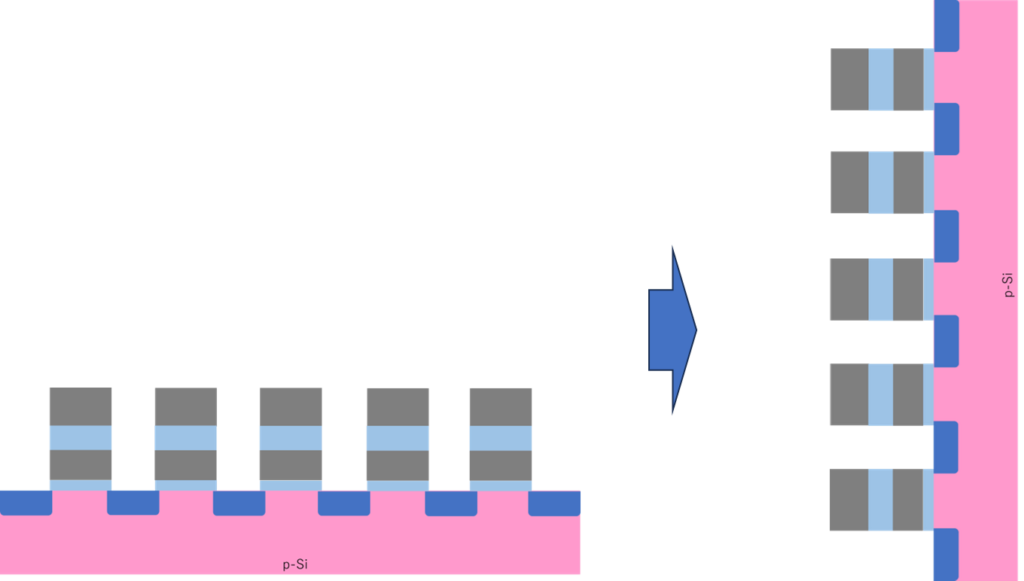

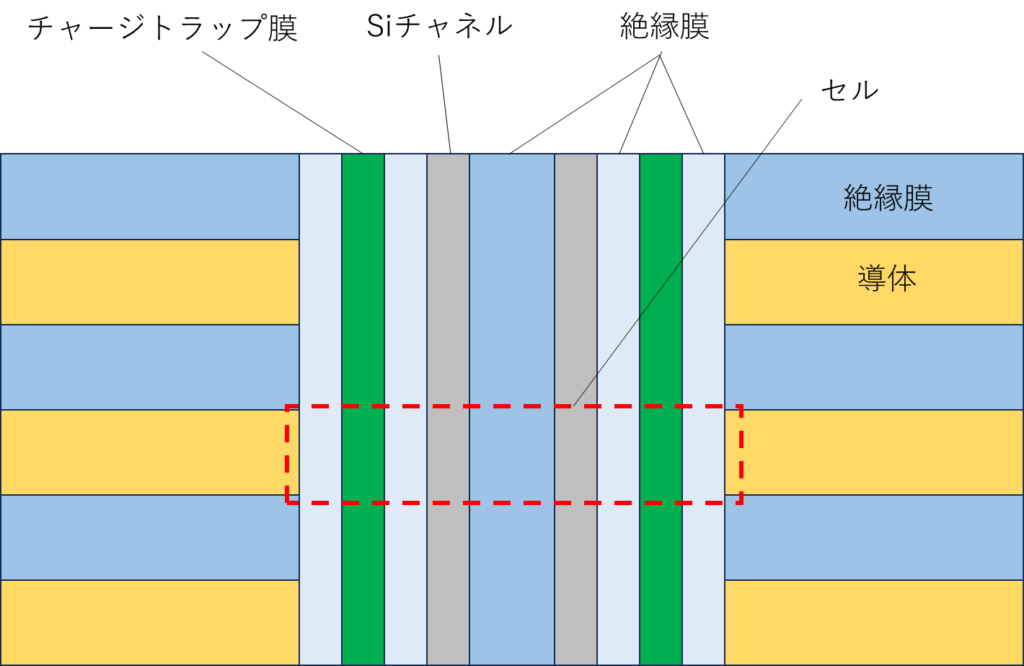

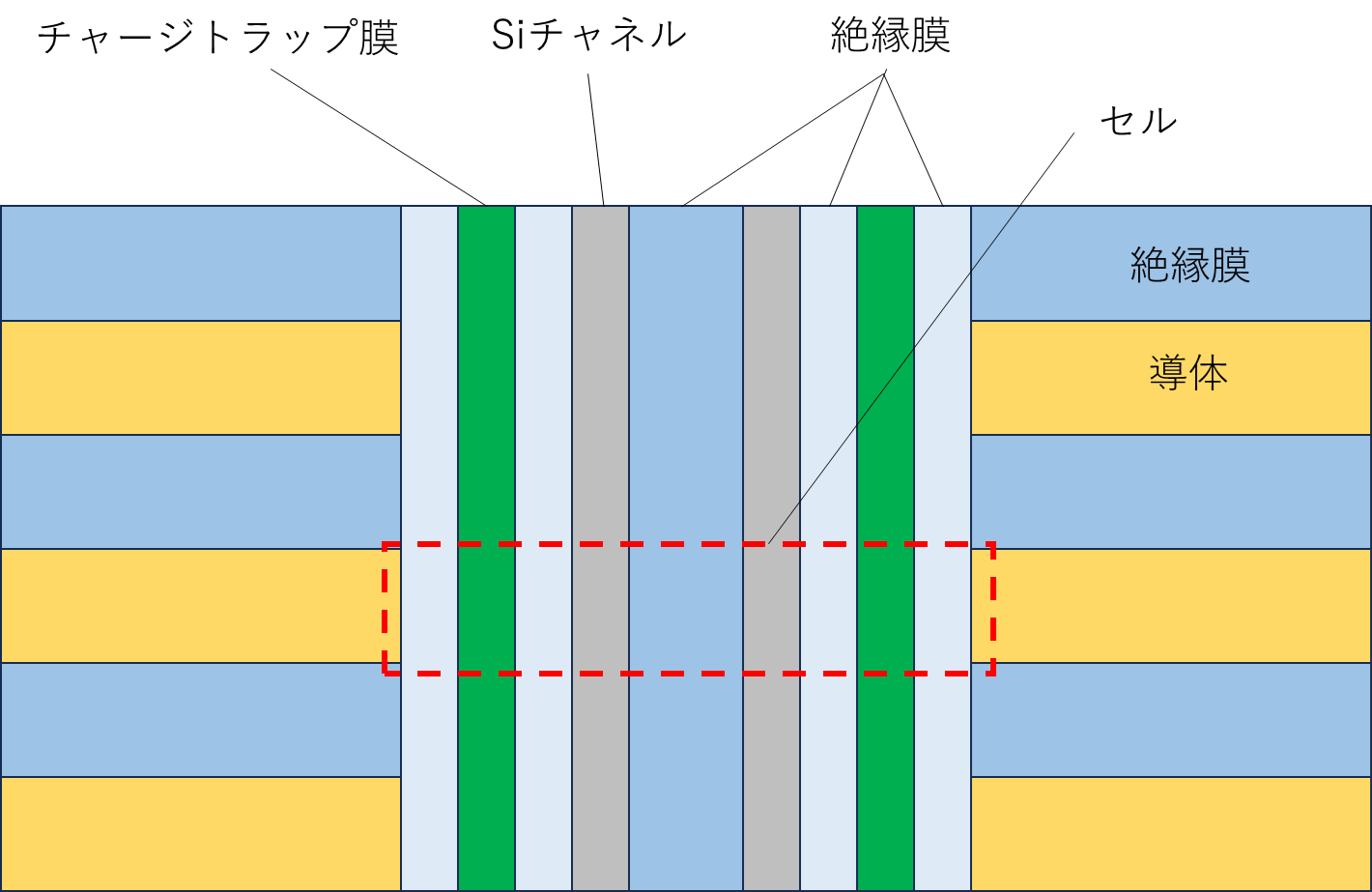

ではどんな構造になっているのかをセル部分の断面を模式的に書くと、このようになります。

赤い点線で囲った部分がセル領域です。

外側にある導体から電圧を印可することで、Siチャネル層と導体の間のチャージトラップ領域にチャージをトラップすることで、データを書き込みます。

これだけと言えば、これだけです。(細かいところはたくさんありますが、動作原理という意味で言うと、これで完結しています。)

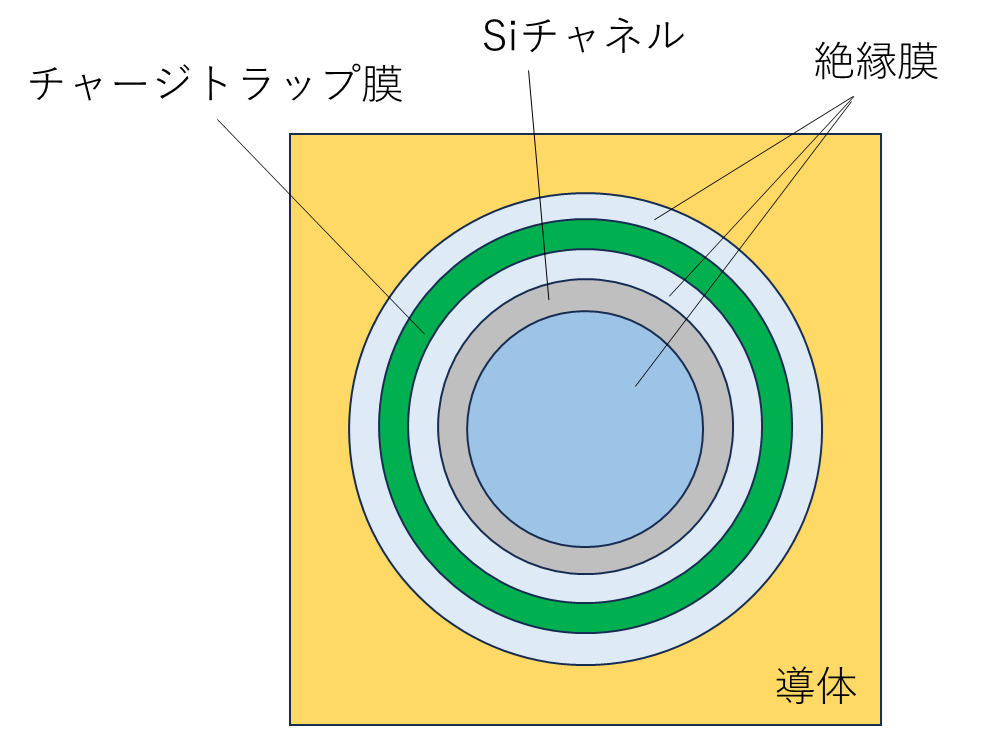

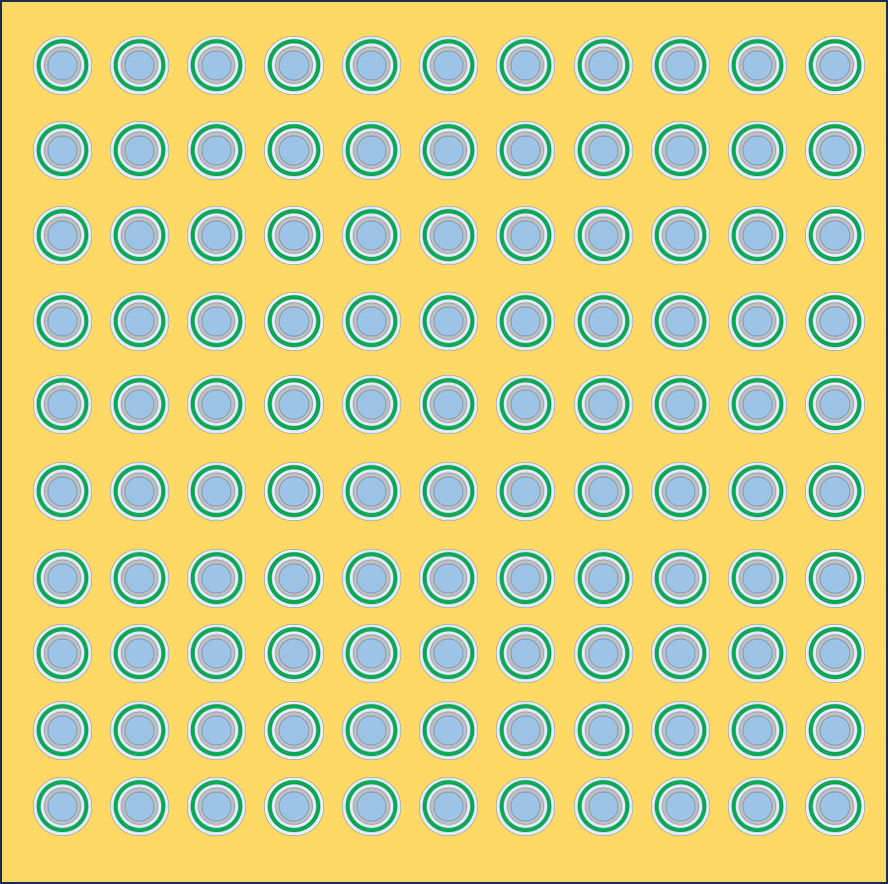

さて、セル領域を上から見て見ると、このようになっています。

円筒形のセル領域の外側には、導体の領域が広がっています。導体とSiチャネルから絶縁された状態に置かれた、チャージトラップ膜が輪状に形成されています。

2D NANDと違って、セルが輪状に形成されています。

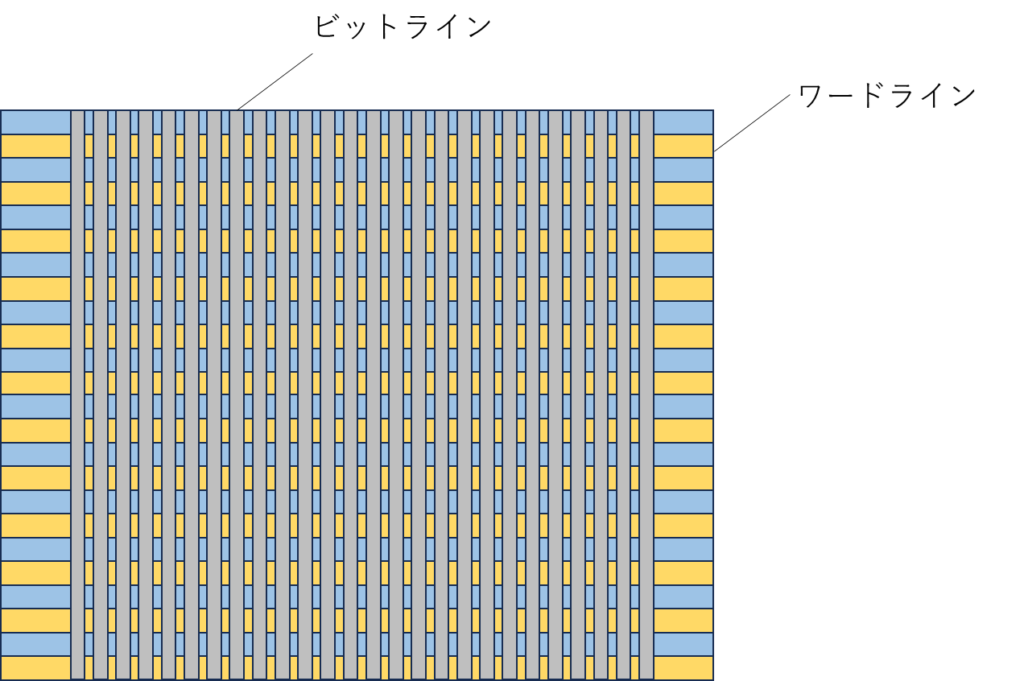

ワードラインは板、ビットラインは細い穴

NANDフラッシュメモリでは、ワードラインが各セルに接続されていて、ビットラインはセルが直列につながることで形成されていました。

3D NANDのセル部分は、Siチャネルがビットラインとなっており、導体がワードラインとなっています。

模式的にビットラインとワードラインの関係性を描きましたが、このようにビットラインとワードラインが交差する部分がセルとなっています。

このセル領域を上から見た図を模式的に描くと、このようになっています。(平面的な最密の構造でセルを埋めた方が効率がいいので、実際は最密構造の配置となっています。また、セル間の距離は詰めた方がビット密度は上がりますが、セル間の干渉が強くなるので、セル間距離の下限があり、セルが干渉せず最密になるようなギリギリの配置になっています。)

このように、セルが作られている部分は細い穴となっており、ビットラインは薄い板のような形をしています。

FGではなくCTが主流

2D NANDでは、セルで電荷を貯める場所はフローティングゲート(FG)でした。FGは、シリコンで作られていて、他のFGとは独立しています。他のセルのFGとは独立しているので、電荷が漏れにくいです。

3D NANDでは、FGではなくチャージトラップ膜(CT)が使われることが多いです。理由は単純で、FGを形成すると製造プロセスが複雑になるからです。(Intel/Micronは当初FGで3D NANDを製造していましたが、IntelはNAND事業から撤退し、Micronも途中からCT方式に転換しました。現在FG方式で3D NANDを作っているのは、元Intelの大連工場です。)

CTはFGと違って、各セルのCTが分離されているわけではありません。つまり、隣接セルとのチャージの干渉が起きやすいことを意味しています。

3D NANDは今後も積層数が増えていくことを考えると、製造プロセスが複雑になるFG方式を改めて導入する会社は無いのではないかと考えられますが、信頼性だけを考えるとFG方式の方が有利は有利です。

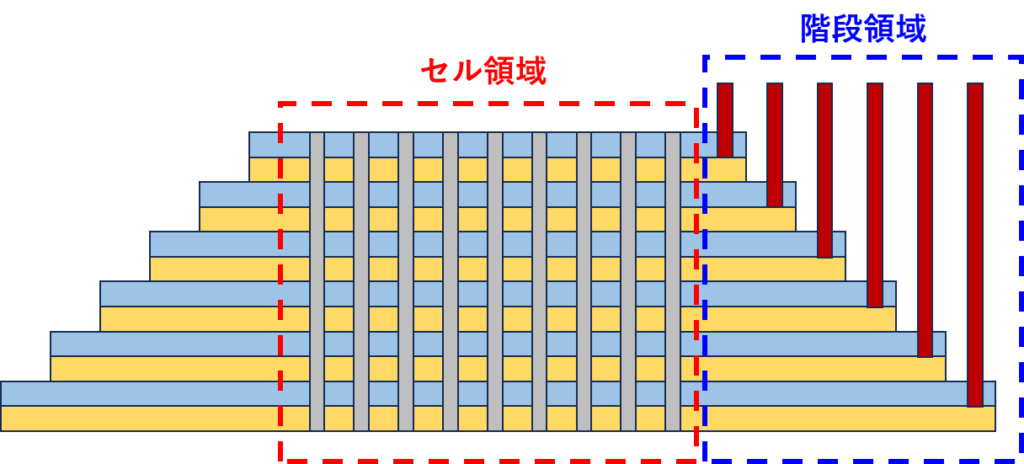

セル・階段・周辺回路が必要

ここまではセル領域だけについて書きましたが、NANDフラッシュメモリとして動作させるためには、セル以外にも作らないといけないものがあります。

大きく分けて、セル・階段・周辺回路が必要です。

セル領域はここまで説明した通りです。階段領域について模式的に図にすると、このようになります。

図では6層のワードラインですが、積層数が何層であったとしても各ワードラインに対して電気的に接続する必要があります。

6層描くだけでも手間だったんですが、実際のNANDフラッシュメモリの先端品では200層近い層数があり、各層にコンタクトを取る必要があるため、階段領域の面積もそれなりに必要になってきます。

階段部分のわかりやすい写真が、東芝レビューに載っていました。

そして、階段領域を作るのも手間ですが、さらに大変なのが周辺回路の領域です。

階段領域で各ワードラインに電気的に接続していますが、ワードラインをオンオフするためのスイッチが必要になります。つまり、ワードラインの数だけスイッチ(トランジスタ)が必要になります。

ワードラインの制御用のトランジスタを小さくできれば問題にならないんですが、NANDフラッシュメモリは原理上ある程度高い電圧を掛ける必要があります。高い電圧を扱う必要があるということは、ある程度ソースドレイン間の距離を取らないと、オフ時に電圧を止めることができません。

つまり、ワードライン制御用のトランジスタを小さくしようとしても、掛かる電圧(耐電圧)によって決まる物理的な限界があるということです。

積層数が増えるとどうなるのか

3D NANDフラッシュメモリは、各社が積層数を増やす方向で技術開発を進めています。

2024年時点だと、先端品の層数は300層近くなっています。積層数が増えてくると問題になるのが、メモリホールのエッチング、ワードラインへコンタクトを取る階段領域の面積、ワードラインを制御するトランジスタの面積です。

メモリホールのエッチングに関しては、ウエハの生産性に直接関わってきます。

例えば、ワードラインの導体と絶縁膜1層の厚さが30nmだったとすると、10層では300nmですが、100層だと3μmに達します。ミクロンオーダーの厚さのものに対して、数十nmオーダーの穴径で穴を形成する必要があるわけです。

積層数が増えると、メモリホールのエッチングの難易度は上がります。積層数が増えてくると、1度でメモリホールを形成するのが難しくなるので、2回か3回に分けてメモリホールをエッチングするようになっています。(Tier数でよく表されます。2Tierと書いてあったら、2回に分けてメモリホールをエッチングしているということです。)

メモリホールのエッチングは、東京エレクトロンのクライオエッチングが新しい技術として注目されています。

ワードラインへのコンタクトを取る階段領域の面積は、積層数が増えると単純に増えていきます。

構造を工夫することで面積を抑える方法もありますが、その分製造プロセスが複雑化します。NANDフラッシュメモリの構造上、ワードラインへのコンタクトができていないと動作しないので、動作に関してクリティカルな部分です。

ワードラインを制御するトランジスタの面積に関しても、積層数が増えると増えます。

この部分の面積を何とかするために、各社色々な方法を取っています。そもそも、2D NANDの時代はセル領域の横にワードラインを制御するトランジスタの領域がありました。

3D NANDになった当初は、セル領域の横にワードライン制御用のトランジスタが置かれていました。一方、積層数が増えてくると、セル領域の横にトランジスタを置こうとしても面積が足りなくなってしまいます。

そこで、セル領域の下部にワードライン制御用のトランジスタを置く方法が取られるようになりました。各社色々な名前を付けていますが、制御用の回路の上にセルを載せるという考え方は同じです。

キオクシア/WD以外の会社は、今のところ制御回路の上にセルを載せるプロセスで進めているようです。

キオクシア/WDだけは、最先端の第8世代(216層)でCBA方式を取っています。CBA方式は、セルと制御回路を別々のウエハに形成して、最後に2つのウエハを貼り合わせる方法です。

CBA方式のメリットは、セルと制御回路を別ウエハに作れるので、完成までの時間を縮めることができることと、制御回路とセルの両方に掛かる熱負荷の制約が減ることです。

NANDフラッシュメモリのセルはある程度熱負荷を掛けた方が性能は上がります。絶縁膜とSiチャネルから作られていることから考えて妥当です。

一方、制御回路のトランジスタは熱負荷を掛ければかけるほど性能が落ちます。理由は簡単で、トランジスタの性能を決めるうえで重要な不純物が、熱負荷によって拡散してしまうからです。

特に、高濃度拡散層の不純物が想定以上に拡散してしまうと、ソース・ドレイン間の実効的な距離が縮まってしまうことを意味するので、性能面では劣化します。

つまり、セルは熱負荷を上げたいが、トランジスタは熱負荷をできるだけ下げたいという矛盾した要求を同じウエハ上で実現するのは困難なわけです。

セルと制御回路を別ウエハに作ることができれば、この2つの矛盾する要求を同時に満たすことができるようになります。

CBA構造に関しては、セル性能と制御用トランジスタの熱負荷および面積の問題から、各社がどこかで導入すると考えられますが、どの時点で導入されるかは今のところわかりません。

まとめ

この記事では、3次元NANDフラッシュメモリの構造について簡単に解説しました。

ざっくりした書き方をしていますが、細かい部分は各社違いますし、二次元フラッシュメモリを縦にしていることがイメージできれば、そんなに難しくは無いと思います。(伝わってなかったらすいません。)

内容が間違っている部分がある場合も、ご連絡いただけると嬉しいです。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント