みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、半導体の物性評価で使われるホール効果測定について、簡単そうに見えて意外と奥が深いんですよということを書いていきます。

ホール効果測定の原理

ホール効果測定は、半導体の物性評価でよく使われる手法です。

シリコン基板を使う場合は、既に物性が調べつくされているので自分で測定することはほとんどないかもしれません。

ホール効果測定を行うことで、材料の「キャリア密度」と「移動度」を知ることができます。

有名な測定方法なので、検索すると原理はすぐ出てきます。Semi-journalさんのページがわかりやすかったです。

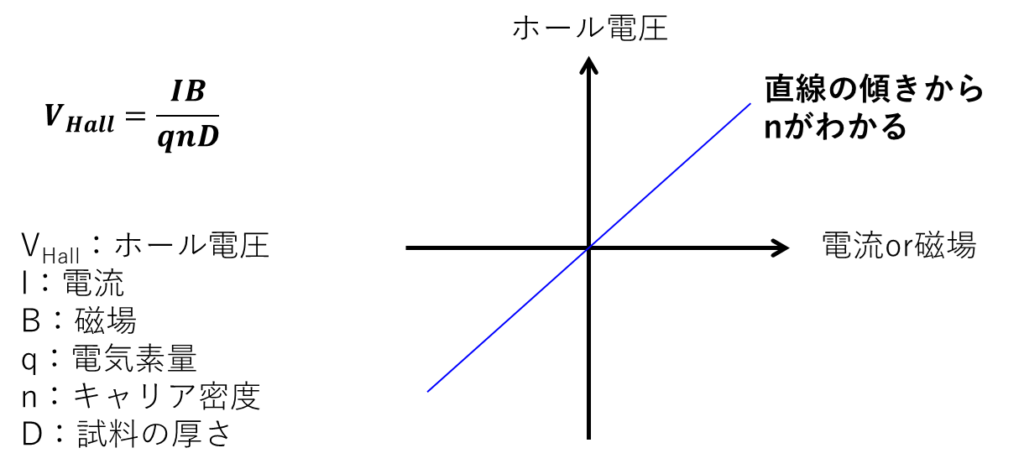

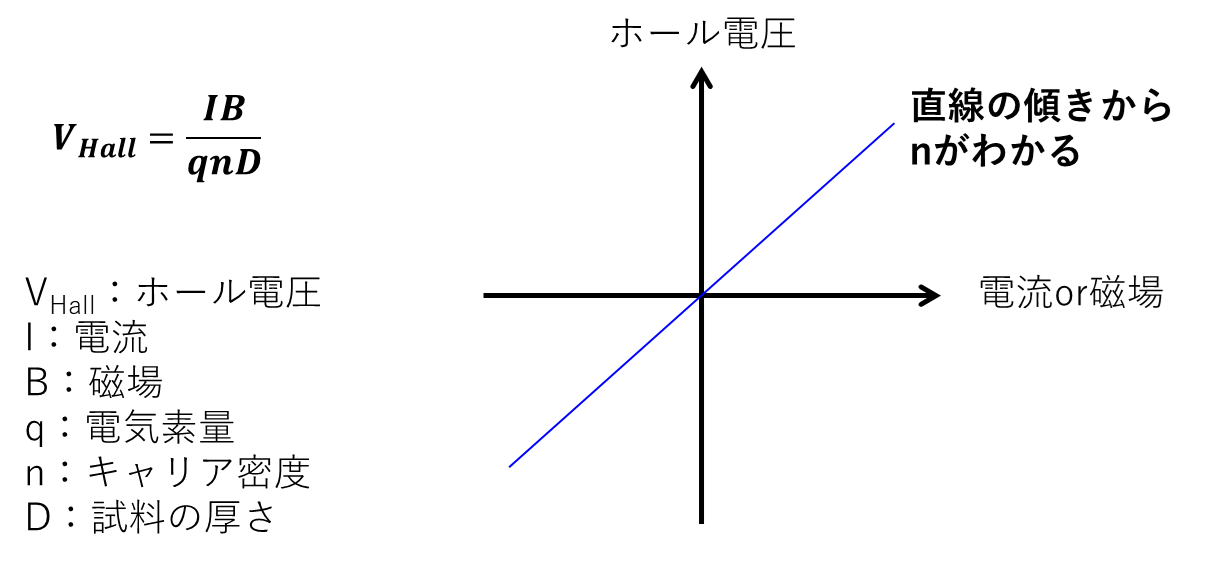

イメージ的にはこんな感じで測定します。

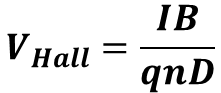

測定前の次点で電気素量(q)と試料の厚さ(D)は既にわかっているので、電流(I)または磁場(B)に対してホール電圧(VHall)を測定することで傾きを求めることができます。

この傾きはn(キャリア密度)の逆数に比例するので、傾きを求めることができればキャリア密度を求めることができるわけです。

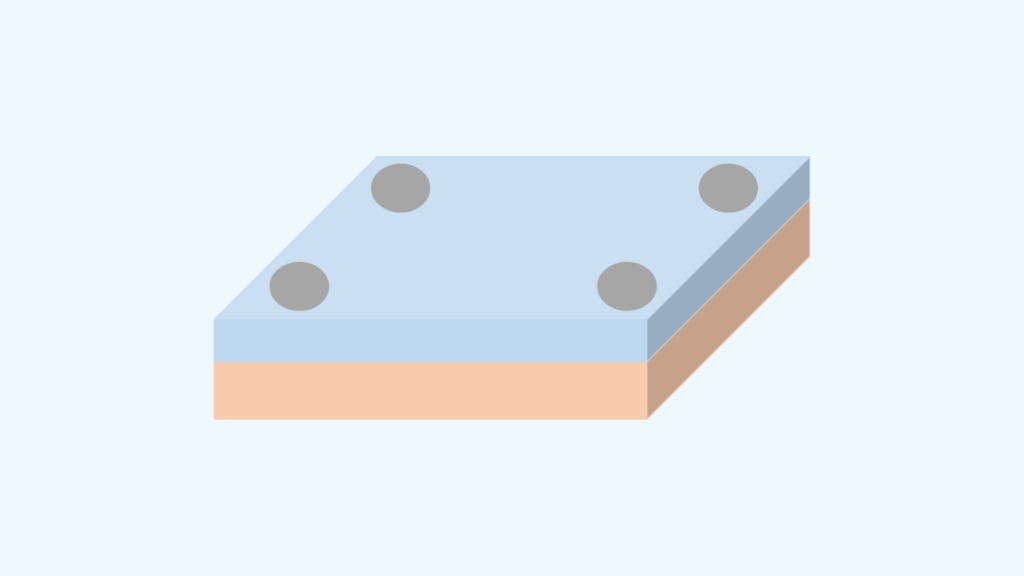

ホール測定は、大きく分けて2つあり「van der paul法」と「ホールバーを作る方法」があります。

van der paul法は、大きな基板を作れる場合に使われます。測定はこっちの方が簡単です。

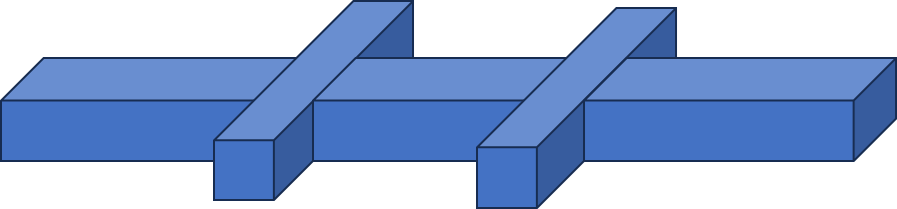

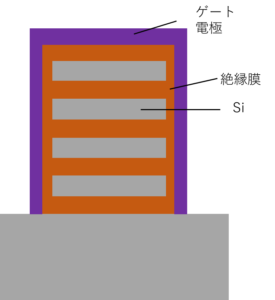

微小領域しか結晶が作れない場合には、ホールバーを作ります。ホールバーは、こんな形のものです。

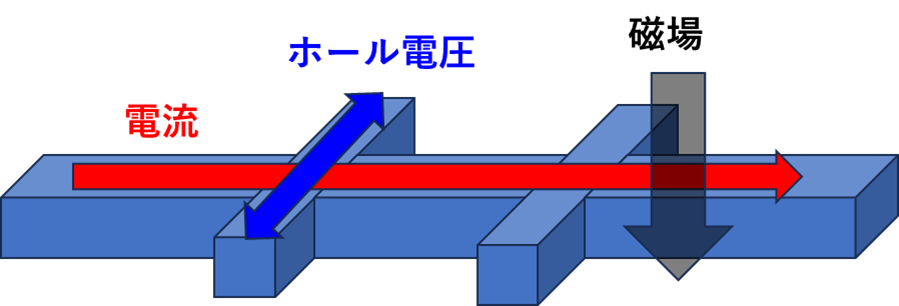

横方向に電流を流して、電流と垂直方向に発生するホール電圧を測定します。

このようにホール電圧を測定して、キャリア密度を求めたあと、ホールバーで抵抗値から抵抗率を求め、材料の移動度を出すことができます。

ちなみに、ホール電圧が発生する理由は、フレミングの左手の法則で説明されます。ローレンツ力が働いた結果として解釈することもできます。

ホール電圧の式に着目

さて、ホール測定の原理自体は簡単です。磁場を印可できる環境(極端な話、磁石があればいい)さえあれば、電流と電圧を測定することができれば、測定することができます。

半導体関連の研究室や企業であれば、テスタくらいはあるでしょう。

実際に測定することを考えるにあたって、もう一度ホール電圧の式を見てみます。

ホール電圧は電流と電圧に比例して、キャリア密度と試料の厚さに反比例します。

これを簡単に言い換えると、ホール電圧は電流と磁場は大きくなるほど大きくなり、キャリア密度と試料の厚さが小さくなるほど大きくなるということです。

実際の測定では、ホール電圧を大きく取りたいので磁場や電流はできるだけ大きく取るのが理想です。

電流に関しては、試料の厚さも関わってくるのでのちほど考えます。磁場の強さは、試料の形状に関係なく決めることができます。

磁場の強さは、テスラ(T)で表すことが多いです。(CGS単位系のGauss(G)で書かれていることも時々あります。1T=10000Gです。)

では永久磁石を使って磁場を印可する場合、どの程度の磁力までかけられるのかを考えると0.5T程度が限界です。(ネオジム磁石を使ってもこんなもんです。)

永久磁石の場合、磁力がついている方向(着磁方向)の長さを伸ばすと、ある程度までは磁力が強くなります。しかし、一定以上の長さになると伸ばしても磁力が飽和してきます。その限界が、だいたい0.5T程度です。

0.5T以上に磁力を強めようとすると、電磁石を使えばいいわけですが、1T近い磁力を持つ電磁石は非常に強力です。MRIに使われる電磁石でも1T程度の強さだと言われているので(もっと強いMRIもあるかもしれません)、そんな強さの電磁石が近くにある場合、磁性体は飛んでいきます。

ガスボンベでさえ、2点固定されていないと飛んでいくくらいの強さですから、結構危ないです。

というわけで、印可できる磁場の強さというのはある程度限られてきます。

次に流せる電流について考えてみます。実は、ある電圧をかけたときに流せる電流値というのは、測定する材料のキャリア密度と試料の厚さが決まってしまうと、ホールバーの形状で決まってしまいます。

例えば、薄膜シリコンに対してホールバーを形成して、キャリア密度を測定したい場合のことを考えてみます。(具体的には、SOI基板のSOI領域にホールバーを形成して、キャリア密度を測定するような場合です。)

シリコンは物性が調べつくされているので、PNの極性とキャリア密度が決まれば(厳密に言うとドーパントのイオン種も限定されますが)抵抗率を知ることができます。

キャリア密度と抵抗率の関係を表したグラフをIrvin曲線と言います。有名な図なので、半導体物性の教科書には必ず載っていると言ってもいいくらいです。

例えば、不純物密度(不純物濃度と書かれている場合もあります)が1016cm-3だとすると、抵抗率はP型は1.5Ωcm・N型は0.5Ωcm程度になります。(Irvin曲線という名前ですが、抵抗率と不純物密度はある程度比例します。しかし、不純物密度が増加すると移動度が下がるので、完全には比例せず少し曲がっている部分があります。故にIrvin「曲線」と呼ばれているわけです。)

抵抗率がわかったので、N型の場合ホールバーの形状が決まれば試料の抵抗値が決まります。

例えば、ホールバーで電流が流れる領域の幅が10μm、長さが100μmだとしましょう。試料の厚さは1μmだとします。

この時、試料の断面積は幅が10μm、厚さが1μmなので10μm2です。抵抗率が0.5Ωcmなので、長さも考えてやると、試料の抵抗値は50kΩとなります。50kΩに対して1V掛けた場合に流れる電流値は、20μAとなります。

では、試料に1V掛けて20μA流れる時に生じるホール電圧を求めてみましょう。磁場の強さは簡単のために、0.5Tとします。

計算過程は省略しますが、電流を20μA流した時に生じるホール電圧は6.25mVになります。ここでよく考えないといけないのが、電流を流すために両端に1Vかかった試料の中で生じるホール電圧がmVオーダーだということです。

例で出した形状のホールバーで、ホール電圧を測定しようとすると、両端に1Vかかった環境下で生じるmVオーダーの微小電圧が正確に測定できないといけないことを意味しています。

この程度だったら測れそうな感覚にはなりますが、測定系やノイズに気を付けないと、何を測っているのかわからない状態になる可能性はあります。(実際、電圧測定の分解能が低いと測れない可能性はあります。)

試料の厚さを厚くすると、ホール電圧がその分減ってしまうので、電流が流れる領域の幅を広くして長さを短くしてやれば、ある電圧に対して流れる電流量を増やすことができます。(要は、幅と長さを抵抗が減る方向にもっていってやればいいわけです。)

幅が広くて、長さを短くしたホールバーを作ることができれば、測定はそんなに難しくないんですが、このような工夫ができない場合、測定自体が大変になります。かつ、ホール測定をやる目的を考えると、もう一つ壁があります。

求めたいのはキャリア密度が低い領域

もう一つの壁というのは、ホール測定を行いたい場合、キャリア密度が低い領域を測定したい場合が多いことです。

シリコンの場合もそうなんですが、ホール測定では材料のキャリア密度と移動度がセットで測定されます。材料の移動度は、物性評価をするに当たって非常に重要な指標です。

以前、シリコンのバルク移動度について記事を書いたことがありましたが、バルク移動度は材料の特性を比較するために用いられるので、基礎的なデータです。

基礎的なデータであるが故に、シリコンは過去に基礎物性は調べつくされているので、現代では文献を見るだけで不純物密度に対する抵抗率と移動度の変化を知ることができます。

そして、シリコンの測定からも明らかなように、材料のバルク移動度は材料中のキャリア密度が低くなればなるほど上がります。つまり、根源的には材料の持っている移動度を知りたい場合、ドーピングされた不純物は限りなく少ない方がいいわけです。

一方で、キャリア密度が減ると、ホール電圧も上がりますが抵抗値も上がります。つまり、同じ電流値で生じるホール電圧はキャリア密度が小さくなるほど上がりますが、ホールバーの形状が同じであれば、同じ電圧をかけた時に流せる電流値が減少するということです。

つまり、キャリア密度が低い材料に対しては、流せる電流が限定されるので、小さい電流値で測定を行わないといけないという制約がついてきます。実はこれだけなら、そんなに問題ではないんですが、材料のキャリア密度が減るともう一つ問題が出てきます。

オーミックコンタクトが取れればいいが・・・

実は、ここまでの話は電極のコンタクト抵抗を無視して考えていました。

どういうことかと言うと、ホール測定を行う場合には電流を流す必要があります。この時、電流を流す領域の両端に電極を落としてやる必要があります。

電極は金属材料を使うことがほとんどなので、金属とホール測定したい材料(半導体です)の間には、接触抵抗が必ず発生します。接触抵抗が小さく、オーミックな電流ー電圧特性を示す場合をオーミック接合と言います。

オーミックではなく、整流性を持つ接合をショットキー接合と言います。

金属と半導体を接合すると、「金属の仕事関数と半導体のフェルミ準位の相対位置により、オーミック接合かショットキー接合かが決まります」と教科書には書かれています。金属の種類を変えてやれば、オーミックかショットキーかを変えられるなら話は早いのです。しかし現実はそうではありません。

半導体の種類によりますが、金属と半導体を接合するとある一定のエネルギー準位に半導体のフェルミ準位が固定されてしまう現象が起きます。(フェルミレベルピニングと言います。)

フェルミレベルピニングが形成されると、金属種によらず一方の極性にはショットキー接合が、もう一方の極性にはオーミック接合が形成されます。

実用的には、金属と半導体の接合部は、半導体の不純物濃度を高めてやることで、仮にショットキー接合が形成されたとしても、トンネル電流でコンタクトが取れるように作ります。シリコンと金属の化合物である、シリサイドを挟んだりする場合もあります。

測定の困難さ

ここからは、私がかつて測定していた材料で大変な目に遭った具体的な話になります。

学生時代、Ge系の材料を扱っていました。純Geは基板が作れるくらいの材料ですが、Ge系と書いているとおり、私が扱っていたのは純Geではありませんでした。(細かいことはここでは書きませんが、Geベースの材料です。)

Ge系の材料で比較的キャリア密度が低いものを測定しようとしていました。製法の関係で、ホールバーとして作れる領域の幅が数μm程度、試料の厚さが100~200nm程度だった記憶があります。

そして、Geはフェルミレベルピニングが強烈で、基本的にどんな金属を相手にしても、N型はショットキー接合をP型はオーミック接合となります。

また、Geは結晶中の点欠陥がアクセプタとしてふるまうので、意図的にドーピングしないとP型になることが知られていました。

最初は、P型のゲルマニウムに対してホール測定を行うつもりだったので、接合としてはオーミックになります。オーミック接合が取れると、比較的すんなりホール測定を行うことができます。

そう、ここまでは良かったんです。しかし、この後えらい目に遭いました。(私の知識が無かったせいもありますが。)

というのは、P型のGe系材料について、測定の再現性を確認するためにサンプルをもう一度作ったんですが、作ったサンプルに全然電流が流れてくれないんです。

全然電流が流れてくれないというのが曲者で、P型で最初に測定できたサンプルの1/10以下しか電流が流れなかったわけです。

最初は、サンプルを作り損ねたのかな?と思い、もう一度最初からサンプルを作り直しました。作り直したサンプルを測定してみましたが、やはり電流が想定の1/10以下しか流れませんでした。

おかしいなぁと思いつつ、2回サンプルを作って、2回とも同じような傾向が出たので、できたなりのサンプルでホール測定をやってみたわけです。

ただ、想定の1/10以下の電流値しか流れないので、ホール測定自体の難易度が上がりました。測定できるであろう電流値を探して、試行錯誤したうえで何とか測れたものがあって、キャリア密度自体は測れたんですが、極性を見るとN型を示していました。

ん?N型?俺はN形になるようなドーパントは混ぜてないぞ??どういうことだ??

測定した当時は、何が起こっているのかよくわからなかったんです。ですが、最初に測定できたサンプルがN型を示しているので、他のサンプルも測定してみると、全てN型を示していました。

こりゃあ、えらいことになったな・・・と思うと同時に、想定の1/10以下しか電流が流れなかった理由ははっきりしました。

Ge系材料と金属の接合は、必ずショットキー接合になるので、電流を流そうとしていた部分の電極と半導体界面にショットキー接合が形成され、コンタクト抵抗が非常に高くなってしまったことが原因です。

かつ、N型の不純物密度が低めだったので、ショットキー接合によって形成される空乏層領域の幅が長く、高抵抗となっていたわけです。

Ge材料の極性がN形になっていたということがわかったので、策を講じることで以後は意図的にドーピングしないものは基本的にP型を作ることができるようになったわけです。

ショットキー接合が形成されて高抵抗になると、なぜホール測定が難しくなるのかを簡単に書きます。

本記事で出した、シリコンのホールバーの例だと、1V掛けて20μA流れる想定でした。これが、ショットキー接合領域に電圧を食われて、1V掛けたのに1μAしか流れなかったとしましょう。(想定の1/20の電流値です。)

そうすると、生じるホール電圧は0.3125mVです。1μA流しても300μV程度しかホール電圧が生じないわけです。300μVという電圧値だけ見ると、測定できそうな気もしますが、一つ重要なポイントがあります。電流を流している端子の両端には1Vが印可されていることです。

電流印可端子の両端には1Vが掛った状態で、300μVの電圧差を測定することになるので、1Vに対する比率を考えると0.03%です。つまり、電流印可端子の電圧変動が0.03%起こっただけで、消し飛んでしまうくらいのホール電圧しか出ないわけです。

理論上はこれでも測定できるはずですが、実際の測定となるとノイズやら電圧変動やらを考えた場合に、なかなか安定して測定することが難しくなります。

図らずも、測定が難しいものを測っていたことになります。(ストーリー立ててなぜ難しかったのかに気づいたのは後からの話で、当時は全然測れないじゃん・・・と思いながら、延々とホール測定を行っていた記憶があります。)

このあとにもいくつか課題はありましたが、一番大きな壁はショットキー接合を形成する半導体に対してホール効果測定を行わなければならなかったことです。

この経験をあとから振り返って、重要だったなと思うことが3つあります。

・先入観や固定観念にとらわれずに事実を素直に見る

・目の前で起こっている現象を正確に言語化する必要がある

・繰り返すことには必ず原因があり原因を掴めないと事象の理解はできない

先入観や固定観念にとらわれず、実験事実を素直に見ることの重要さに関しては文字通りです。なまじ、1回目がP型として測定できてしまったが故に、材料はP型であると思い込んでしまったので、測定している材料がN型を示していることに気づくまでに時間がかかってしまいました。

P型であるという先入観を取り去っていれば、N型かもしれないという気付きを得られたかもしれないなと感じます。なかなか難しいですけどね。

次に、目の前で起こっている現象を正確に言語化する必要があることの重要性も感じました。当時は、言語化する力が足りていなかったので実験データに対して「想定より電流が流れていない」とか、「電流が流れない」というざっくりした表現を使っていました。

ちゃんと、「1V掛けても〇〇Aしか流れない」とか、「IV特性がオーミックにならない」とか、データを正確に表現する言葉を使っていたり、IV特性を測ったらこうなりました(図で示す)というような表現をしていれば、もう少し変わったかもしれません。

最後に、繰り返すことには必ず原因があり、原因を掴めないと事象の理解はできないという点です。これは、何かおかしいなと思った時に、原因を掴めなければ同じことを繰り返してしまうという意味合いです。

目の前の事象には必ず原因があるので、表面的な対症療法で止まるのではなく原因を探りにいくのが何をやるにしても重要なんだということを、あとから振り返って強く感じるところです。

ここまで、私がえらい目にあった話を書きましたが、もし仮にホール効果測定で困っている方が読んでくださってヒントにしてくださったら幸いです。

物性データがそろっているシリコンの偉大さ

最後に、Ge系の材料を測定した時に感じたシリコンの偉大さを書いておきます。

シリコンは、半導体デバイスの基幹材料として長年研究が行われてきた歴史があります。シリコンの基礎物性のデータは、古いものだと1950年代の実験が引用されている場合もあります。

50年以上にわたって半導体デバイスの基板材料として使われてきた歴史と、物性評価の積み上げがあるので、かなりの部分は先人が研究したデータが残っている状態になっています。要は、文献を探せば答えがだいたい見つかるということです。

これほど詳細に物性が調査されている物質が他にあるのだろうか、と感じるくらい文献はたくさんあります。そのおかげで、シリコンに関してはIrvin曲線を使って不純物密度と抵抗率の関係を見ることもできるわけです。(Irvin曲線に乗っているのは、Siの他にGeとGaAsがあります。)

自分でえらい目に遭いながらホール効果測定をしたことで、先人たちが築いた物性データの重要性が身にしみてわかりました。原理は簡単ですが、実際に測定することは奥深いものがあります。

現代に、今更シリコンウエハの移動度を測定する必要は無いですしやる人もほとんどいないと思いますが、やはり私たちが当たり前のように使っているシリコンや半導体デバイスも、先人たちの知見や技術の積み上げの上にあることを忘れてはいけないと強く感じました。

まとめ

この記事では、半導体の物性評価で使われるホール効果測定について、簡単そうに見えて意外と奥が深いんですよということについて、私自身の経験(ただの失敗談かな?)も含めて書きました。

原理は簡単ですが、まじめにホール測定をやる人も少ないと思うので、参考になったら幸いです。

記事の内容に明らかな間違いや、誤植、誤解を招く表現等がありましたら、コメントかお問い合わせフォームでご連絡いただけるとありがたいです。(基本的に、頂いたコメント等には全てお返事しております。)

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

2024/5/15に新しく本を出しました。興味があれば下記リンク先から見てみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント