みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、2024/7/10にWetern Digital(WD)から出ていた、The New Era of NANDの内容が興味深かったので、内容についてNANDの今後の方向性を踏まえて考えてみます。

The New Era of NANDの内容

もとの動画

The New Era of NANDの元の動画が、WDのIRサイトに公開されています。名前・メールアドレス・会社を入力すれば、無料で観ることができます。

https://investor.wdc.com/events/event-details/new-era-nand

最初に、The New Era of NANDのアナウンスがあった時には、スピンオフについて話があるのか?と思っていましたが、文字通りの内容でした。

WDが描いている3D NANDの方向性についての約1時間の講演です。

NANDの売上に対する投資比率が2Dと3Dで変わった

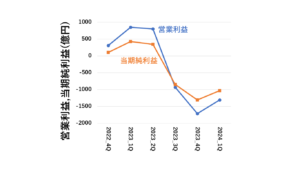

WDの主張としてまず出てくるのが、NANDで粗利が落ちているということです。

2012年から2018年の粗利の平均は19%だったのに対して、2019年から2023年は-5%と25%近く落ちています。特に、2019年以降に関しては平均の粗利がマイナスになっていて、端的に言うとNANDで儲かっていないということです。

これは、WDに限らず協業しているキオクシアでも同様の傾向がみられます。

粗利が落ちている理由として、2D NAND時代と比較して3D NAND時代の売上に対する投資額のデータが上げられています。

2D NAND時代(2015年以前)は、NAND業界全体の前工程に対する投資額が年間60億ドル程度の投資額だったものが2017年以降は年間170億ドルまで増加しています。

3D NAND時代の平均投資額は、2D NAND時代の約3倍に達しています。

3D化によるCapExの増加

NANDの3D化によるコスト増は、ビットコストの低減がなかなか進まないことを意味しています。

ビット当たりのコスト低減率と、売上に対する投資額比率を比べると、2D NAND時代は投資額が小さくてもビットコスト低減率が高かったですが、3D NANDはビットコスト低減率が低いのに、売上に対する投資比率は上がっています。

つまり、お金を掛けているのに、ビットコストは下がりにくくなっていることがわかります。

3D NANDのスケーリング手法

3D NANDのコストダウンのためのスケーリング手法は4つ挙げられています。

・Lateral

・Logical

・Vertical

・Architecture

Lateral

Lateralスケーリングは、単純に2D方向のシュリンクを図るものです。セルの2次元的な密度を上げていくことです。

やり方としては、2D NANDと同じなので、2次元的にセル密度が上がるので、チップ面積が同じであれば、セル密度が上がりますし、同じセル密度であればチップ面積を減らせるので、スケーリングには一番効果的です。

一方で、平面的なスケーリングによってセル同士の距離が近づくと、隣接セル間の干渉などが出てくるので、平面的なスケーリングには限度があります。

WD/キオクシアは、従来から平面的なスケーリングを積極的に採用しています。

Logical

Logicalスケーリングは、多値化です。

NANDフラッシュメモリは、一番最初は0と1の1ビットの情報を1セルに記憶するところが始まりでした。

0と1の1ビットの情報を1つのセルで記憶するのは、現代ではSLCと呼ばれています。

セルの閾値電圧を増やせれば、1セルで2ビットの情報を記憶することができます。(MLC)

このように、1セルあたりに記憶できる情報を増やしていけば、同じ構造の中で記憶容量を増やすことができます。現代では、TLC(3ビット/セル)、QLC(4ビット/セル)が使われています。

セルあたりの記憶ビット数を増やせれば、積層数を増やさないでも記憶容量を増やせます。ただ、多値化にも限界があるので、5ビット/セル、6ビット/セルにしていくのはなかなか難しいと考えられます。

Vertical

Verticalなスケーリングは、1セル層当たりの厚さを薄くしていくことで、スケーリングを図るものです。

例えば、1セルあたり50nmの厚さを使っていたものを、40nmにすることで、同じ高さで積層した場合に作ることができるセル数が増えるので(1.25倍)セルあたりのコストを下げることができます。

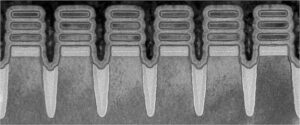

3D NANDは、1加工でエッチングできる深さでスタック数がきまるので、1セルあたりの厚さを薄くすることができれば、1加工で処理できるセル数が増えるのでコストダウンにつながります。

一方で、1セル層当たりの厚さを薄くしていくということは、1セルあたりの電荷保持層の厚みが減ることになるので、電荷保持の面から見ると不利になります。

コストだけ考えると、ギリギリまでセルの厚さを薄くしたほうがいいですが、性能とのトレードオフになるのでどこまで攻めるかは、各社の考え方によると思います。

Architecture

Architectureは、ちょっと変わり種で、メモリセルの周辺回路をどう置くか?ということです。

過去は、CNA(CMOS next to Array)でメモリセルの横に周辺回路がありました。次に、CUA(CMOS Under Array)としてメモリセルの下部に周辺回路を置く形にしました。

WD/キオクシアの最新世代であるBiCS8ではCBA(CMOS Bonded to Array)によるウエハ貼り合わせにより、セルとは別ウエハにCMOSが載っています。

CBAの次として、セルを別ウエハに作って、セル層を積層する図も出ていましたが、Architectureスケーリングの大枠としては周辺回路をどう置くかがターゲットです。

3D NANDのセルと周辺回路の構造をどう作るかは、一概にどれが良いとは言えないところです。

セルの面積的に、現代ではCNAは採用できないとしても、CUAがいいのかCBAがいいのかは、歩留まり・TAT・セルの熱負荷・CMOSの性能を考えないといけないので、各社判断が分かれているところです。

BiCS8の宣伝

最後の方は、BiCS8の宣伝がありました。CBAで218層積層により、I/O速度の向上を図りましたという内容です。

この辺は、キオクシアのページに日本語で詳しく書いてあるので、興味がある方は読んでみてください。

https://www.kioxia.com/ja-jp/rd/technology/topics/topics-66.html

今後の3D NANDの方向性

ここまで、WDのThe New Era of NANDの内容を簡単に紹介しました。

ここからは、The New Era of NANDの内容を踏まえて、今後の3D NANDの方向性を考えていきます。

WD/キオクシアは積層数競争から降りるのか?

私がまず感じたのは、WD/キオクシアは積極的に積層数競争をやらないという宣言なのではないか?ということです。

もちろん、積層数競争はある程度やるんでしょうが、一番大きなメッセージとしては、

「積層数を増やすだけではビットコストは下がらない」

ということに尽きると思いました。

また、今後の設備投資額は適正な比率を保ってあげ過ぎないことも、念頭にあるのではないかと感じます。

WDはNAND部門をスピンオフするので、NAND単体の企業として存続するためには、設備投資をある程度に抑えないと利益が出ないことは、2018年以降のWDのNAND部門の粗利率が物語っています。

積層数競争が供給過剰を引き起こす?

次に、積層数競争が供給過剰を引き起こす可能性について考えてみます。

これは、需要と供給がマッチするのか?というところに尽きると、私は考えています。

3D NANDの開発における積層数競争は、あくまでもNANDを供給するメーカー側の立ち位置です。とはいえ、これまで積層数競争を行っていた背景としては、積層数が増えるとビットコストがとりあえず減っていたからです。

2D NANDの時代から振り返ると、セルの微細化による容量増加によって、ビットコストが下がっていました。そうすると、消費者の立場から見れば、同じ容量のものは安く買えるようになり、同じ値段なら大容量のものが買えるようになっていました。

つまり、セルの微細化や積層数競争は、ビットコストが下がることが前提の技術開発競争だったと、私は考えています。

3D NANDは積層数を増やしてもビットコストが下がらないフェーズへ突入

しかし、3D NANDで積層数が200層を越えてくると、積層数を増やしてもビットコストが下がりにくいフェーズに入っていると私は考えています。

その理由は、3D NANDの積層数競争が、スタック(ティアと呼ばれることもあると思います)の積み重ねで実現されるようになったからです。

私の意図を、簡単に書きます。3D NANDの構造を簡略化すると、このようになります。(階段領域は面倒なので省いています。)

単純な積層数競争をしているときに、ウエハ上のセルの加工が問題になります。

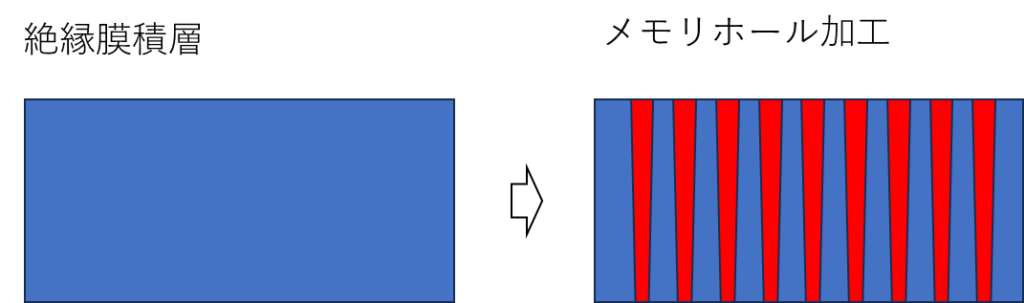

セルを加工するときに一番コストがかかっていると考えられるのは、絶縁膜を積層したあとにメモリホールをドライエッチングで形成する工程です。イメージ的にはこんな感じです。

赤い穴がメモリホールのイメージです。この時に、積み上げ層数を増やして一度に加工できる層数を増やしているうちは、ビットコストの低減につながります。

しかし、積層数を増やして一度に加工できる層数には限界があります。(TELのクライオエッチングを導入すると、現在よりは一括加工できる層数は増えると考えられますが、それでも1000層一括加工は無理でしょうから、そのうち限界がきます。)

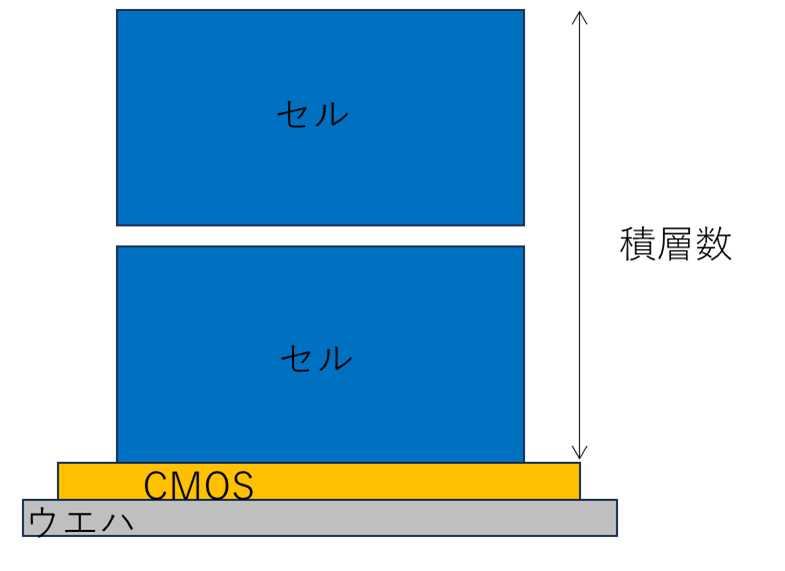

では、3D NANDの積層数競争はどのようになっているのかを考えて見ると、一括加工できる層数は限られているので、一括加工できる層数を1スタックとして、スタック数を増やすことで積層数競争をしています。こんなイメージです。

例えば、WD/キオクシアのBiCS8だと全体の積層数は218層ですが、128層弱が2スタックになっています。

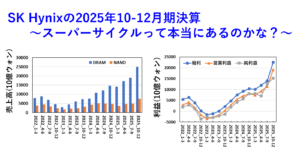

SK Hynixの321層品は、3スタックだと言われています。

つまり、1スタックで加工できる層数は増えていないので、結局ビットコストはほとんど下がっていないわけです。

もちろん、CMOSやウエハは同じウエハ上のものを使うことができるので、ウエハ2枚で作る場合よりコストは下がるかもしれませんが、積層数を増やしたとてビットコストの低減には必ずしもつながらない状況にあるといえます。

このことから、WDは積層数競争に走るのではなく、全体のバランスを見てビットコストが下がるような方向性を取りたいと考えているのではないかと、私は感じました。

協業相手のキオクシアはどう考えているのか

さて、WDが考えていることはわかったとして、協業しているキオクシアがどう考えているのかが、気になります。

キオクシアも、3D NANDは3000層積むことも可能だが、重要なのはバランスだという当時のCTOのインタビューが出ています。

https://xtech.nikkei.com/atcl/nxt/column/18/02127/00066

一方で、現在のCTOは積層数1000層に向けた道筋を語っています。

https://xtech.nikkei.com/atcl/nxt/column/18/00001/09089

個人的には、キオクシアが積層数競争に挑むのは得策ではないと感じますが、会社の方針としてどういう道を描くのかはよくわからないです。

また、WDが積層数競争ではビットコスト低減の道が無いと考えているのに、キオクシアは積層数競争で勝負したいと考えているとすると、なおさら相性が悪そうです。

協業で1社あたりの投資コストを下げることができるのは大きなメリットですが、会社ごとの考え方の違いが顕在化すると、方向性の決定に時間がかかります。

設備投資の自社負担を減らせる代わりに負っているリスクなので、協業スキームの中では仕方ないことですが、1社単独で投資決定を行っている会社ではまず起こりえない話です。

業界再編と寡占化の可能性

私個人としては、キオクシア/WD連合が積層数競争を追うのはあまりメリットは無いと感じていますが、仮に積層数競争を追うことになった場合のことを考えてみます。

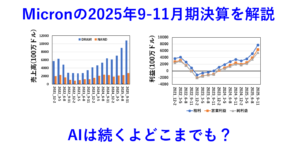

単純に考えると、3D NANDで積層数競争をしても、ビットコストが下がりにくくなっているので、このまま進めば「ビットコストが下がらない=時間が経ってもNANDの値段が下がらない」世界が来る可能性があります。

この世界が来るまでの過程で、(現在もそうかもしれませんが)メモリメーカーは2D NAND時代ほどの利益率を享受することができていません。

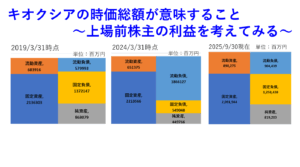

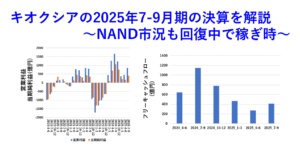

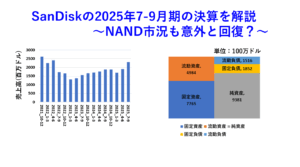

NAND専業であるキオクシアの業績を見れば、2019年以降を平均してみると、ほとんど儲かっていないことがよくわかります。

ビットコストが下がらないにもかかわらず、需要が減ると製造原価が高いのに製品の売価が下がるという、メーカーから見ると最悪な状況が起こります。

買い手に対して、ビットコストが下がらなくなった分を転嫁できればいいんですが、おそらく簡単な話ではないでしょう。30年近くNANDのビットコストは下がり続けてきたわけで、メモリの値段は下がる物だと思っている人の考え方を変えるのは容易ではありません。

投資競争の世界とも捉えらえる

また、積層数競争を続けるのであれば、それなりの設備投資を続けなければなりません。

しかし、3D NANDは投資額は増えるのに利益出にくくなっている状況です。

正直、WD(スピンオフ後)のNAND部門とキオクシア以外はDRAMの方が儲かっているので、NANDでの利益が小さくてもやっていくことはできます。

スピンオフ後のWDのNAND部門とキオクシアはNAND専業なので、NANDで利益が出せない=自社の利益が出ないことに直結します。

そんな中、積層数競争に追随するということは、投資余力のある競合他社に対して利益が出来くくなっているNANDの利益から投資を行わないといけないので、相対的に不利になっていると考えられます。

結果的に、積層数競争に追随するためにはそれ相応の設備投資が必要になるので、設備投資競争についていけるかどうかが、今後のキーになると考えています。

次回のメモリ不況で勝負が決まる

残念ながら、半導体メモリは好況と不況を繰り返すサイクルにあるので、そのうち次回のメモリ不況がやってくるでしょう。

この時に、ある程度勝負が決まるのではないかと考えています。NAND市場においては、DRAMがNAND以上に低収益にならない限り(長期的に見て)、DRAM・NANDを製造しているSamsung・SK Hynix・MicronがNANDの収益性を理由で撤退する可能性はほぼありません。

そうすると、NANDの利益率の低下の影響をもろに受けるのは、キオクシアとWDからスピンオフされるNAND部門です。

2社は、ウエハ製造で協業しているので、片方の会社が資金ショートするとドボンです。

と考えると、次にメモリ業界の再編が起こる可能性があるタイミングは、次回のNAND不況期にNAND専業の2社のキャッシュフローが、持つかどうかという点で決まります。キャッシュフローが持てば現状の5社体制が続きますし、持たなくなると5社体制から再編が起こると考えられます。

NAND市場の寡占化は避けられない

個人的にも、消費者としての意見としても、NAND市場の寡占化は起こってほしくないですが、現実的にはNANDのビットコストが下がりにくくなっていることを考えると、近い将来に寡占化が起こるのではないかと考えています。

どうしても、5社いる市場だとマーケットシェアが分散するので、価格は下がる方向になります。

大きく見ると、NANDのシェアはSamsung1社・キオクシア+WD・SK Hynix+Micronで同じくらいになっています。

NANDの利益率が下がる局面であれば、キオクシア+WDが経営統合を含めた形でシェアを増やしていかないと、ますます取り巻く環境が厳しくなっていくのは自明です。

キオクシアは、WDなのかMicronなのかSK Hynixなのかわかりませんが(Samsungはシェア的に無理)、どこかと組むor合併する形でないと、ビットコストが下がらない時代の3D NANDで競争していくのは厳しいというのが、私の考えです。

まとめ

この記事では、WDのThe New Era of NANDの内容から今後のNANDの方向性について考えてみました。

積層数競争をするだけでは、ビットコストは下がりませんよということが、わかりやすく伝えられていたので、WDのマーケティングは上手いなと感じました。

記事の内容に明らかな間違いや、誤植、誤解を招く表現等がありましたら、コメントかお問い合わせフォームでご連絡いただけるとありがたいです。(基本的に、頂いたコメント等には全てお返事しております。)

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント