みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、ロジック半導体の2nmプロセスの技術的な難しさを詳しく紹介していきます。

2nmプロセスについて、簡単に大枠を知りたい方はこちらの記事をご覧ください。

今回は、わかりやすさを重視した大枠の解説ではなく、半導体に詳しい方向けに2nmプロセスの技術的な難しさを紹介していきます。

始めに断っておきますが、この記事は半導体に詳しい方向けに書いているので、専門用語をガンガン使っていきます。

また、IBMの2nmプロセスのプロセスフローを見たわけではないので、公表されている資料と論文等の発表から想像した、筆者の想定であることをご承知おきください。

2nmプロセスの断面写真から考えられる技術的な難しさ

日本で2nmプロセスというと、新しく設立されたラピダスがIBMからプロセスの供与を受けて量産を目指しています。

ラピダス以外の会社で言うと、TSMC・Samsung・Intelが2nmプロセスに相当するノードを量産しようとしています。

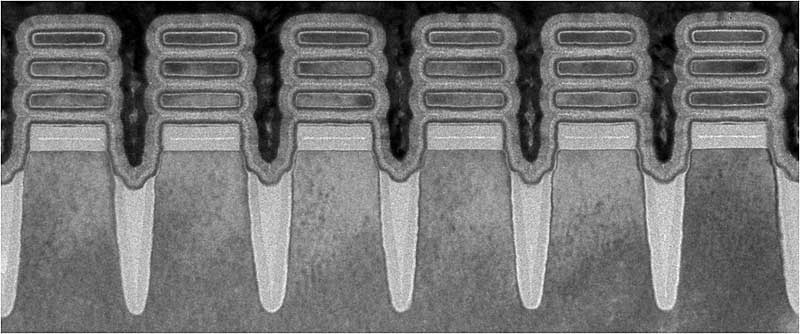

IBMが公表した2nmプロセスで作ったトランジスタの断面写真はこちらです。

IBMの公表資料から引用

この断面写真を見て、難しいだろうなと感じる部分を挙げると6個あります。

・ナノシートの成膜

・High-k絶縁膜の形成

・ゲート電極の形成

・ナノシート形成時のリプレイス

・チャネル/基板間のSiN層形成

・素子分離部分の形成および埋め込み

他にも難しいと思われるポイントはありますが、1つずつ解説していきます。

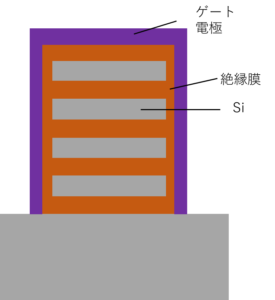

ナノシートの成膜

1つ目は、ナノシートの成膜です。

トランジスタのチャネル部分に相当するナノシートは、シリコンで作られていると考えられます。厚さは5~10nm程度でしょうか。(写真にスケールバーが無いので、ざっくりした数字です。)

チャネル部分のシリコンは、10~20nm程度の間隔を置いて積層されています。(写真の中では3層積まれています。)

おそらく、チャネルに使うSiとSiGe層をエピで積層して作っていると考えられます。チャネルとして使うSi部分を残して、SIGeの部分を後から抜いて、3層のSi層を作っていると思われます。

SiとSiGeを、10~20nmずつエピ成長して形成すること自体は、技術的には昔からあったものだと思いますが、ウエハ全体に均一な膜厚でSiとSiGeを積層するのはそれでも大変そうです。

Si上にSiGeを積層する場合は、それほどSiとGeの格子定数差が大きくないので、ヘテロエピする場合と比べればエピ成長させやすいですが、それでもチャネル部分に欠陥が入っていないのは技術力が高いことを示しているでしょう。

High-k絶縁膜の形成

2つ目は、High-k絶縁膜の形成です。

High-k絶縁膜は、SiO2より誘電率の高い材料を使った絶縁膜のことを指しますが、ロジック半導体でHigh-k絶縁膜というと、だいたいHfO2ベースの絶縁膜を指すことが多いです。

High-k絶縁膜自体は、プレーナー型のトランジスタの絶縁膜として導入されたので、歴史としては20年近くあります。

(たしか、IntelがHigh-k絶縁膜と金属ゲート電極を最初に導入したんじゃなかったかと思います。)

High-k絶縁膜以前は、SiO2やSiO2を窒化したSiONのような絶縁膜が一般的でした。SiO2の絶縁膜のメリットは、基板であるSiを熱酸化すればSiO2が形成できて、かつSiO2/Siの界面特性が非常に良いことです。

SiO2は基板であるSiを酸化すれば作ることができますが、High-k絶縁膜はSiの上に膜をわざわざ載せないといけないのが手間です。

2nmプロセスでは、チャネル部分の断面が長方形をしており、数nm~10nmレベルの間に絶縁膜を均一につける必要があります。絶縁膜の膜厚が均一でないと、ゲートに電圧をかけてもチャネルがオンする部分とオンしない部分ができてしまうので、膜厚の均一性は非常に重要です。

半導体プロセスでは、ALDが一般的に使われいてHigh-k絶縁膜もALDで成膜できるはずなので、おそらくALDで形成しているんでしょう。

ALDは原子1層レベルの膜厚調整ができるので、比較的膜厚の制御はしやすいとは思いますが、それでも大変そうに感じます。

また、High-k絶縁膜の部分をよく見ると、絶縁膜の中でも色が2種類に分かれています。おそらく、絶縁膜の組成を変えて2層に分けた(2層以上かもしれませんが)構造になっているようです。写真からでは組成はわかりませんが、相当なノウハウが詰まっているんでしょう。

ゲート電極の形成

3つ目は、ゲート電極の形成です。

ゲート電極は、色から見て金属材料でCVDかALDで付けられる金属を使っているんでしょうね。

一つの島と島の間隔が、数10nmしか空いていない領域に均一に金属を形成しないといけないのが難しいところです。

写真で見た感じ、少し金属が埋まっていない部分があるようにも感じられますが、ゲート電極は電流を通すわけではないので、空間が多少空いていても問題ないというコンセプトで作っているのかもしれません。

多少空間が空いているにしても、これだけ狭い空間に金属を形成するのは非常に大変だと思います。金属の種類や成膜条件にも、ノウハウがあるんでしょう。

ナノシート形成時のリプレイス

4つ目は、ナノシート形成時のリプレイスです。

写真の中に写っているわけではないですが、チャネル領域を間をあけて形成するときに、元々間にいた層を抜く工程が必要になります。

「抜く」のをリプレイスと言っているんですが、SiとSiGeがあった時に、SiはエッチングせずSiGeだけ抜いているわけです。

リプレイスの方法としては、薬液を使うウエットエッチングと、ガスを使うドライエッチングがあります。

どちらの方法でリプレイスしているのかは、作っている人しかわからないですが、Siの角が丸まっていないところを見ると、ドライエッチングでリプレイスしているのではないかと思っています。

ちょろっと論文を読んでみると、薬液を使ってリプレイスした場合、SiとSiGeで選択比を取ったとしても、どうしてもチャネルのSiの部分の角が丸まってしまうようです。しかし、ドライエッチングで条件を最適化すると、チャネル部分の角を保ったまま加工ができるそうです。

チャネル領域のSiの形が微妙に違うとなると、トランジスタとして動作するときに、オンした時の電流値が少しずつ変わってしまうことになるので厄介です。

ここにもノウハウが詰まっているんだと考えられます。

チャネル/基板間のSiN層形成

5つ目は、チャネルと基板の間に絶縁膜であるSiNが形成されていることです。

明確にSiNだと言われているわけではありませんんが、写真の色的にSiNでしょう。

チャネル領域と基板の間に厚めの絶縁膜を入れるメリットとしては、チャネルと基板の間の静電容量の低減でしょう。

静電容量は対向する基板の距離に反比例するので、チャネルと基板の距離が離れればそれだけ静電容量が小さくなるというわけです。

電気的な性能から考えると、チャネルと基板の距離は遠いに越したことがないわけですが、実際に構造を作るとなるとそう簡単にはいきません。

ナノシートの成膜の部分で触れましたが、チャネル領域のSiはエピ成長で作っているはずです。

絶縁膜上にSiやSiGeがエピ成長できるのかは、詳しくないのでわからないんですが、少なくともSi基板上にSiやSiGeをエピ成長することよりは難しくなるんじゃないかと思います。

SiN層を設けたうえで、チャネルのSiをどう作っているのかは謎なんですが、それだけ基板とチャネルの容量が効くようなスケールになってきているんでしょう。

チャネルと基板の間に絶縁膜を挟まないといけないという要求は、モノを作る方からするとハードルが上がっているように感じます。

素子分離部分の形成および埋め込み

6つ目は、素子分離部分の形成および埋め込みです。

素子分離部分と言っているのは、島と島と間に白い溝が入っているところのことです。

全てのトランジスタは基板上に作られていますが、それぞれのトランジスタを電気的に分離するために、素子分離は作られています。

素子分離の加工は、難易度が高そうです。開口が数10nmしかないところを200nm近く加工しているわけです。

また、素子分離の恐ろしいところは、加工だけでも難易度が高いのに、加工した溝の部分に絶縁膜を埋め込んでいるところです。

もはやこのサイズだったら、絶縁膜を埋め込まずにエアギャップにしてもいいんじゃなかろうかと思いましたが、おそらくプロセス上絶縁膜を埋め込まないと不都合があるんでしょう。

そして、埋め込まれている絶縁膜は、よく見ると3層構造になっています。基板側が白い絶縁膜で、灰色の絶縁膜になり、もう一度白くなっています。

おそらく、白い部分がSiO2で灰色の部分がSiNでしょう。

ただ絶縁膜を埋め込むだけでも大変だろうに、わざわざ膜種まで作り分けているわけです。素子分離の部分には、何かしらのノウハウがあるんでしょうね。そうでなければ、わざわざSiO2にSiNを挟んだ構造にはしないはずです。

High-k/Metal GateとFinFETを知り尽くしていないと作れない

ここまで、IBMの2nmプロセスで難しいと感じた場所を6個解説しました。

・ナノシートの成膜

・High-k絶縁膜の形成

・ゲート電極の形成

・ナノシート形成時のリプレイス

・チャネル/基板間のSiN層形成

・素子分離部分の形成および埋め込み

6個上げた点で、ナノシート構造のリプレイスは2nmプロセスで初めて出てきた課題です。しかし、他のことはプレーナー型トランジスタやFinFETを作っている会社であれば、ノウハウがあるものです。

例えば、High-k絶縁膜に関しては20年近く前に初めて導入されましたが、2nmプロセス以前のFinFETのプロセスでは当たり前のように使われています。素子分離や加工に関しても、FinFETを作った経験があれば、そこでのノウハウが流用できるでしょう。

やはり、断面写真を1枚見ただけでも、High-k Metal Gate技術やFinFETの加工などのノウハウが詰め込まれた、芸術作品のような見た目をしています。

断面写真から感じることとしては、2nmプロセス以前の製品を作り上げるためのノウハウを地道に積み上げていないと、製品を作るのは無理だということです。

High-k Metal GateやFinFETなどの、既に製品になっているロジック半導体を作るノウハウを持ったうえで、新しい課題を解決して初めて2nmプロセスは成り立つものだとしみじみ感じます。

ウエハ投入から完成までのプロセス数はいくつなんだろうか

最後に、ラピダスに限らず2nmプロセスを適用したロジック半導体を作るためにかかるプロセス数はどのくらいになるんだろうかという話です。

ロジック半導体に限らず、回路を作るうえではまっさらな基板に対して1つ1つ加工を行って、その積み上げで完成品を作っていきます。

2nmプロセスは、FinFETよりも格段に加工に手間がかかるようになっていますし、全体の工数も増えていると考えられます。半導体を製造するための装置は、数億円するものがザラにある世界なので、いったいどのくらいの投資が必要なのか想像もつきません。

研究開発にもお金がかかるし、量産するとなると莫大な投資が必要だとすると、最終製品の値段は確実に上がるでしょう。

とすると、2nmプロセスが使われる製品は、最終製品をお客さんが高い値段で買ってくれる用途に限定されてくるはずです。

最終製品を高い値段でお客さんが買ってくれる用途を考えてみると、サーバー向けの高性能CPU・ハイエンドPC・スマートフォンの最新製品くらいに限られるんじゃないかと思っています。

量産から時間が経って、値段が下がってくれば話は別かもしれませんが。

まとめ

今回の記事では、ロジック半導体の2nmプロセスの技術的な難しさを詳しく紹介しました。

半導体に詳しい方向けに書いたので、専門用語もたくさん入っていますが、2nmプロセスの技術的な要素を理解しようとすると、ただ半導体を知っているだけではなく、ロジック半導体を専門に研究開発している方や、していた方でないと読み解けないのかもしれないです。

わからない部分があったり、もう少し専門的に書いてほしいというご希望・ご意見がありましたら、コメント欄かお問い合わせフォームからご連絡いただけると幸いです。必ずお返事するようにいたします。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント

コメント一覧 (6件)

半導体初心者です。

2nmがなぜ難しいかの初心者向け解説記事を読みましたがとても分かり易ったです。

2nmでは裏面電源供給の技術が使用されるというのを聞いたのですが、なぜその技術が必要になったか等の経緯から仕組みまでの解説もよろしければほしいです。

おはぎさん。コメントありがとうございます。東急三崎口です。

配線の部分はあまり詳しくないんですが、裏面電源供給の技術を使うと配線の抵抗を下げられるメリットがあります。

トランジスタは電気回路の一部なので、1つ1つの素子に電気を通すための配線がつなげられています。

ただ、1つ1つの素子が小さくなると配線として割ける面積が減ります。

配線は金属で作られているので、比較的抵抗は小さいですが、配線に割ける面積が減ると配線の断面積が減って抵抗が上がってきます。

電源を供給する配線は、他の配線と比較してかかる電圧や電流が大きいので、配線の抵抗が増えると一番影響が出ます。

裏面から電源を供給できれば、他の配線との干渉を考える必要が無くなり、電源供給のための配線の断面積を大きく取ることができるということです。

裏面電源供給を使うメリットはざっくり言うと、こんな感じです。

メリットとデメリットを含めて、別途記事にしたいと思っています。今後ともよろしくお願いします。

はじめまして。

こんなブログが有るのかと、びっくりしました。

掲載のトレンチ構造のSEMの写真から感じた事ですが、2nm(20Å)プロセスとなると、積層ではリソ装置の重ね合わせ精度や解像度のコンディション維持やレジスト塗布装置精度や振動による露光干渉対策。エッチングでのトレンチ形成では深さやボーイング形状の管理に適したマスクエッチやトレンチ装置の管理は高難易度です。ゲート膜の清浄度、面均 埋め込みの管理。CVD成膜、エピ成膜では、面均、Rsでは温度、ガス、真空管理、圧力、チャンバーコンディションの管理。目視出来ないがインプラでのイオン注入でのRs面均ドーズ量の管理。裏面研磨後の薄ウエハー歪みによるセルクラック対策等、など、リソ、サーマル、メタル、インプラ、エッチング、エピ、CVD、裏面、全ての製造装置精度、コンディション管理が半導体の歩留りを左右する、管理するのは人でありスキルと経験が必要で、簡単では無い。ある装置内の1つ部品が不安定でも歩留まりに影響するのが、半導体です。10年、20年、安全に環境負荷を掛けず、アメリカ、中国、他国から干渉されずに利益を安定させる為にどう維持するのか?老朽化更新で金を掛けるのか?ファブレス、アウトソース?レンタル?成功事例は?半導体の設計の時点で確立する事も課題と思いますよ。先ずは80年代以降、日本の半導体が何故衰退したのか?原因を確認してからですね。どうすれば良かったのか? 技術とは関係無いが馬鹿らしくなる前に必須ですよ。何だか久しぶりで…長々とゴメンね。

隠居してゴメンねゴメンねさん。コメントありがとうございます。東急三崎口です。

半導体について書かれている記事は、あんまりないかもしれないですね。

ご指摘の通り、2nmプロセスで量産を実現しようとしたらリソ技術が非常に重要になってくると思います。

リソ以外でも、様々な工程の細かい部分(特に面均が大変だと思いますが)をケアしていかないといけないプロセスであることは間違いなさそうです。

技術的な難易度が高いこともさることながら、ラピダスが2nmプロセスの量産を行う時に一番クリティカルなのは、人材がいないことでしょう。

建屋を立てて、装置を並べることはお金をかければできますが、量産品の立ち上げを行って管理していく「人」がいなければ、絵にかいた餅です。

過去に日本の半導体が衰退した理由は諸説あって、はっきりした答えは無いと思いますが、ラピダスが同じ轍を踏まないようにしてほしいとは思います。

今後ともよろしくお願いいたします。

お疲れ様です。

2nmプロセスで量産を実現にはリソ技術ではオランダのASLMの様な極微細、重ね合わせに特化した露光装置がヒントで、スキルレスな先端装置作りが非常に重要になってくると思います。

半導体の装置は重故障でメーカーオンコールすれば現地にエンジニアが来て修理をしますが、ASLMにはフィールドエンジニアは来ません。オンコールで故障内容を確認すると装置ユニットを指定され、メーカーへ送らせユニットごとスワップ、入れ替え復元をする。現場も予めメントレを受ける。今までのキャノンやニコンには無い非常に合理的でしかも振動による重ね合わせズレしない夢の様な露光機。Arf、Krf、液浸レベルでは張り合えない…ニコン、キャノンは露光機を撤退するとまで…某OBエンジニアから聞いた時には、それはそれはショックで、老朽化と次世代パワトラ立ち上げと戦って疲れていた私の様な廃人は何とかもう少しだけ生産活動を延命処置をして、隠居する事にした。次世代半導体も今の回路設計や使う側からすればじゃじゃ馬的な特性であることから扱い難く選定されないのでSi品の様には売れない。次世代半導体にはアプリケーションも次世代回路技術やユーザーがいなければビジネスとして成立しない。 なので、ユーザー向けにアプリケーションまで考え、売れる物を作る覚悟が要る。

そう、ラピダスといえば、何故?北海道でやるのか根拠が判らない。

政府は夢でも見てるのか?と思う。

北海道に先端を支える協力会社や環境、インフラ、人材…無いでしょ…あるのは広大な自然のある土地で、半導体工場から出る酸.有機、排ガス、高周波ノイズ、様々な汚染や環境負荷は否めない。何も福島原発の教訓が生かされていない…と感じる。

色んな業界で国プロ、政府が絡むと上手く行かない。マイスター達は口を揃えるが、無駄、制約、忖度が原因と思える。結局ダメでも忖度が上手く改ざんするので頂上へ辿り着けない。プロジェクトは現場主導でも上のものは夜な夜な接待みたいな、変な能力者が有能な技術をダメにしてしまう。政府や税金は判り易いクリアーな案件

じやないと見積もりや想定時点でミスが起きる。成功事例じゃなく、経験や体験がないのと、権益目的が…風力発電みたいな、

20,30年安定維持してこそ成功です。 若者よ、この小さな半導体と関わるにはスキル以外に覚悟が要ると思います。

三崎口さま

お久しぶりです。

現在もラピダスで頑張っておられますでしょうか?先日、NHKスペシャルを見てこれ、大丈夫か?心配になってきました。小池社長の今回はGAAの動作確認とか言ってましたよね…

いや、初期ロット(魂のロット)と言うならば初期歩留まりの目標を持って有言実行でなければ国民の税金が無駄です。急がば回れと言う言葉があるように、成功事例や成功体験があればプロジェクト立ち上げも何とかなりますが、2ナノ事態実績がないでしょう。まして量産となると装置ラインナップの相関問題と複数台装置バラツキの合わせ込み、装置のコンディション管理など歩留まり直結する管理は人がしなければなりません。立ち上げに寝ずにやるとか、有り得ません。EUVの露光機、あれステッパーじゃなくて?2nmの重ね合わせ…無理でしょ、

また最初から大口径ウェーハでは平坦度や加工精度、面内均一性など8インチ、12インチ特有の問題が条件出しの阻害となります。先ず小口径ウェーハや2ナノじゃなく、拡大チップでの条件出しの確立をしておく方が、あとで微細化を特化としてやれる気がします。

色々ありますが、今回はここまで、書いときます。