みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、YMTCの特許に着目して、ウエハのボンディングが当たり前になったとすると、NANDフラッシュがどう変化していくのかを考えていきます。

特許の内容

今回着目した特許は、YMTCが日本で出願している公開番号「特開2023-160856」の特許です。(執筆日の2023/12/11時点では、公開はされていますが、特許が成立しているわけではありません。)

YMTCの特許を調べたきっかけは、Micronを特許侵害で訴えたという記事を見て、そういえばYMTCってどんな特許を出しているんだろう?と思ったことです。

3D NANDは、4社が技術開発で先行していた中、YMTCは後発として参入しているため、特許を取るのは大変なんじゃなかろうかと思っていました。

図面と本文に関しては、特許を検索して読んでください。(転載すると、著作権に引っかかりそうなので、本ページに図面は載せていません。)

ざっくりした特許の内容としては、ページバッファ・SRAM・周辺回路・コントローラーと3D NANDのチップがくっついた形になっていて、I/O速度・スループット・メモリ密度を改善できますよということになっています。

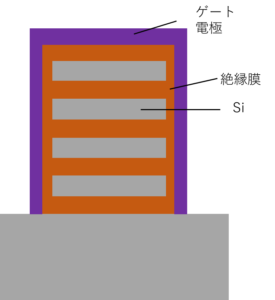

YMTCは、Xtacking技術を使って3D NANDを作っているので、NANDのメモリセルと制御回路を貼り合わせています。制御回路側に、SRAM・ページバッファ・周辺回路・コントローラーも載せてしまえという発想のようです。

Xtackingで得られるメリット・デメリット

YMTCはXtackingと呼んでいますが、2枚のウエハを貼り合わせてNANDフラッシュを作っています。

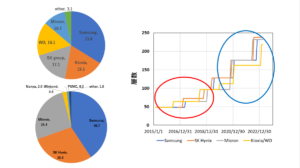

現状、YMTC以外で先端3D NANDでウエハを貼り合わせる方法を取っているのは、キオクシア/WD連合だけです。他の会社(Samsung、SK Hynix、Micron)は1枚のウエハでメモリを作っています。

貼り合わせを採用した場合に、デメリットとしてはコスト増になることが考えられます。1枚のウエハの歩留まりと、2枚を別々に作って貼り合わせるのと、どちらの方が歩留まりが良いのかはプロセス次第なので何とも言えないですが、同じ歩留まりで作れたとすると、ウエハ1枚で作る方がコストは安くなります。

貼り合わせを採用するメリットとしては、貼り合わせる2枚のウエハは別々に作ることができるので、納期を短くすることができます。単純に1/2にはならないと思いますが、1枚で完結する場合より納期を短くすることは可能でしょう。

YMTCの特許で、貼り合わせ構造にしたときのメリットとして挙げられていたことが2つあります。(他にもたくさん書いてあるんですが、目についたものを抜粋しています。)

1.制御回路側の熱負荷が減らせるため、CMOSに高度な論理プロセス(90~3nmプロセス)が使える

2.メモリアレイと制御回路を垂直に統合することで、チップ密度が向上できI/O速度が向上する

1については、次の章で詳しく書きますが、制御回路側のCMOSは、ロジック半導体として使われている90nm以降のプロセスは何でも積めるよということを言っているんだと思います。

2については、GPUにDRAMとしてHBMが使われることに似ている気がしました。要は、NANDとコントローラーとデータキャッシュを別々のチップに作ってつなげると、配線長が長くなりI/O速度を上げることが難しくなるので、配線長を短くしてかつ高密度につなげてやろうという発想なんだと思います。

制御回路側のウエハは何でも積める?

ここまで、YMTCの特許で私が着目したポイントを見てきました。

結構インパクトが強かったのは、制御回路側には90~3nmまでロジックの回路を積めますよという主張です。(本文中に、ちゃんと、「90nm、80nm、65nm、55nm、45nm、40nm、32nm、28nm、22nm、20nm、16nm、14nm、10nm、7nm、5nm、3nmなどのテクノロジーノード」って明記されてるんですよ。)(p10参照)

逆に言うと、制御回路の基板側は使うプロセスノードに合わせて熱負荷を調整してやればいいってことなんでしょうね。

具体的に出されたプロセスノードの中に、2nmが入っていないのは、量産されていないからなのかわかりませんが、使われる半導体基板には、Si・SiGe・Ge・GaAs・SOIなんかも例示されているので、広く書いてあるんでしょうね。

この特許が成立するかどうかはわかりませんが、少なくともYMTCは制御回路側の基板にロジックで使われている高速CMOSを使ってやろうという考えがあることがうかがえます。(じゃなきゃ、こんなにたくさんプロセスノードを例示しないと思いいました。)

米国の輸出規制があるので、3nmプロセスのチップをどうやって手に入れられるのかは置いておいて、7nmプロセスまでなら、SMICが作っているので中国国内で手に入れられることを考えると、FinFETのある程度のプロセスまではやろうと思えば積める環境にはあるんだと思います。

もちろん、3D NANDの制御回路側の基板はロジック半導体を作れればいいわけではないので、それなりに技術開発は必要なんでしょうけど、個別の要素技術を持っていれば、YMTCがロジック半導体が載ったNANDを作るのは時間の問題なのではないかと感じました。

一つ不思議に感じたのが、なぜ90nm以降のプロセスが例示されているのかということです。90nmの一つ前のプロセスノードは、130nmでだいたい20年前くらいの先端ロジックです。もしかしたら、YMTCは現状130nmくらいのプロセスノードを使っているのかもしれないですね。

他社の特許を少し見てみる

YMTCの特許について、みてきました。3DNANDとSRAMを垂直統合するというアイデアが非常に面白いと思ったので、他のNANDメーカーで似たような特許が無いか探してみました。特許の検索は無限にできますが、今回は「会社名+SRAM」で調べています。

メモリメーカー+Intel+TSMCを見てみました。

Samsung

意外と、NANDとSRAMを垂直に統合する形の特許は見当たりませんでした。まだ公開されていないだけかもしれませんが、DRAMのHBMとSRAMを組み合わせたような特許は見つかったので、HBMの方にフォーカスしているのかもしれません。

SK Hynix

SK Hynixも見つけられませんでした。3D NANDの特許はたくさんでてくるんですが、意外とNAND+SRAMの特許はなさそうです。

Micron

MicronもNANDとSRAMに関しては、見当たりませんでした。Phase Change Memory(Intel-Micronが出していた3D Xpointで使われていたと言われているものです。)とSRAMを組み合わせたような特許は見つかったので、別の機会に見てみようと思います。

Western Digital

Western Digitalに関しては、全く出てきませんでした。SSDに関連した特許はたくさん出されている印象ですが、SRAM等は特許出してないのかもしれないですね。

キオクシア

キオクシアに関しても、見つかりませんでした。メモリメーカーは、NANDとSRAMってあまり融合しようというイメージは無いのかもしれないですね。

Intel

Intelは、今ではNANDからは撤退してしまいましたが、かつてNANDを扱っており、かつ先端ロジック半導体のメーカーでもあるので少し期待しながら探しました。特許として成立しているわけではありませんが、似たようなコンセプトの特許が1件ありました。公開番号「特開2022-100222」です。

コンセプトとしては、不揮発性メモリの読み書きを高速化するために、不揮発性メモリと同ダイに形成した内部バッファを用いるものです。内部バッファの例として、SRAMが記載されています。不揮発性メモリとしては、NANDフラッシュが書かれていますが、同時に3D XPも例示されています。

Intelが3D XPをやっていた頃に、NANDも含めたSSDの高速化のために、出した特許だと考えています。

SRAMと不揮発性メモリの統合という意味では、YMTCの特許に近い考え方があるように感じました。

TSMC

TSMCは、メモリメーカーではありませんが、もしかしたらSRAMとNANDの融合のような特許が出されているかもしれないと思って探しましたが、案の定出てきませんでした。SRAM単独の特許は出ていましたが、さすがにNANDとくっつけるような特許はありませんでした。

TSMCはNANDやDRAMは本業ではないので、出していないのかもしれないです。

各社が貼り合わせに移行するとNANDの高速化競争が始まるのではないかと予測

YMTCの特許をベースに、メモリメーカー、Intel、TSMCに類似特許が無いか探してみました。

Intelの特許が唯一、似たようなコンセプトのものでしたが、他の会社はあまりSRAMとNANDの融合に関しては特許は出していないようです。(私が調査できていないだけかもしれませんが。)

YMTCの特許を見て少し感じたのは、3D NANDの技術革新がもしかしたら高速化に向かうかもしれないということです。

というのは、YMTCの特許にも書いてあるとおり、制御回路が載っている基板を貼り合わせて作ることができれば、ロジック半導体で使われているプロセスを流用することができます。

NANDのチップを作るときの熱負荷がどの程度かはわかりませんが、少なくともロジック半導体よりは熱負荷が高い工程を経ているのは間違いないでしょう。

とすると、YMTCとキオクシア/WD連合は、貼り合わせプロセスに移行していますが、他社はまだ1枚のウエハでメモリを作っています。そのうち、積層数が増えるとどこかで、各社が貼り合わせプロセスに移行する時期が来ると考えられます。

各社が足並みをそろえて移行するのか、世代が分かれるのかは、各社のコストおよび歩留まりを考えたうえでの判断になると思いますが、多分10年後は貼り合わせプロセスに移行するのではないかと思います。(積層数が増えるほど、各レイヤから配線を引き出すのに必要な面積が増えるので。)

各社が貼り合わせプロセスに移行した段階で、制御回路にはロジック半導体のプロセスを載せられるようになるわけです。そうすると、3D NANDの方向性は2つに分かれると思っています。

・とにかく大容量を目指して容量当たりの単価低減を目指す

・NANDの容量を持ちながら、ある程度高速動作するメモリの用途を開拓する

前者は従来通りのNANDメモリの方向性で、後者はDRAMの中のHBMのような方向性ではないかと思っています。

後者の市場があるかそもそもわかりませんが、もしあるとしたら、高速動作するNANDの世界を切り開いていくのは、ロジック・DRAM・NANDを全て手掛けているSamsungになるような気がします。

まとめ

この記事では、YMTCの特許に着目して、ウエハのボンディングが当たり前になったとすると、NANDフラッシュがどう変化していくのかを考えてきました。

未来のことを正確に予測することは不可能ですが、少なくともYMTCが制御回路側の基板にロジックCMOSを載せる気満々なことは、はっきりとわかります。

記事内での、明らかな間違い・誤記・認識違い等があれば、教えていただければ、事実確認のうえ修正いたします。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント