みなさんこんにちは、このブログを書いている東急三崎口です。

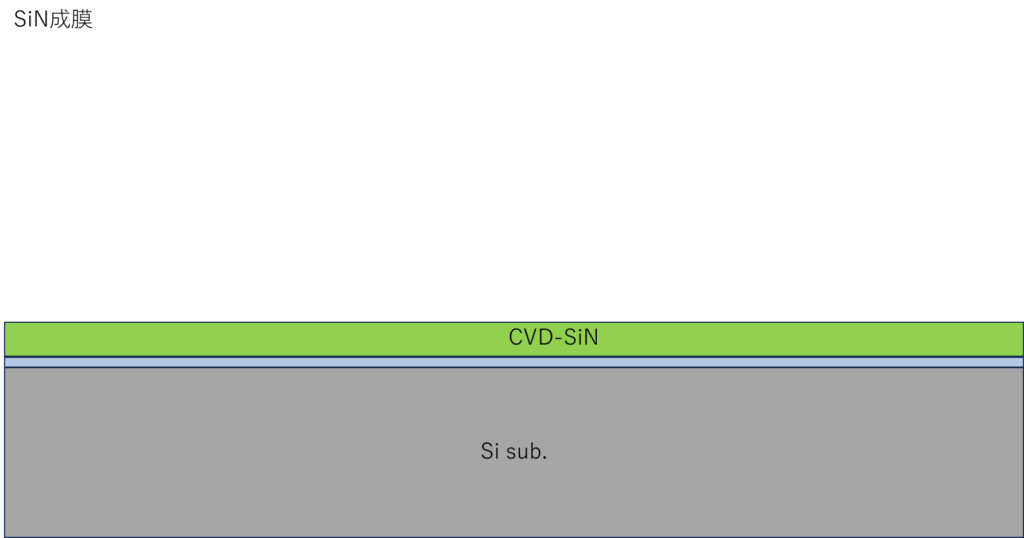

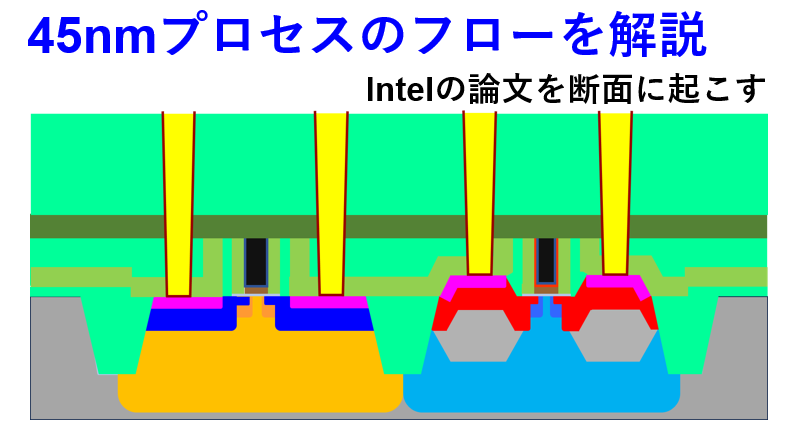

この記事では、ロジック半導体の45nmプロセスのフローを断面に起こして解説します。

45nmプロセスは、2007年当時の最先端ロジックプロセスで15年くらい前のプロセスです。

現代では、レガシーと呼ばれるような世代ですが、現代の先端ロジック半導体につながるような技術が多く使われているので今回取り上げています。

非常に長いですが、お付き合いいただけると嬉しいです。(図面は約90枚載せていて、文字数は15000字程度あるので非常に長くなってしまいましたが、それなりの内容なので、興味があるからは最後まで読んでいただけると幸いです。)

180nmプロセスの断面は別記事で解説しているので、興味があれば読んでみてください。

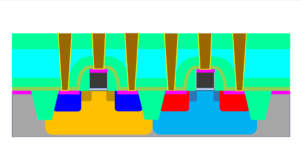

45nmプロセスの概要

45nmプロセスは、2007年前後の先端ロジック半導体のプロセスノードです。

wikiの英語版にも、それなりの内容が書いてあります。

https://en.wikipedia.org/wiki/45_nm_process

45nmプロセスの時代は、ロジック半導体に参入している会社は多く、各社が製品を出していました。その中でも、今回はIntelのプロセスに着目しました。

ベースにしたプロセスは、こちらの論文に掲載されていたものです。Intelの2007年のIEDMでの発表です。

日本語文献でも、解説記事が出ています。(福田昭さんのPC Watchでの解説記事です。)

とはいえ、論文と解説記事だけだと、細かいプロセスは書かれていないので、Intelの特許を探しながら断面を描いています。

2007年の先端ロジック半導体ですから、私自身が関わっていたことはありませんので、プロセス・断面について、実際のものとずれている場合、こっそり教えていただけると助かります。

45nmプロセスは非常に長いので、概要を図にしています。

45nmより前のプロセスと大きく変わっているのは、ゲート絶縁膜にHigh-k絶縁膜を入れたうえで、ゲート電極の材料をpoly-Siから金属材料にしている点です。

45nmより前の世代は、High-k絶縁膜を入れてpoly-Si電極を使用する通称「ゲートファースト」プロセスで作られています。

一方、Intelは45nm世代からHigh-k絶縁膜を入れて、ダミーのpoly-Siゲートを作ったうえで、あとからpoly-Siゲートを金属材料に置き換える通称「ゲートラスト」プロセスを採用しました。

ゲートファーストからゲートラストになると、製造プロセスを大幅に変える必要があるので、以前の世代とプロセスがかなり変わっています。

ゲートラストで製造する場合のキープロセスを解説したかったので、45nmプロセスを今回断面に起こしてみたわけです。

というわけで、45nmプロセスのプロセスフローおよび断面を一から解説していきます。

プロセスフロー

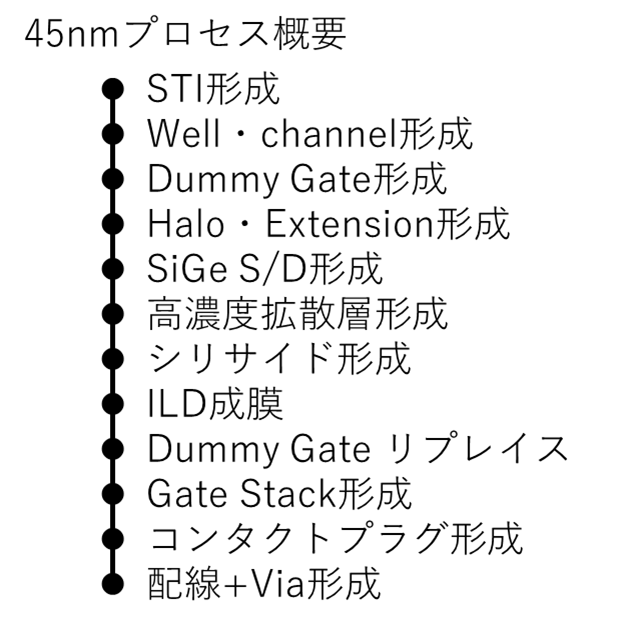

1:基板~STI形成

ロジック半導体を作るにしても、一番最初はSi基板からスタートです。

基板を洗浄したあとに熱酸化して、表面にSiO2層を形成します。

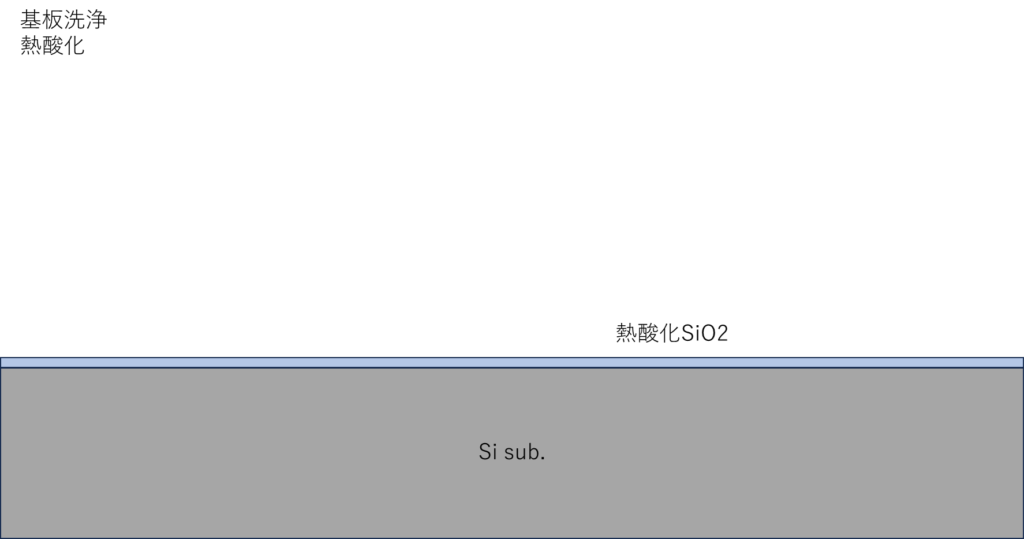

次にSiNを成膜します。

この辺の構造は、180nmプロセスの時と、ほとんど変わっていません。

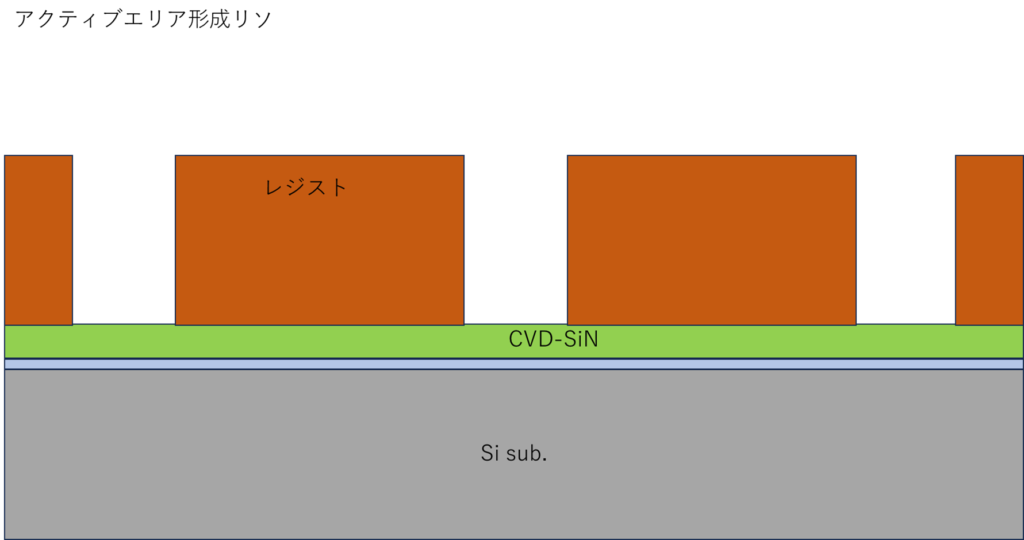

SiNを成膜したら、素子分離のためのリソグラフィーを行います。素子領域をアクティブエリアと呼ぶので、アクティブエリア形成リソと書いています。

細かい話になりますが、2007年当時は露光機がArFドライまでは出ていたはずですが、ArF液浸が使われていたのか定かではありません。素子分離なので、ダブルパターニングや側壁プロセスは使われていないと思いますが、念のため書いておきます。

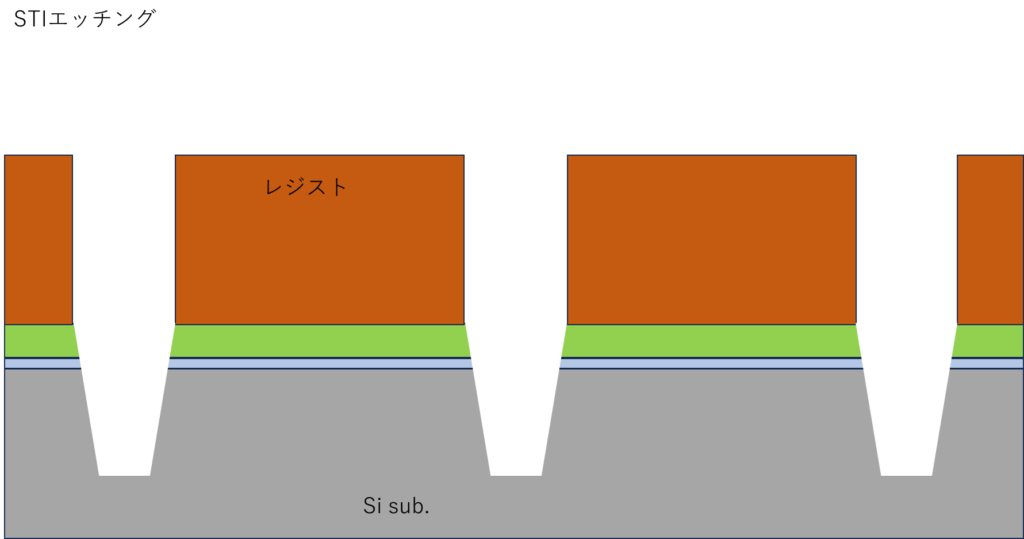

素子領域のレジスト露光ができたら、STIの加工です。

STIの幅や深さは、世代によって変わっています。細かいデータが見れなかったので、適当は幅と深さで描いていますが、ちゃんと描くときはスケール感を合わせないと、あとから縮尺が合わなくなるので困ります。

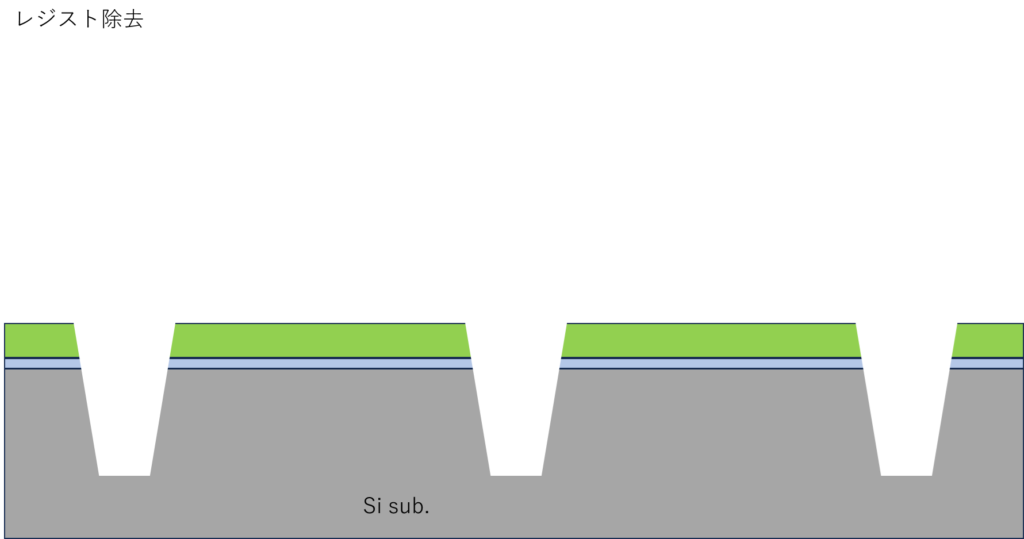

STIが加工できたら、レジストを除去してやります。そうすると、STIの領域に溝が掘られた断面ができます。

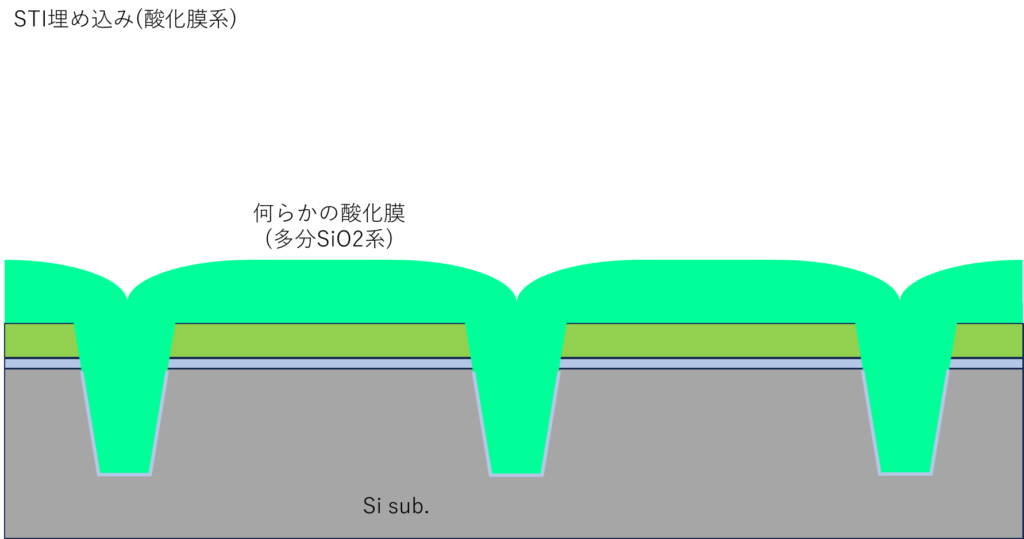

STIの溝が掘れたので、次は埋め込みにかかります。

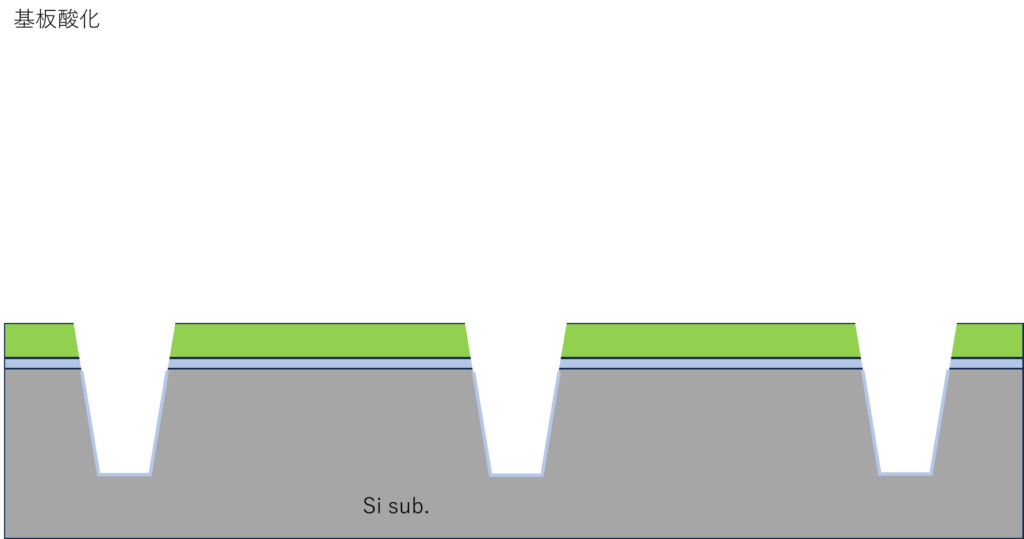

45nmプロセスで行われているかは明記されていませんでしたが、STI領域のSiの酸化はおそらく行われているでしょう。

そして、形成したSTIを酸化膜系の膜で埋め込みます。

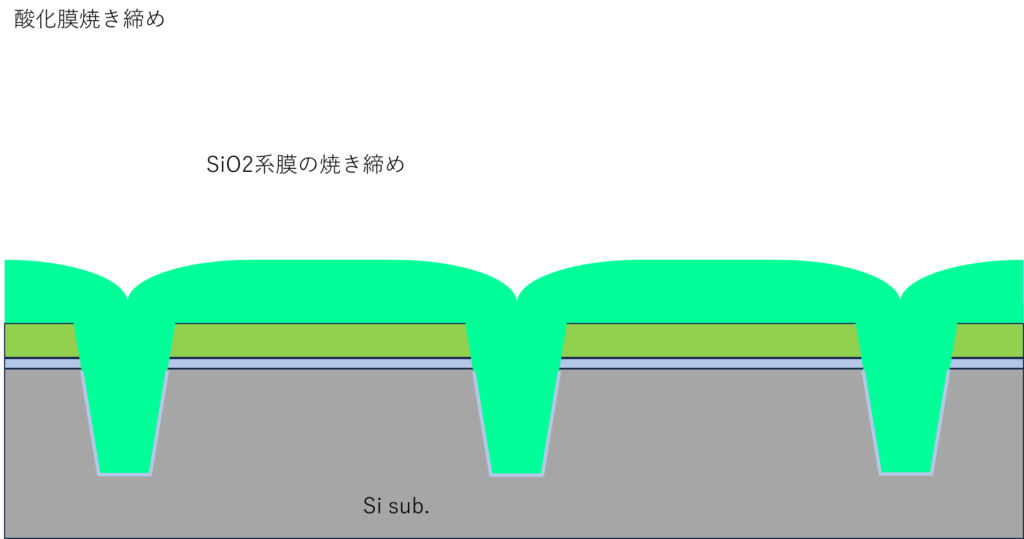

STIの埋め込みが終わったら、酸化膜の焼き締めを行います。焼き締めを行う理由としては、HF系の薬液に対する耐性を高めるためでしょう。

SiO2系の酸化膜は、膜質によってHF系の薬液へのエッチングレートが大きく変わります。

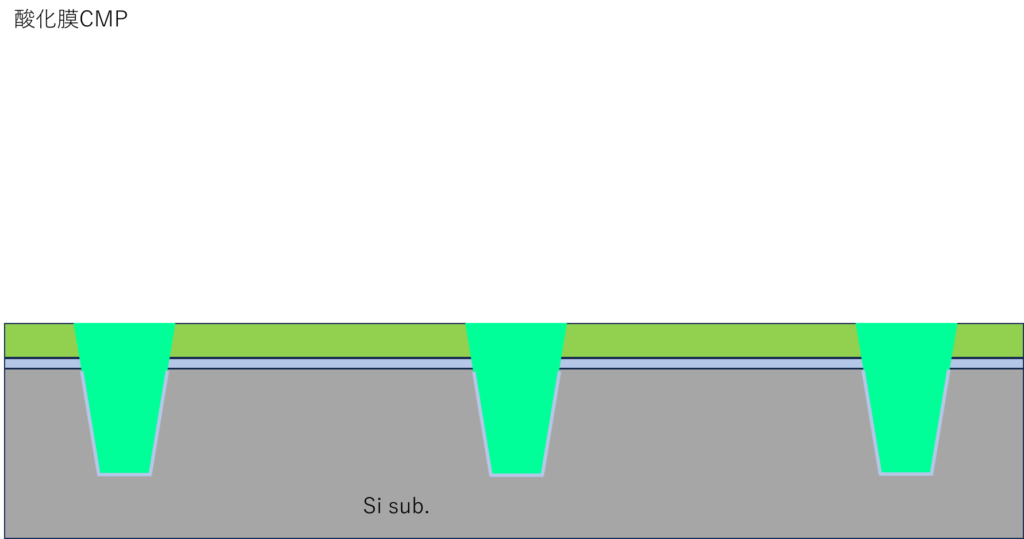

STIの埋め込みができたので、CMPで平坦化することで、掘った溝の領域だけが酸化膜で埋まるようにします。

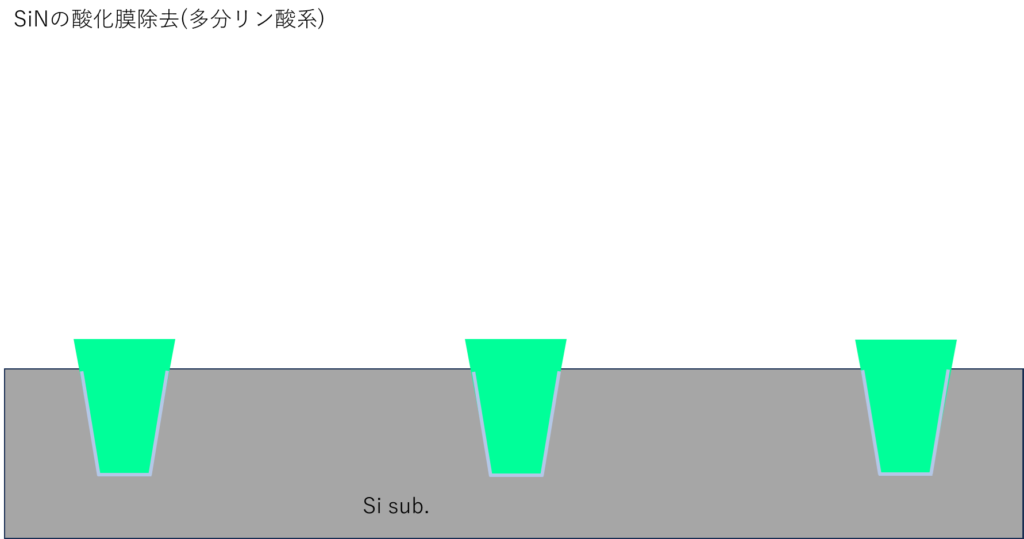

ここまできたら、表面に残っているSiNを取ってやればSTIの完成です。

ここでSiN層は、おそらくリン酸系の薬液によるウエットエッチングで除去されていると考えられます。

ドライエッチングで取ろうとすると、STIと基板の間の領域にSiNが残ってしまうのと、Si基板をエッチストップレイヤにする必要があるので、この時点ではドライエッチングよりウエットエッチングを使った方がよさそうです。

ここまでのプロセスで、STI形成まで完了しました。正直、ここまでのプロセスは180nm世代と変わっていません。

STIの幅と深さ、露光時の露光線幅は変わっていると思いますが、製造プロセス自体はそれほど大きな変更はないと考えられます。

2:Well・Channel形成

STI形成まで進んだので、次はWell・Channel領域を形成していきます。

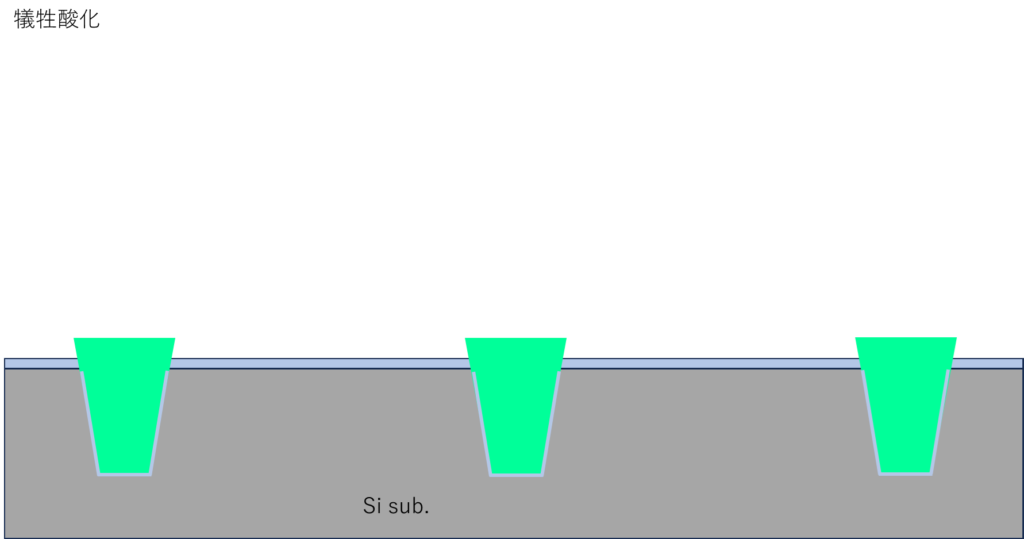

Well・Channelの形成の前に、犠牲酸化を行って表面を一度熱酸化膜にしてやります。

ここから、Well・Channel領域用のイオン注入に入ります。この図では、左側にNMOS、右側にPMOSを作っていきます。

Well・Channelのイオン注入をNMOSからやるのか、PMOSからやるのかは、各社それぞれ文化があると思いますが、この記事では特段理由が無い限りNMOS、PMOSの順番にやっていきます。

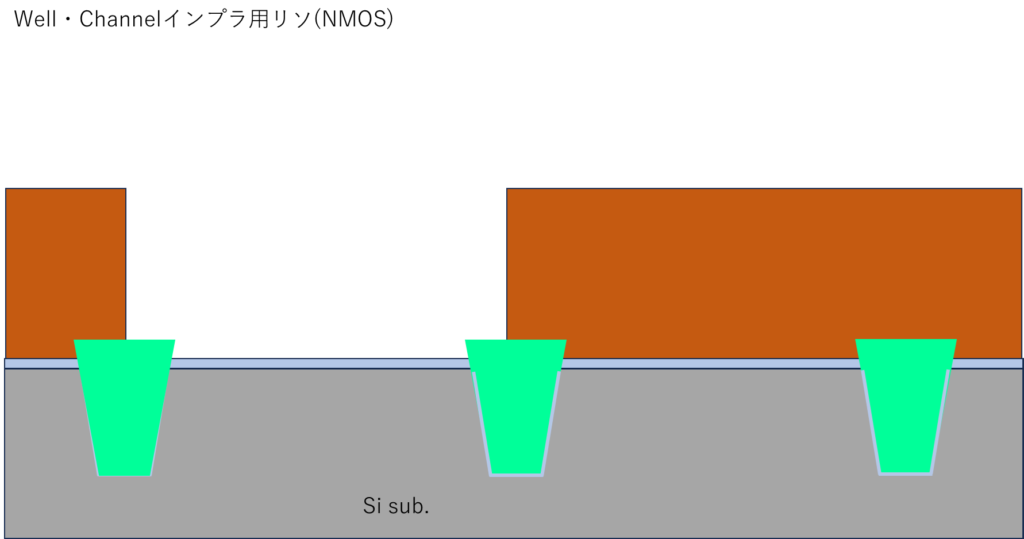

NMOS用のWell・Channelのイオン注入用に、NMOS以外の領域にイオンが入らないようにするために、リソグラフィーを行います。

左側の領域がNMOSなので、NMOS領域だけを開口しました。

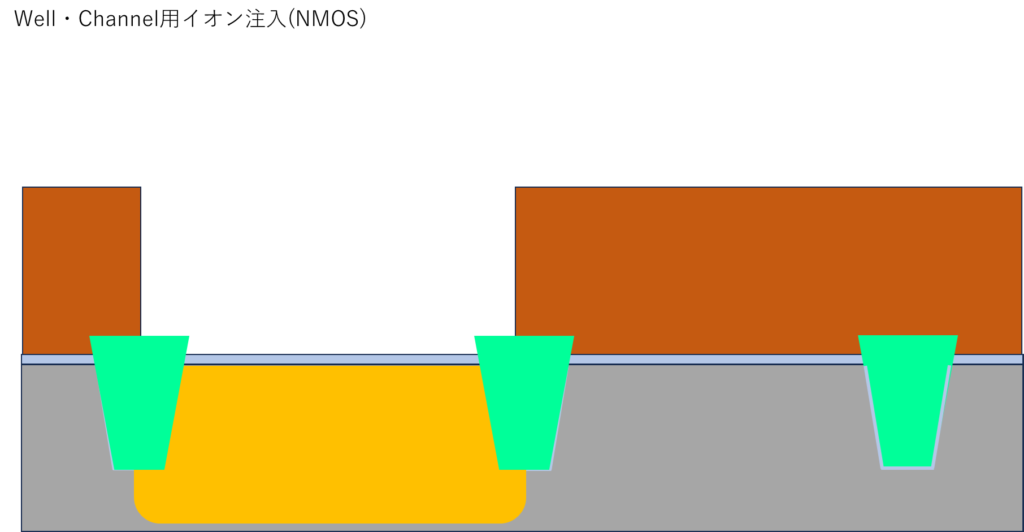

開口した領域に、NMOSのWell・Channel用のイオン注入を行います。

NMOSのWell・Channel領域には、P型の不純物を打ち込みます。ホウ素(B)を打つことが多いでしょう。

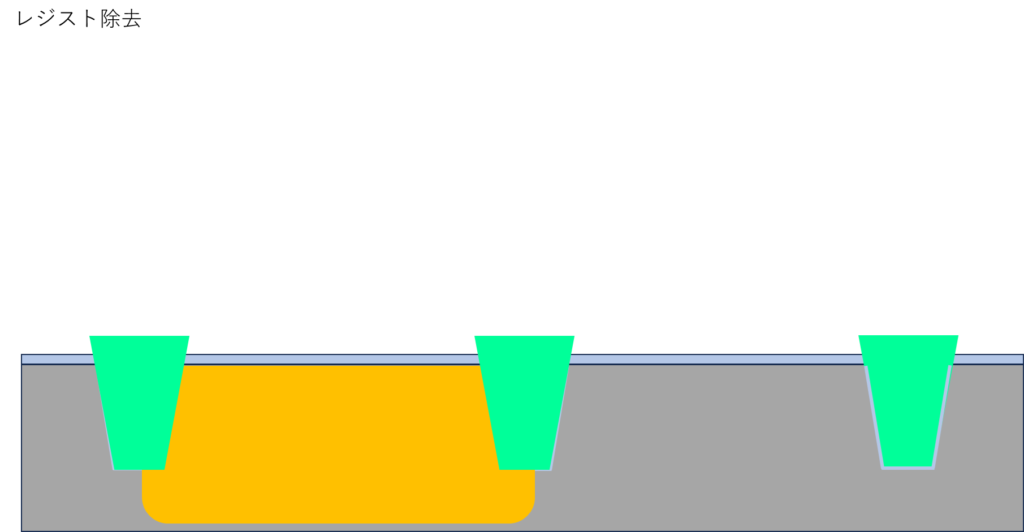

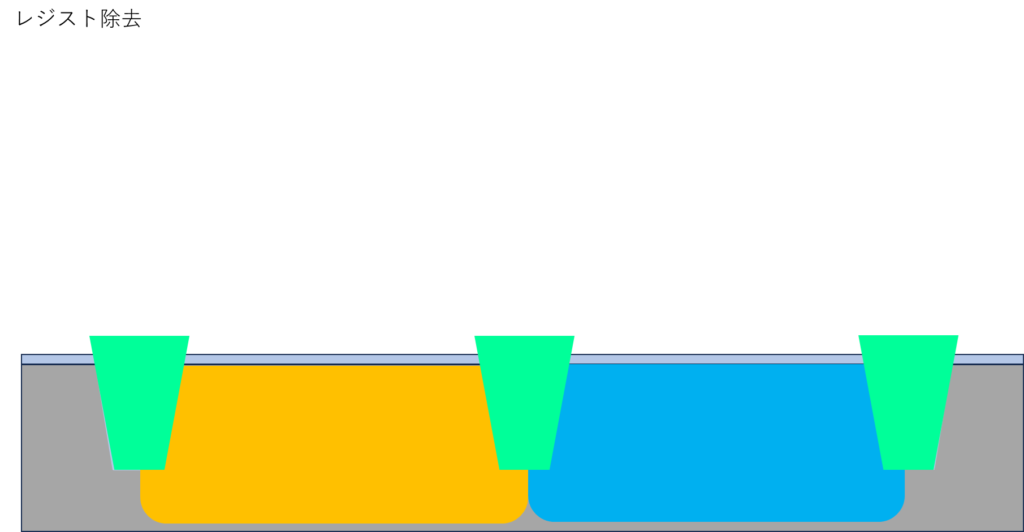

イオン注入が終わったら、レジストを除去します。

レジストを除去してやると、NMOS領域だけにWell・Channelのイオン注入がなされた状態になりました。

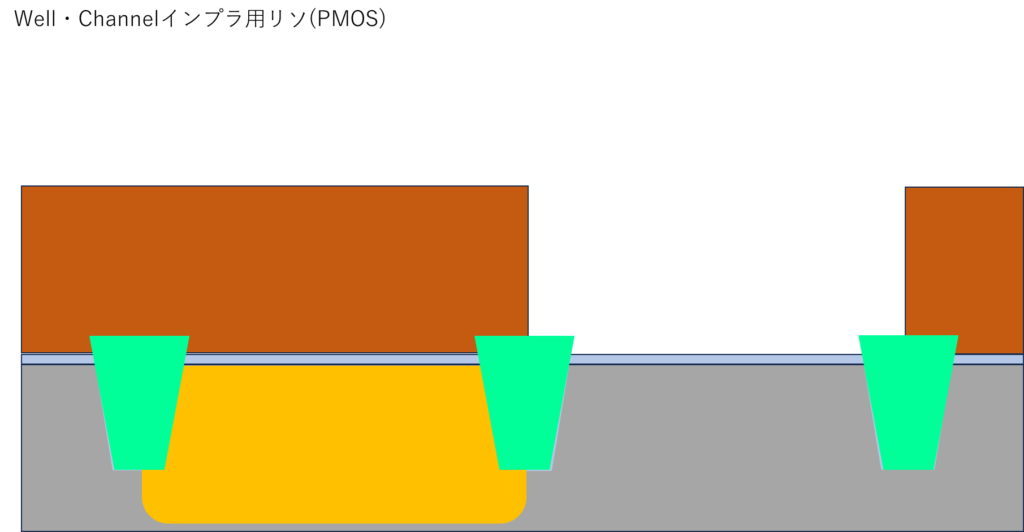

NMOSと同様に、PMOS側にもWell・Channelのイオン注入を行います。

NMOSの時と同様に、左側のPMOS側だけが開口するようにリソグラフィーを行います。

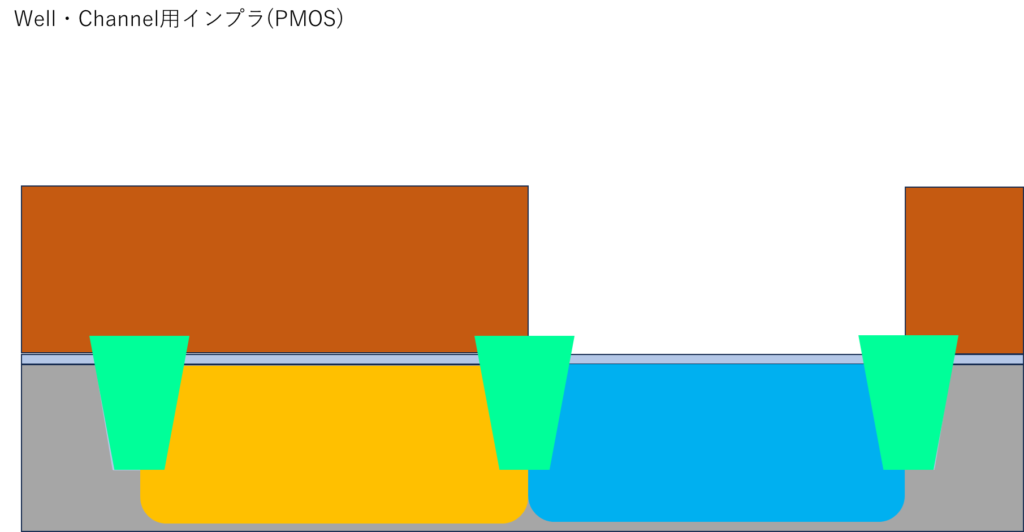

そして、PMOSの開口部に、PMOSのWell・Channel領域のためのイオン注入を行います。

イオン注入後に、レジストを除去してやると、このようになります。

これで、NMOS・PMOSともに、Well・Channel領域を形成することができました。

おそらく、このあと活性化アニールが入っているはずですが、特に断面は変わらないので、このまま進めます。(厳密に言うとイオン注入した不純物が熱拡散しますが、Well領域の不純物はChannel領域と比べて非常に深い領域に打たれているので、熱拡散はここでは強調しません。)

3:Dummy Gate形成

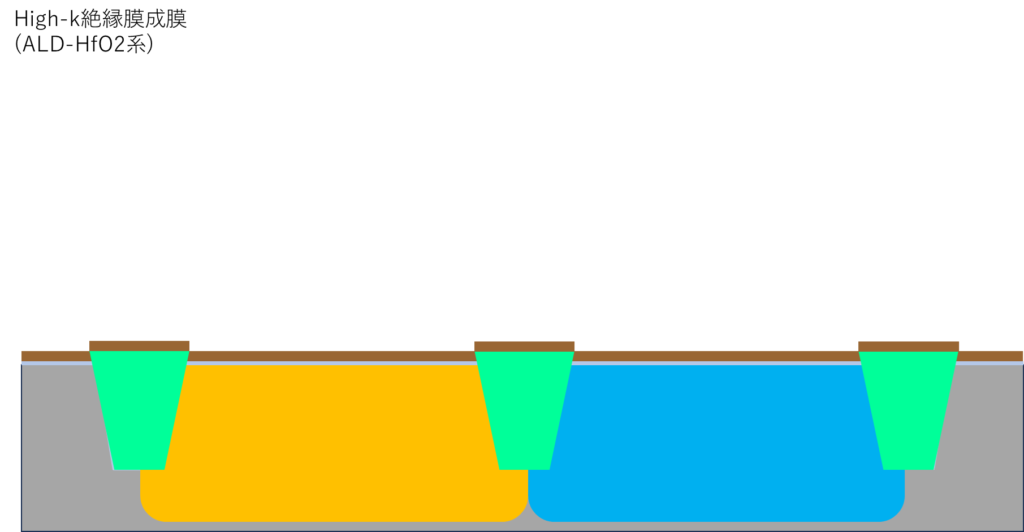

ここから、Dummy Gate形成に入ります。大まかな流れは、High-k絶縁膜成膜、poly-Si成膜、ゲート加工の3つです。

まずは、ゲート絶縁膜の形成工程です。絶縁膜を作る前に、基板表面を洗浄します。(多分フッ酸系の処理です。)

そして、ゲート絶縁膜を形成しますが、Siとの界面は非常に薄いSiO2を形成します。

Si表面に形成するSiO2膜が、熱酸化で形成されているのか、ケミカルOxで作られているのかは、断面だけではわかりませんが、おそらくケミカルOxなのではないかと考えています。

非常に薄いSiO2(1nm以下)を安定的に形成するのは、熱酸化だと難しいからです。(ばらつき等含めて。)

Siの酸化を定量的に表現しているDeal-Glove modelよりも、最初期の酸化は速く進むことが知られています。(ドライ酸化の場合。)

この辺の詳しいことは、こちらの記事に書かれています。

というわけで、極薄のSiO2を形成したあと、High-k絶縁膜を形成します。

ご存じの方が多いと思いますが、簡単にHigh-k絶縁膜について解説します。

High-k絶縁膜と言いますが、High-k(kはギリシャ文字のκで書かれることもあります。)のkの意味は誘電率が高いということです。

従来トランジスタの絶縁膜として使われていたSiO2より誘電率が高い材料のことを、High-k材料と呼んでいます。例えば、HfO2・ZrO2・SiNなどがあります。

45nmプロセスで使われているHigh-k絶縁膜の材料は、HfO2ベースの材料だと言われています。窒化処理などが入っているかもしれませんが、HfO2を中心とした材料です。

HfO2なんて、どうやって成膜するのか?という話になりますが、ALDで成膜することができます。ALDで成膜できるので、成膜したい部分の形が多少変わっても、カバレッジの問題は出にくいです。(スパッタ成膜しかできないと、カバレッジの問題が出てきます。)

つらつら書きましたが、High-k絶縁膜にHfO2ベースの材料を使うが故に、リプレイスメントメタルゲート構造を取らなければいけなくなったという事情もあります。

この点について書き始めると長くなるので、別記事で詳しく書いていきたいと思います。

さて、45nmプロセスに戻ります。

High-k絶縁膜を成膜したあと、Dummy Gateとしてpoly-Siを成膜します。

Dummy Gateと呼んでいるのは、最後にここで積んだpoly-Siのゲートを金属に置き換えるからです。

従来のプロセスでは、ここで形成したpoly-Siをそのままトランジスタのゲートとして使っていました。

ここで積むSiは、poly-Siで積むのと、a-Siで積むのと2通り考えられます。断面を考えるだけであれば、どっちでもいいんですが、実際のプロセスでどっちを選択するのかは、表面のラフネスとか膜厚の制御性で決まるのではないかと考えられます。

ゲートラストのプロセスだと、最終的にここのpoly-Siは金属に置換するので、不純物のドーピングは特にやらなくていいです。(勝手にドーピングされる工程は、あとから出てきますが。)

Dummy Gate用のpoly-Siを成膜したあと、Cap用のSiNを成膜します。(もしかしたらSiO2かもしれませんが、おそらくSiNだと思われます。)

このSiN膜の存在を当初見落としていて、あとの工程(シリサイド形成工程)でpoly-Siの上に保護膜無いとダメじゃん・・・と思って断面描き直したんです。

ここのSiN膜が必要な理由は、あとからわかります。現段階だと、無くても問題なさそうに見えますが、あとから問題が出てきます。

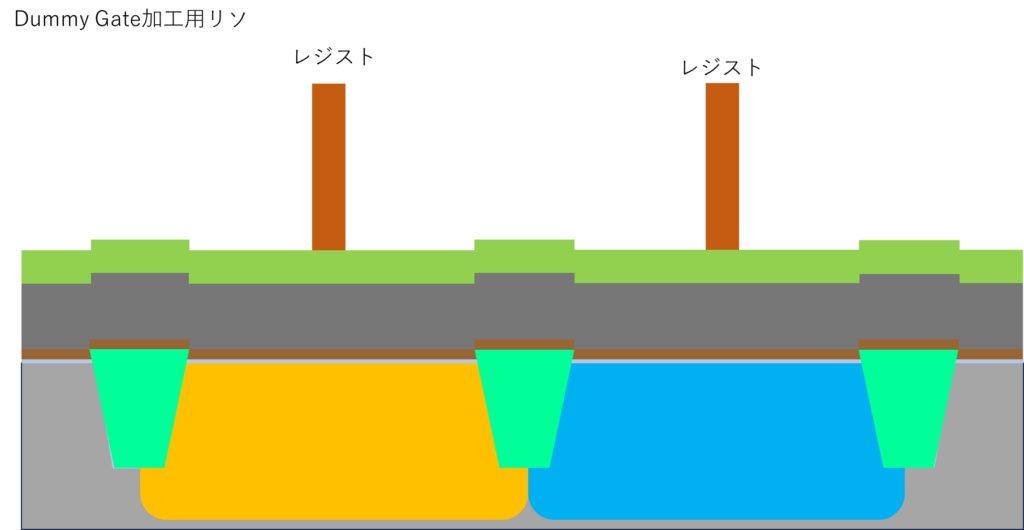

Dummy Gate用のゲート材料の成膜が終わったので、次はゲート加工に移ります。

ゲート加工用に、リソグラフィーを行います。

ここで、一つだけ注釈があります。45nmプロセスが発表された2007年当時、ArF液浸の露光機が量産として使われていたのかがわかりませんでした。

ArF液浸が使えていたのであれば、1発で露光できてもおかしくないと思いますが、ArFドライの露光機を使っていたのであれば、ダブルパターニングが必要になってきます。

ArF液浸が使えていれば話は早いんですが、当時はArFドライしか使えていなかったのであれば、少し話は変わってくるので、識者の方は教えていただけると幸いです。

記事の図としては、ArF液浸を使って1発でゲートを露光する形で描いています。

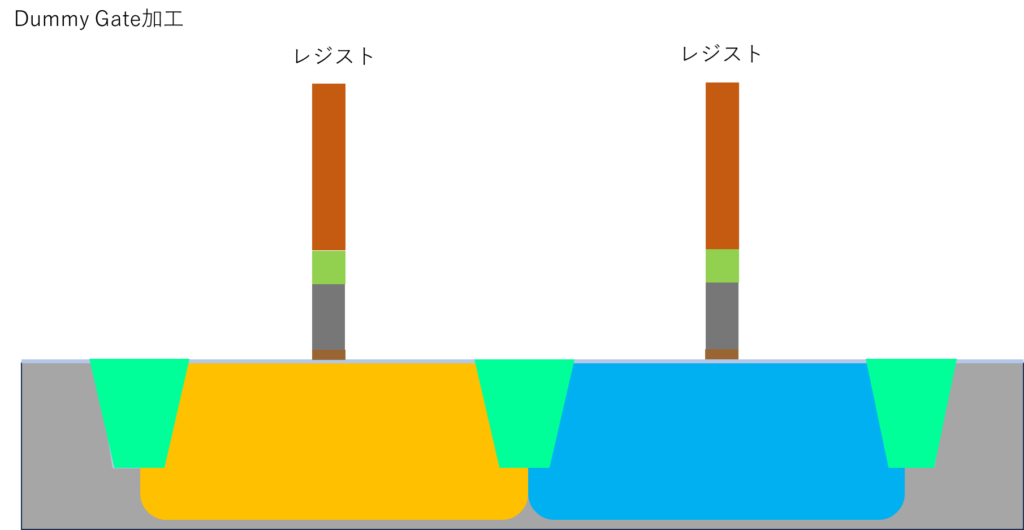

露光できたら、Dummy Gateごと加工していきます。

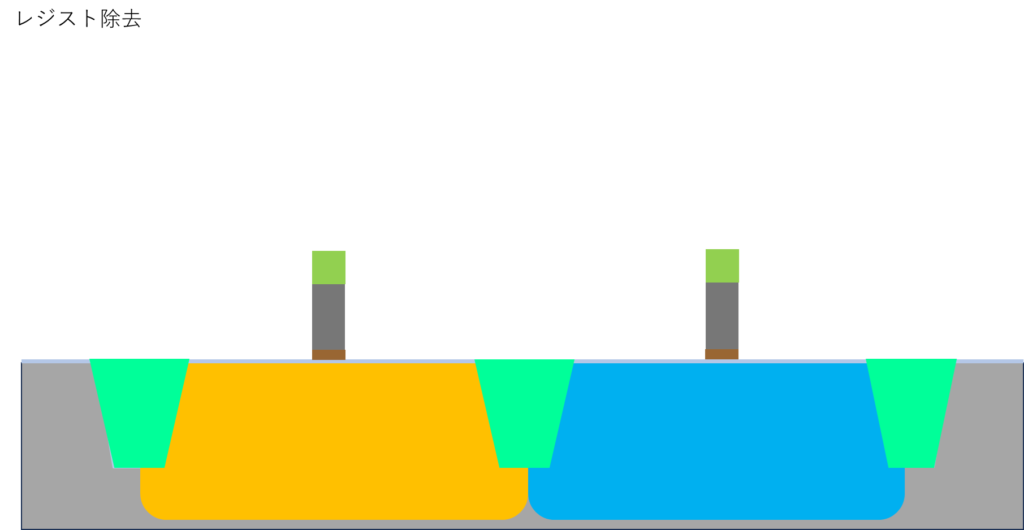

加工できたら、レジストを除去することでDummy Gateのゲートスタックが完成します。

ここまでの工程で、Dummy Gate周りのゲートスタックまで完了しました。

High-k絶縁膜を適用していること以外は、従来のプロセスとそれほど大きく変わりません。(High-k絶縁膜を使うので、装置等は大きく変わっていると思われます。)

Dummy Gate形成まで終わったので、ここからはチャネル直下の不純物プロファイルを調整する工程に入ります。

4:Halo・Extension形成

ゲート形成ができたので、トランジスタのチャネル直下の不純物を調整する工程に入ります。

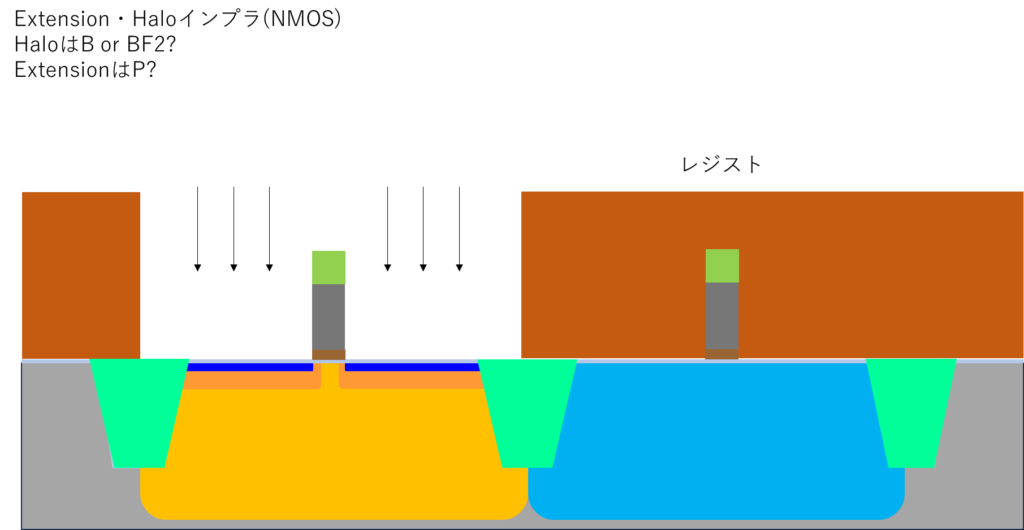

チャネル直下の不純物注入には、ExtensionとHaloの2種類があります。

Extensionは、NMOSであればN型の不純物を、PMOSならP型の不純物を打ちます。高濃度かつ浅く不純物を打つことで、オン時の抵抗を低減する効果があります。

Haloは、Extensionを取り囲むように、Extensionと逆の極性の不純物を打ちます。NMOSであればP型の不純物を、PMOSであればN型の不純物を打ちます。

単純にExtensionを打つだけだと、オン時の抵抗は下がりますが、閾値電圧が下がってしまうので閾値電圧の低下を抑えるためにHaloが打たれます。

ExtensionとHaloの注入条件(ドーズ量・打ち込み角度等)は、デバイスメーカーのノウハウです。

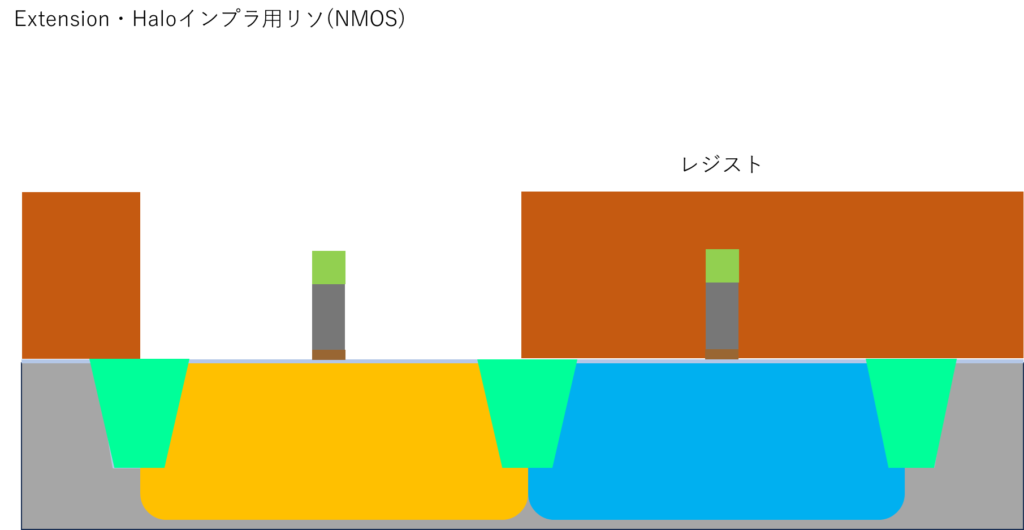

それでは、NMOSのExtension・Haloの注入から始めます。

Well・Channelの時と同様に、NMOS側だけ開口するようにリソグラフィーを行います。(左側がNMOS、右側がPMOSです。)

開口部に対して、ExtensitonとHaloを打ちます。

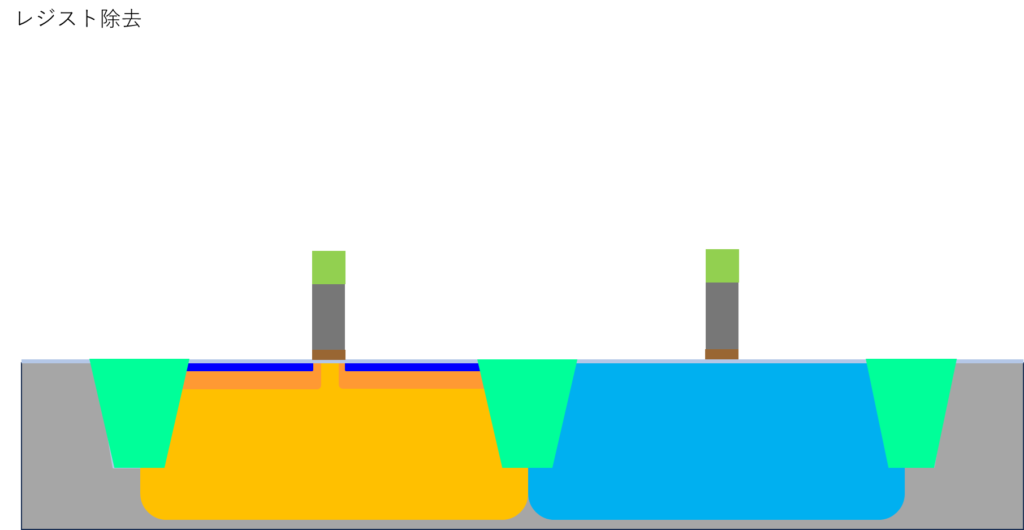

イオン注入後レジストを除去すると、NMOS領域のExtension・Haloが打たれた状態になります。

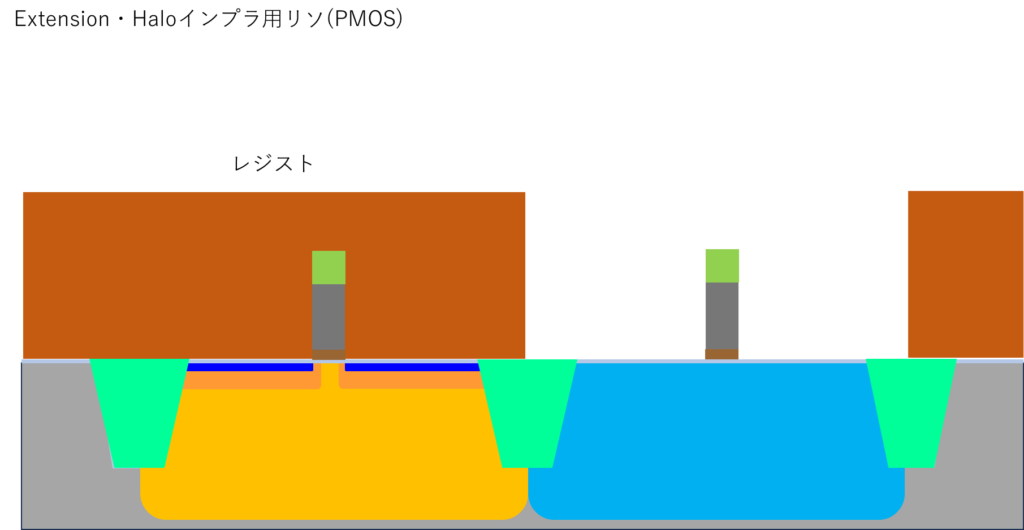

NMOSのExtension・Haloの形成が終わったので、次はPMOSです。

PMOS側だけ開口するように、リソグラフィーをおこないます。

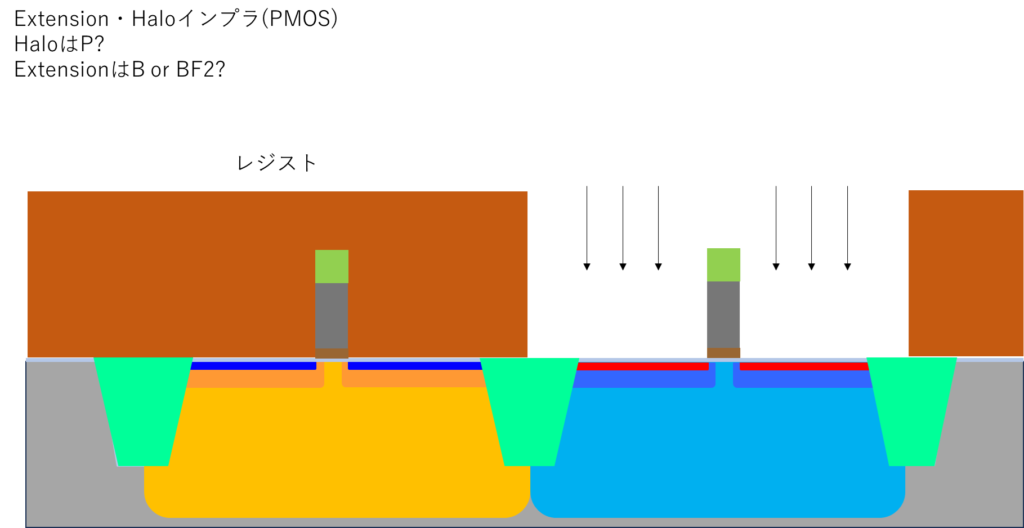

PMOS側だけ開口できたので、Extension・Haloを打ち込みます。

最後に、レジストを除去してやると、このようになります。

これで、NMOS・PMOSともに、Extension・Haloを形成することができました。

このあと、活性化アニールが入っているかもしれませんが、次にSiGeをEpiするので、この時の熱負荷を考えるとスキップされているかもしれません。

活性化アニールが入っていたとしても、Extensionが拡散しすぎてしまうと、閾値電圧が下がってしまうので、短時間かつ活性化率が上がるようなアニール方法が取られていることは間違いありません。

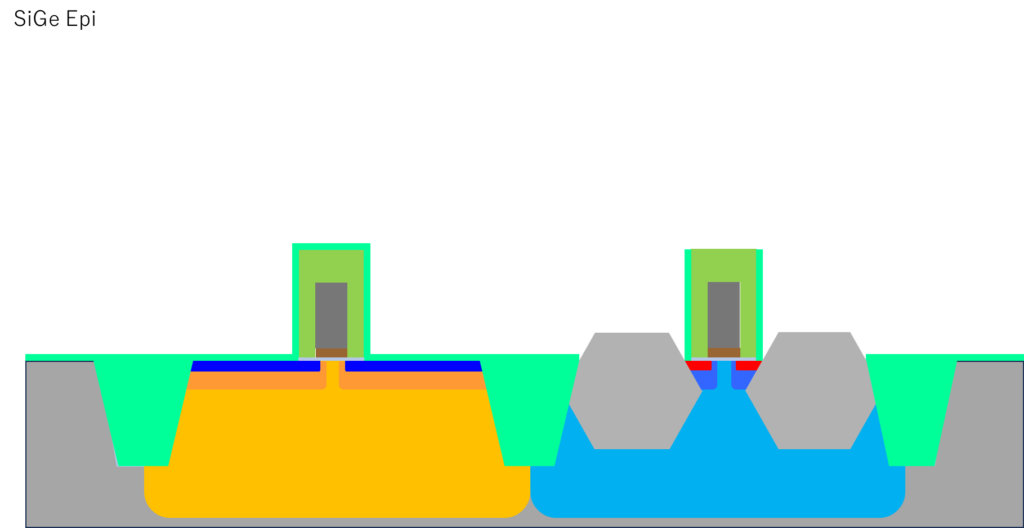

5:SIGe S/D形成

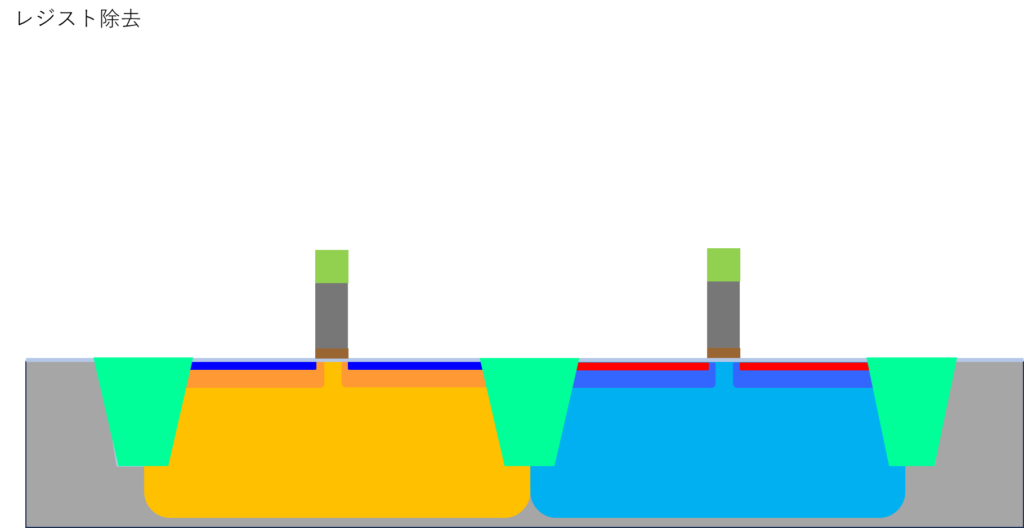

NMOS・PMOSともに、Extension・Haloを形成できたので、ここからスペーサーを形成します。

そして、スペーサーを形成後、45nmプロセスの見どころの1つである、SiGeソースドレインを形成していきます。

まずは、スペーサーを形成します。どうも、SiNでスペーサーが作られているようです。

CVD-SiNでスペーサーを形成しているので、全面にSiNがつく形になります。

全面に成膜したSiNを全面エッチバックすると、このようになります。

こんな形でSiNスペーサーを作っていると考えられます。

スペーサーの膜厚で、あとから作る高濃度拡散層の距離が決まってくるので、膜厚制御はシビアでしょう。

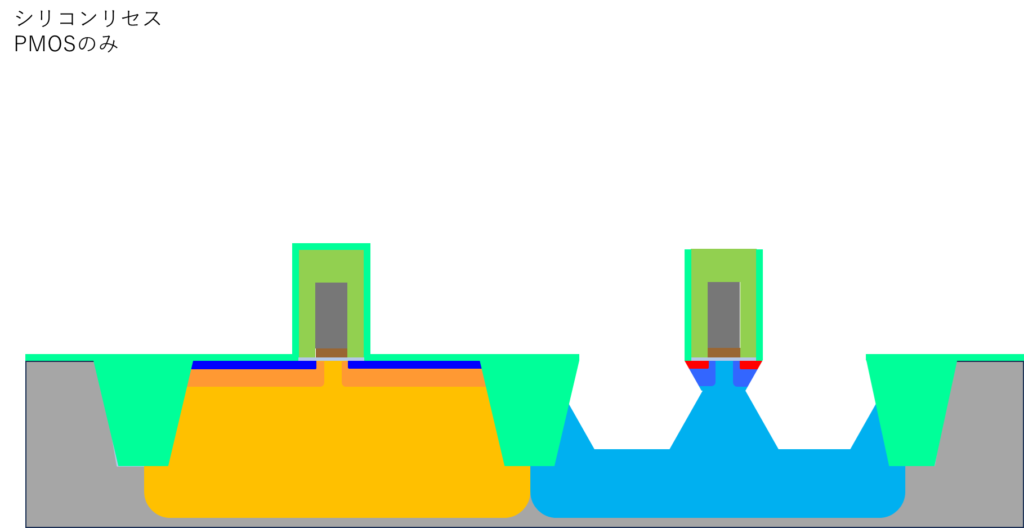

45nmプロセスでは、PMOSのみにSiGeソースドレインを適用しています。簡単な流れは、PMOS側のソースドレイン領域のSiをエッチングして、SiGeをエピする形になります。

この時に、NMOS側にSiGeがエピされてしまうと問題なので、PMOSでSiGeエピする場所だけ開口しておく必要があります。

SiGeエピを行う時にはそれなりの温度(800℃以上)がかかるので、レジストでは対応できません。そこで、SiO2のマスクを切ってやることが必要になります。

というわけで、SiO2を全面に成膜します。

今回は、PMOS側だけ開口したいので、レジストでPMOS側だけを開口します。

開口したPMOS側はSiO2保護膜をエッチングする必要があるので、エッチングします。

この時、SiO2のエッチングをドライにしているか、ウエットにしているのかはわからないですが、加工寸法の精度で決まっているのではないかと考えられます。

ドライエッチングの場合は、ほとんどレジストの寸法に近いエッチング形状が得られますが、ウエットエッチングの場合、どうしてもサイドエッチが発生し、レジストの寸法よりも開口が広がります。

基板へのダメージやコストを考えると、ウエットエッチングの方が有利ですが、加工寸法ではドライエッチングの方が有利です。

ここは、寸法とコストとどちらが優先されるかで、決まってくると思われます。(この記事の図では、ドライエッチングを使った場合の断面を描いています。)

そして、レジストを除去すると、SiO2保護膜がPMOS領域だけ開口された形ができます。

さて、PMOS領域だけ開口できたので、Siのリセスを行います。

Si基板をエッチングするのは、おそらくアルカリ系の薬液でのウエットエッチングだと思われます。

45nmプロセスでは、Si基板へのエッチングが異方性エッチングになっているので、面方位依存性が出るようなエッチング条件にしていると考えられます。

PMOSのソースドレイン領域をエッチングすると、このようになります。

なかなか、派手な見た目をしています。(そう感じるのは私だけかな?)

この空間にSiGeをエピしていきます。

エピしたSiGe領域は、もともとのSi基板よりも高い位置になっています。

SiGeのエピは、正確にはSi基板へのSiGeのヘテロエピタキシャル成長です。基板材料と同じ材料をエピする場合には、ホモエピタキシャル成長、違う材料をエピ成長する場合にはヘテロエピタキシャル成長と言います。

なぜわざわざPMOSだけにSiGeをエピしているのかというと、PMOSのホールの移動度を上げたいからです。

Siのホールの移動度は、圧縮歪み(正確に言うと、一軸圧縮歪み)を掛けると上がることが知られています。そこで、PMOSに対して、チャネル領域に圧縮歪みを掛けるために、わざわざSiGeをエピしています。

GeはSiより格子定数が大きいので、SiGeはSiよりも格子定数が大きくなります。そうすると、SiGeエピしてやることで、PMOSのチャネル領域にはソース側とドレイン側から圧縮歪みがかかります。この効果を狙っています。

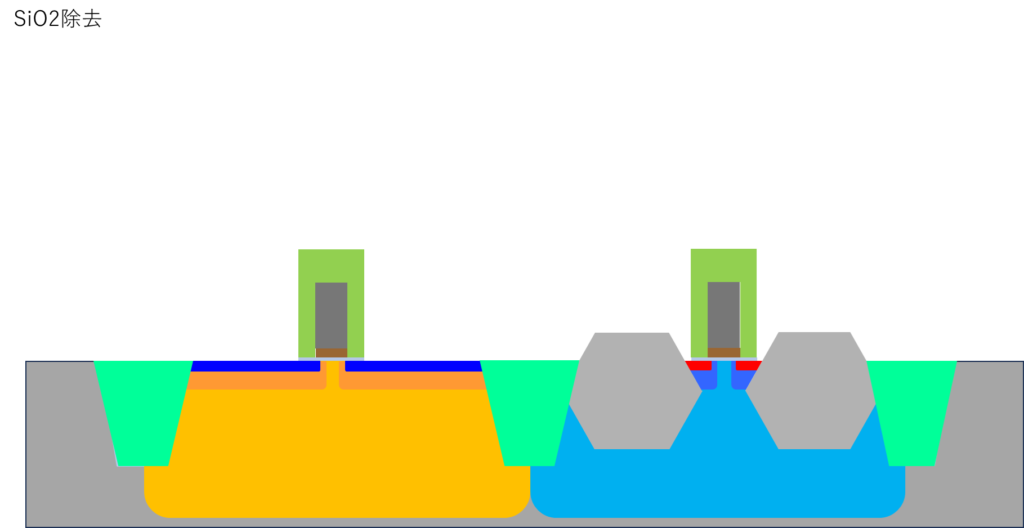

SiGeエピが終わったら、SiO2の保護膜をエッチングしてやります。

これで、PMOSのSiGeソースドレイン形成まで終わりました。

PMOSのソースドレインのSiGeエピが終わったので、ここからは高濃度拡散層の形成に入ります。

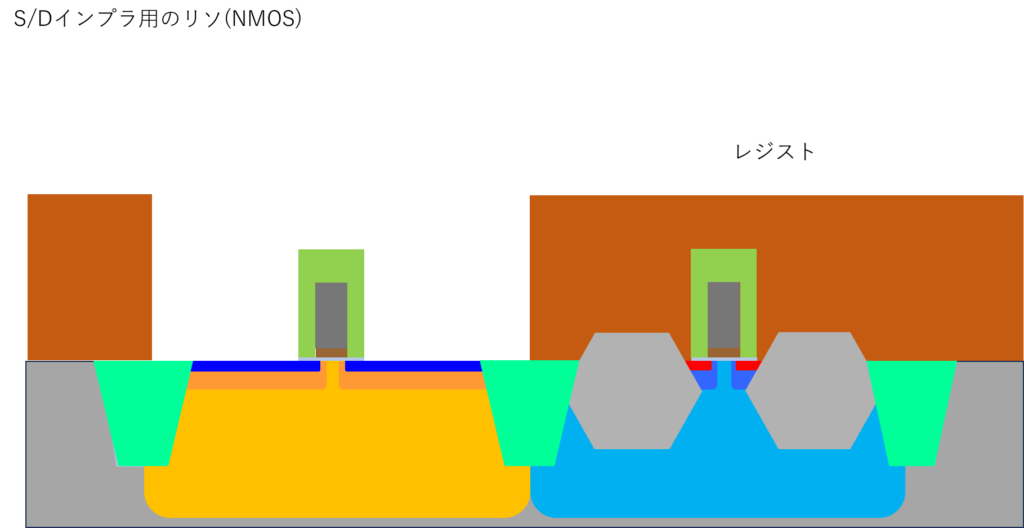

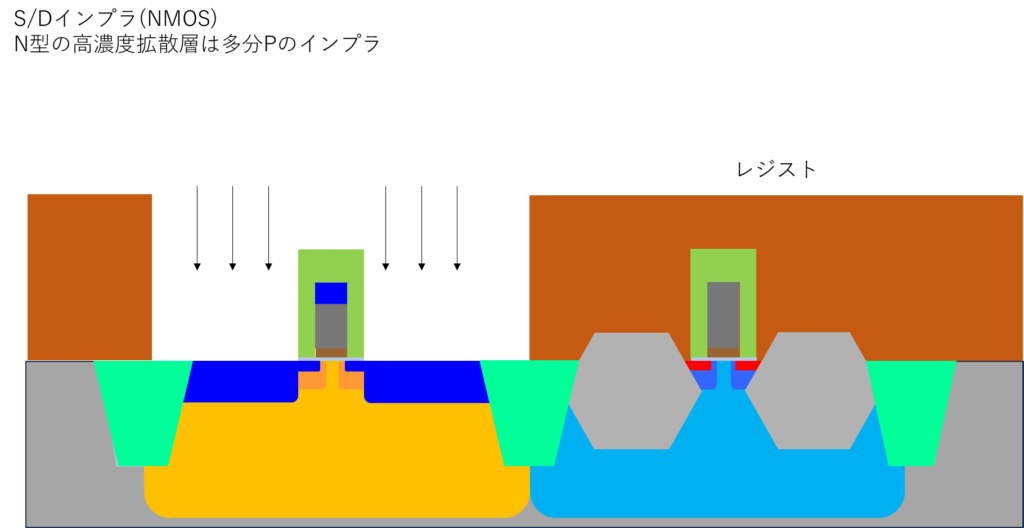

6:高濃度拡散層形成

NMOS・PMOSの高濃度拡散層を形成していきます。

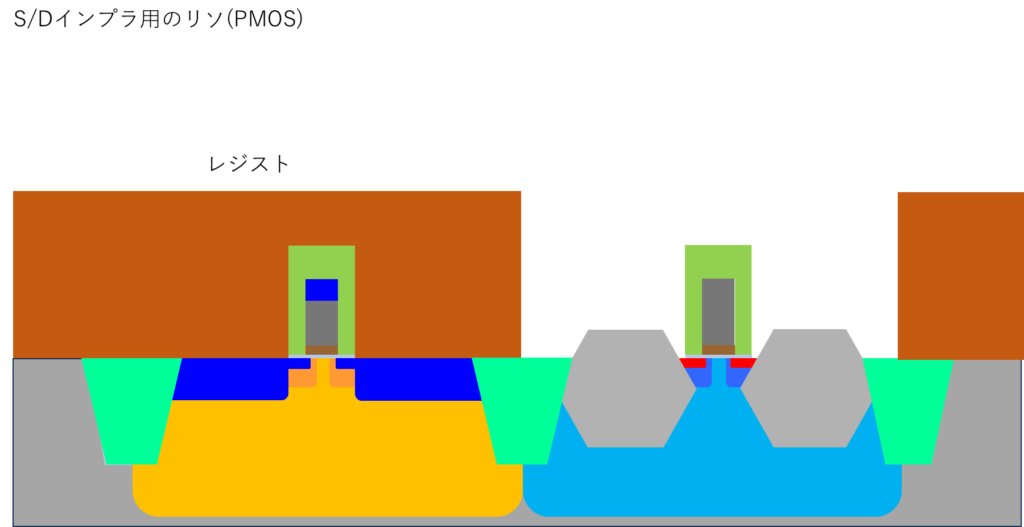

まず、NMOS領域だけを開口するようにリソグラフィーを行います。

NMOS領域だけ開口したあと、高濃度拡散層のイオン注入を行います。

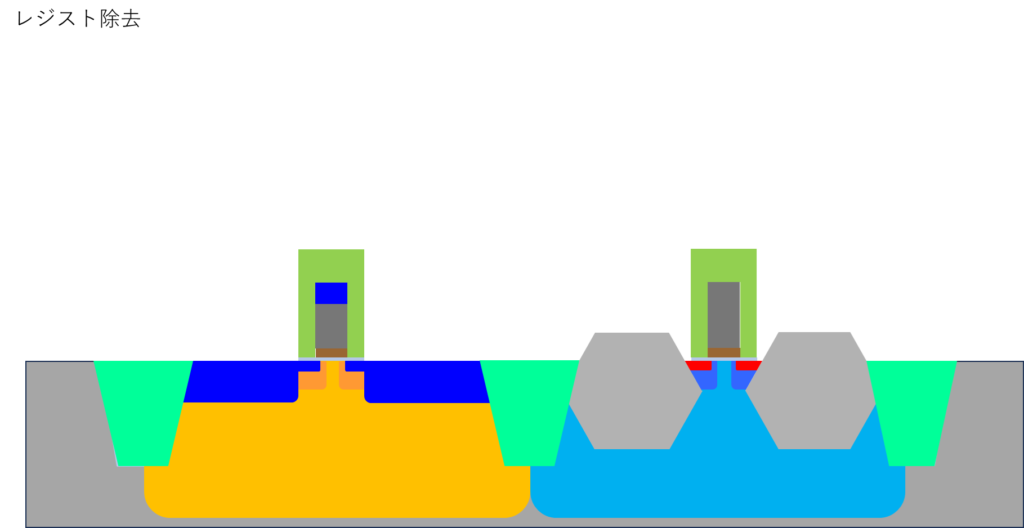

レジスト除去すると、NMOS領域の高濃度拡散層が打ち込まれた状態になります。

細かい芸ですが、高濃度拡散層のイオン注入の時に、Dummy Gateの領域にもイオンが打ち込まれます。

これはイオン注入の仕組みから考えて仕方ないですが、Dummy Geteの上部はNMOSはN型・PMOSはP型になっている領域ができます。

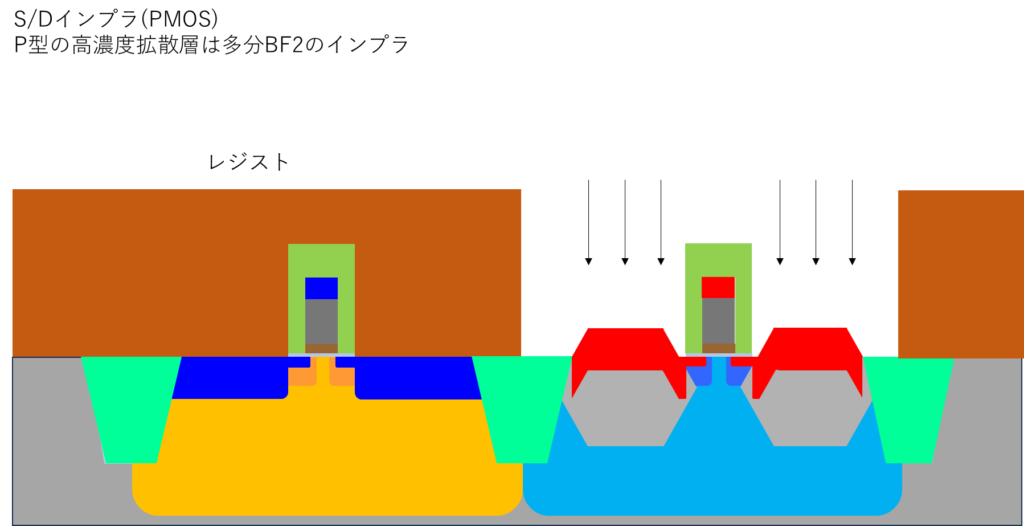

続いて、PMOS領域を開口するようにリソグラフィーを行います。

PMOS領域に、高濃度拡散層向けのイオン注入を行うと、このようになります。

ざっくり描いているので、イオン注入の深さはデバイスメーカーが設計しているので、この図の通りとは限りません。

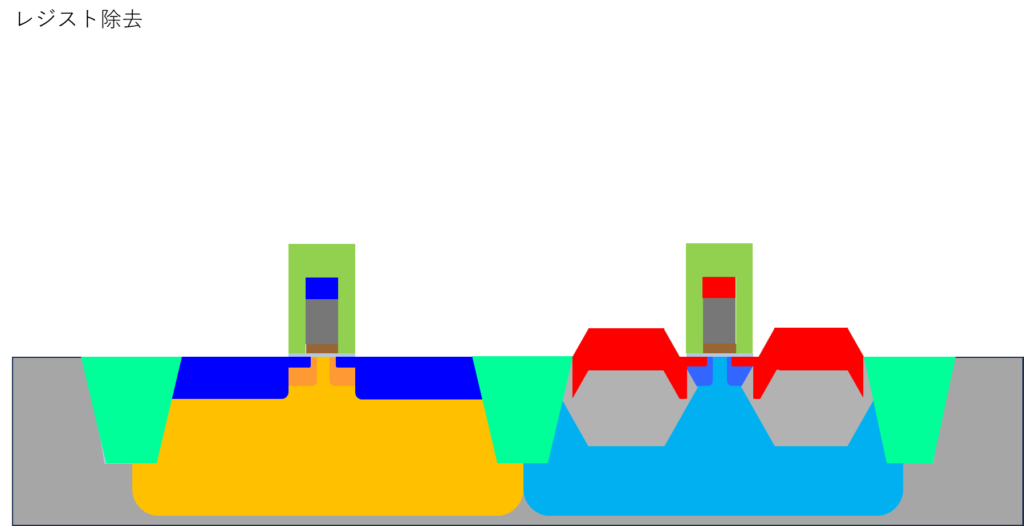

レジストを除去してやると、NMOS・PMOSともに、高濃度拡散層が打たれた構造ができました。

やっと、高濃度拡散層形成までたどりつきました。

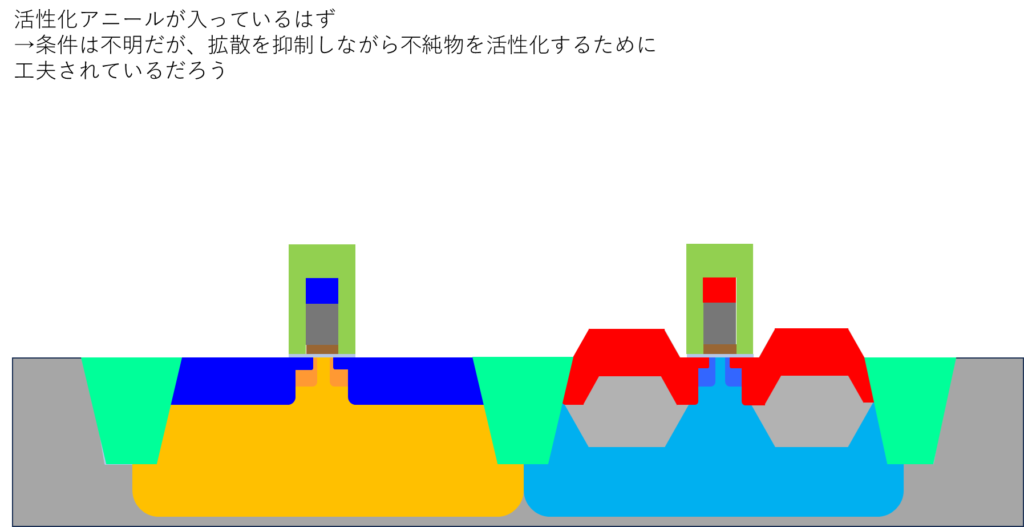

シリサイド形成の前に、活性化アニールが入っていると思われます。

細かい条件はわかりませんが、少し不純物分布のプロファイルが伸びるでしょう。

ここまで形成できたら、シリサイド形成に入ります。

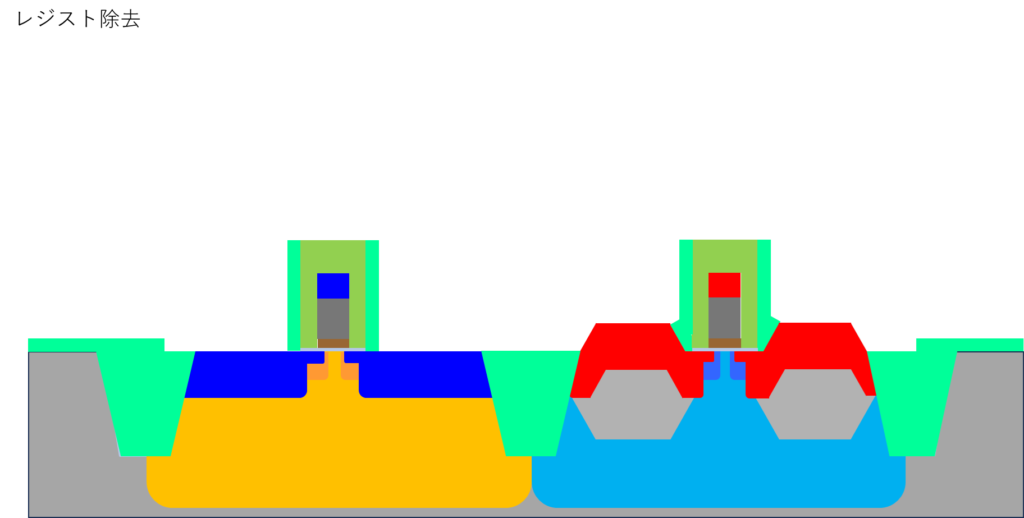

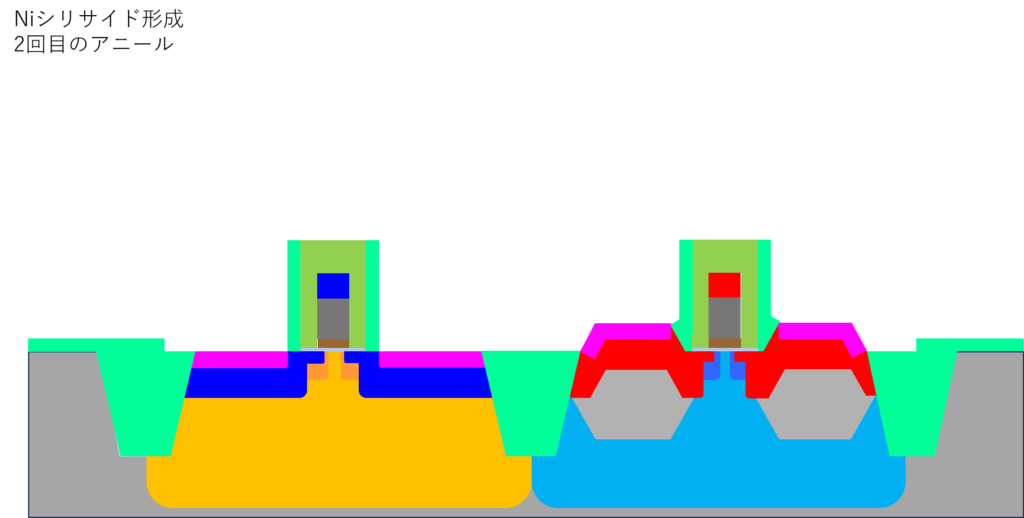

7:シリサイド形成

45nmプロセスで使われているのは、Niシリサイドです。180nmプロセスではCoシリサイドが使われていましたが、45nmプロセスではNiシリサイドに変わっています。

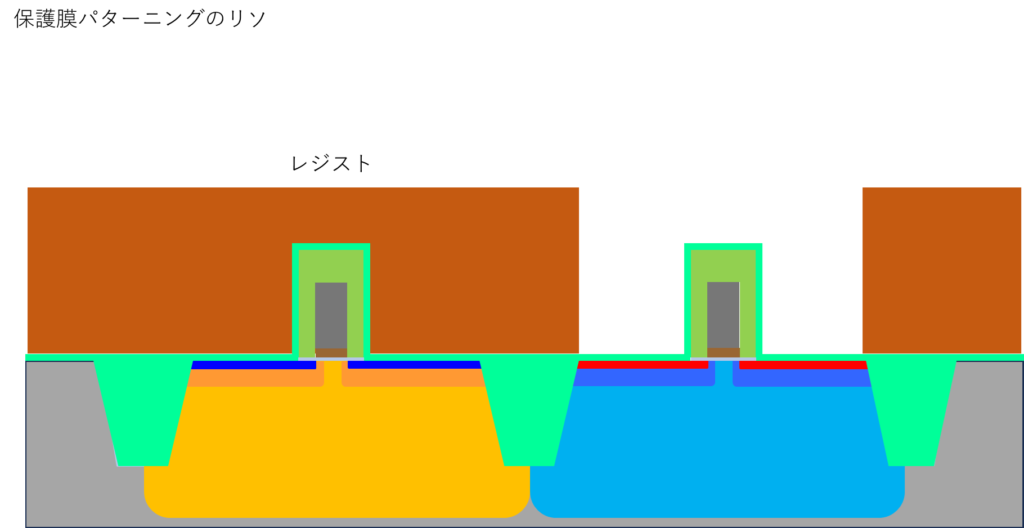

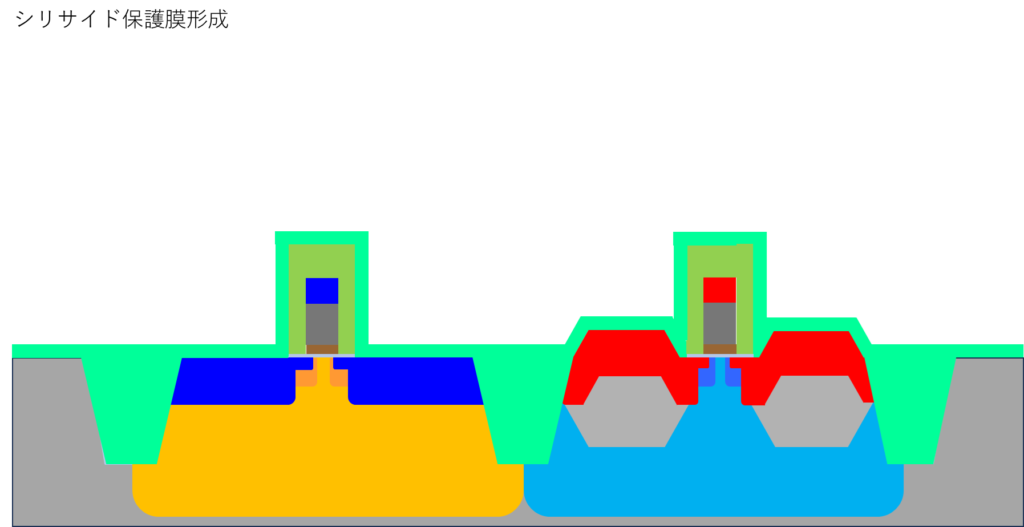

シリサイド形成プロセスでは、シリサイドを形成したい領域と形成したくない領域を分けるための保護膜を形成します。

保護膜としては、SiO2が使われていると考えられるので、全面にSiO2を成膜します。

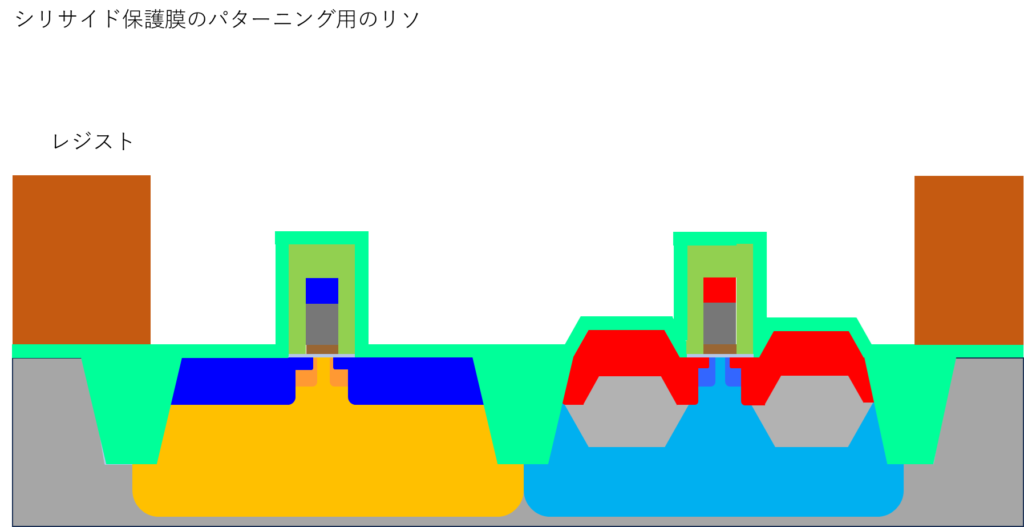

シリサイドを形成したい領域は、SiO2保護膜を取り除きたいので、シリサイドを形成したい領域だけを開口します。

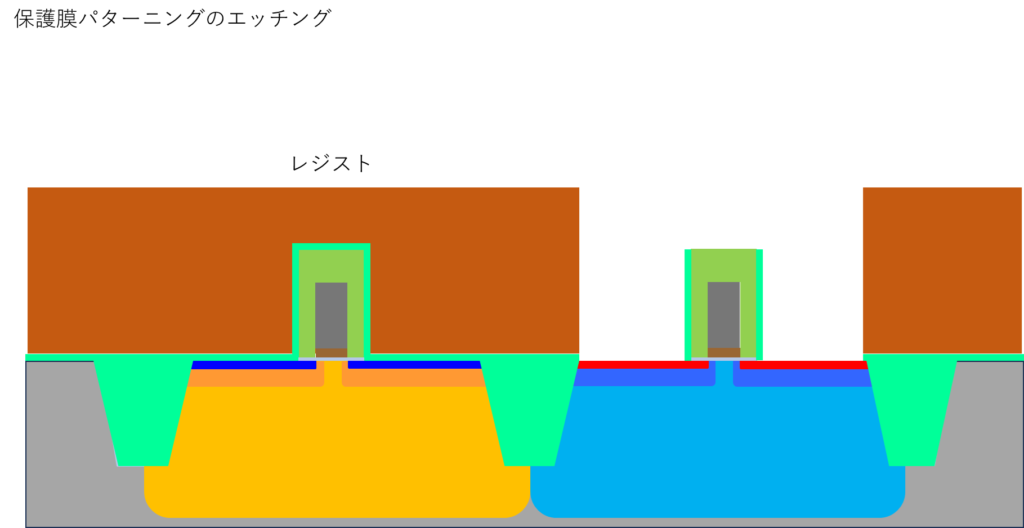

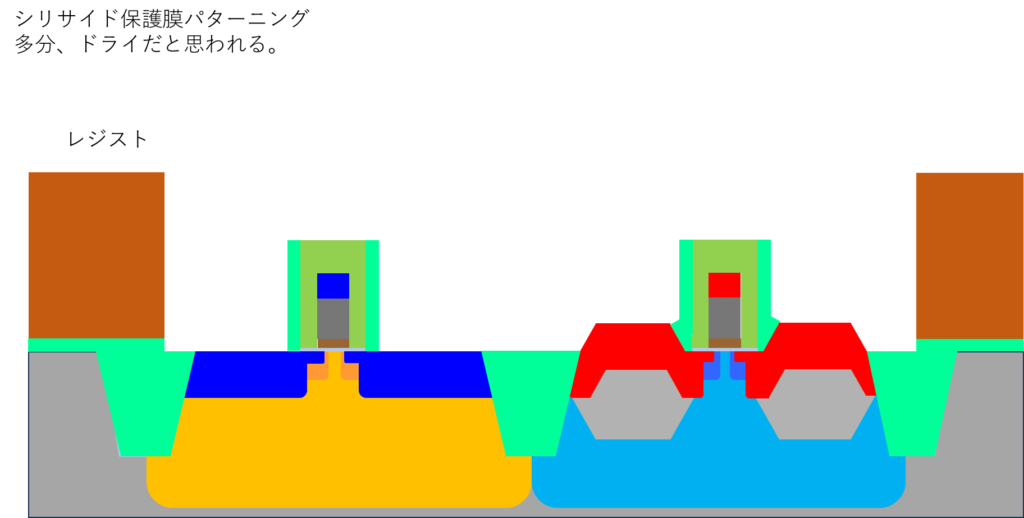

開口した領域のSiO2を除去しますが、おそらくドライエッチングで行われていると思われます。

NMOS・PMOS領域の両方でシリサイドを形成したいので、この図のトランジスタではシリサイドを形成するためにSiO2をエッチングしています。

細かい話ですが、ここでドライエッチングを使うか、ウエットエッチングを使うかで、SiO2絶縁膜の残り方が変わってきます。

レジストを除去してやると、このような断面になります。

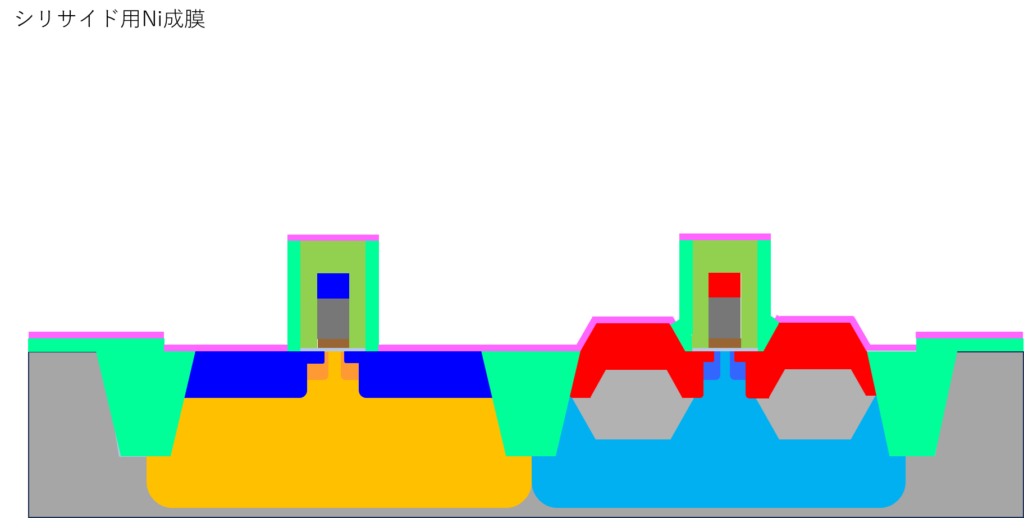

シリサイドを形成したい領域としたくない領域のパターニングができたので、Niシリサイド形成のためにNiを成膜します。

全面にNiを成膜すると、このようになります。シリサイド化の反応は、NiがSiと接触している領域のみに生じます。

絶縁膜上のNiは反応せずに残るので、Siと接触している領域をセルフアラインにシリサイド化することができるので、都合のいい反応となっています。

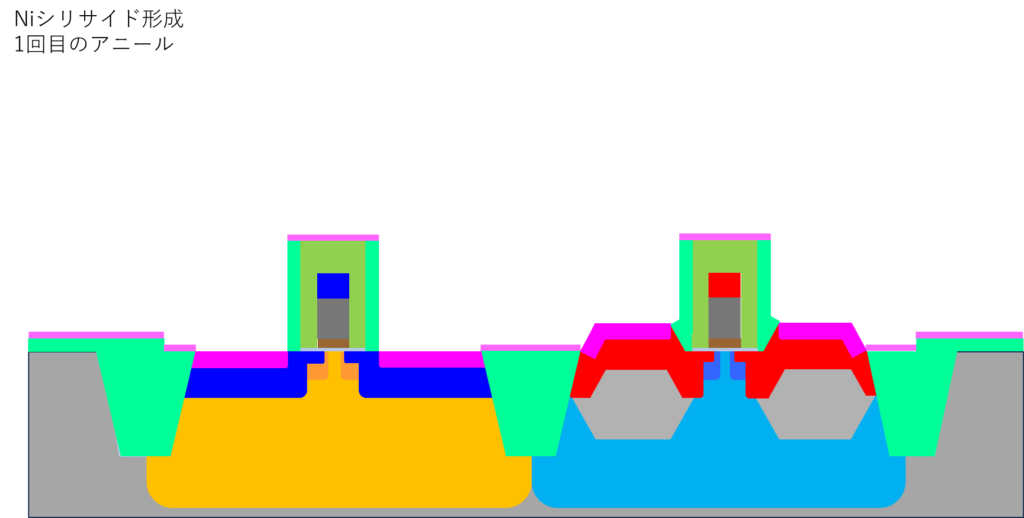

シリサイド化を行うには、熱処理が必要になります。だいたい2段階の熱処理を行うのが一般的なやり方です。

1段階目のアニールで、NiとSiが接触している領域でシリサイドを形成します。1段階目のアニール後の断面は、このようになります。

Siと接触している領域のNiは、Niシリサイドとしてシリサイド化しています。絶縁膜上のNiは、未反応のまま残っています。

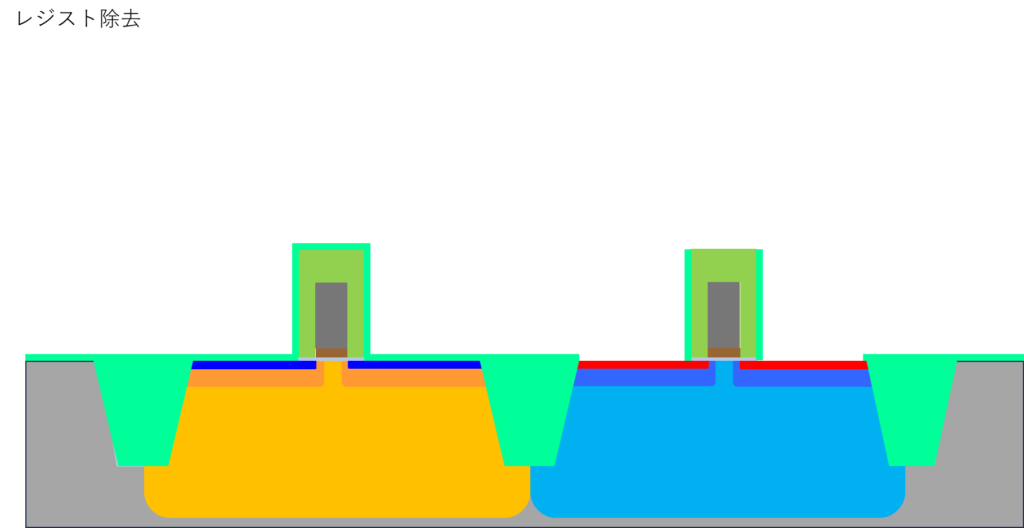

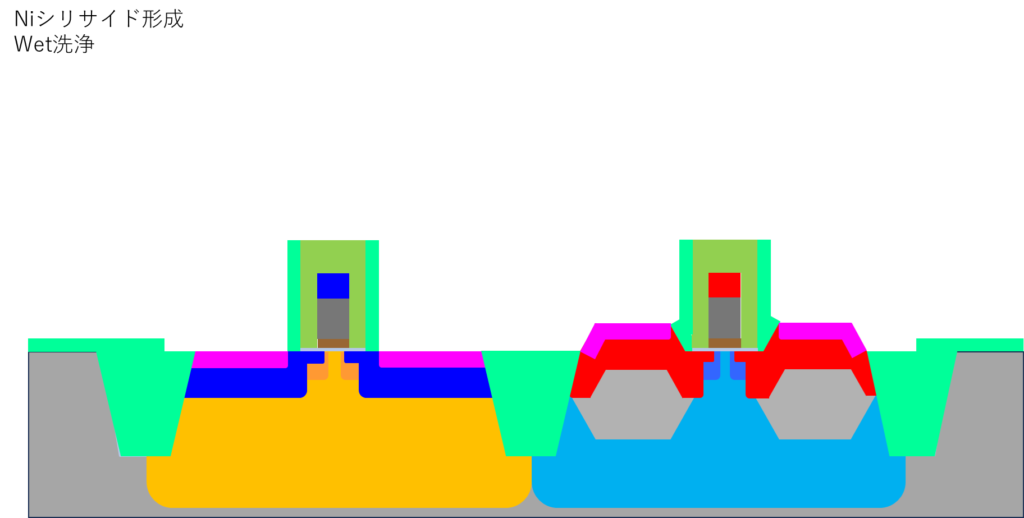

未反応のNiは除去してやる必要があるので、ウエットエッチングでNiを除去してやります。

未反応のNiを除去してやると、Niシリサイドの領域のみが残ります。

未反応のNiを除去後に、Niシリサイドを再度アニールしてやることで、このような断面になります。

ここまでで、Niシリサイド形成まで終わりました。シリサイド形成が終われば、トランジスタの形はほとんど出来上がったようなものです。

ここからは、トランジスタへのコンタクトを形成するための工程に入ります。

[da01]

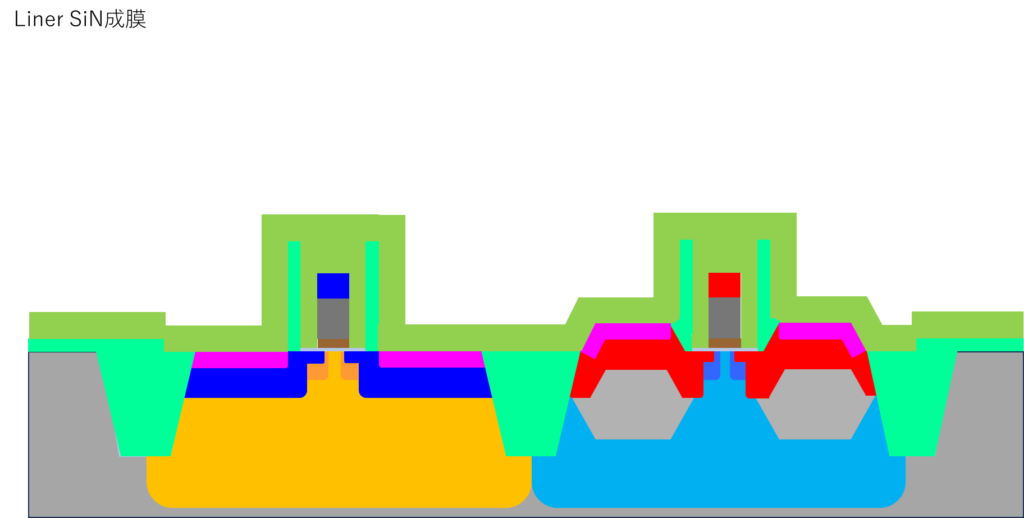

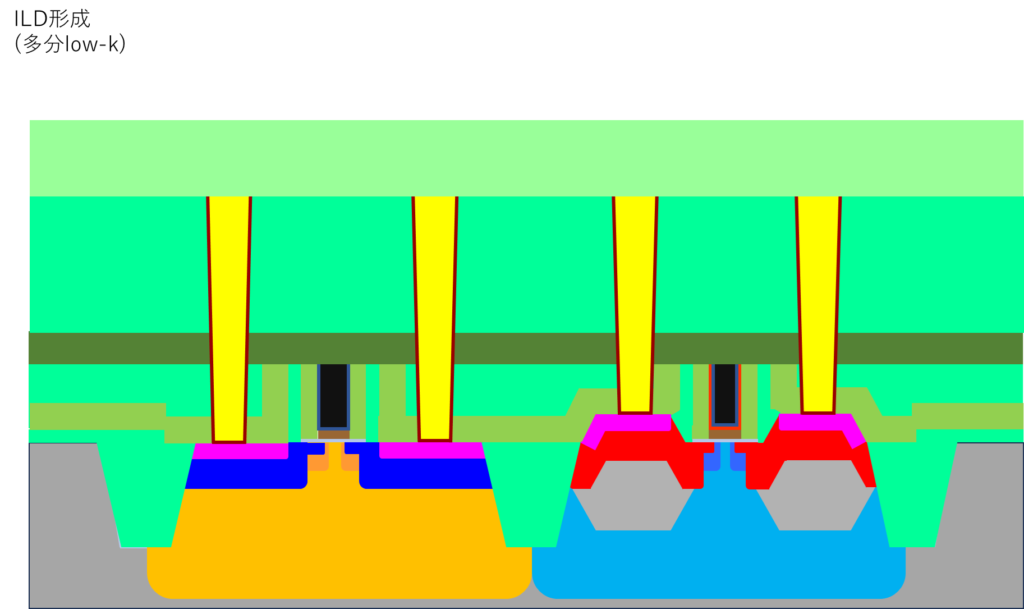

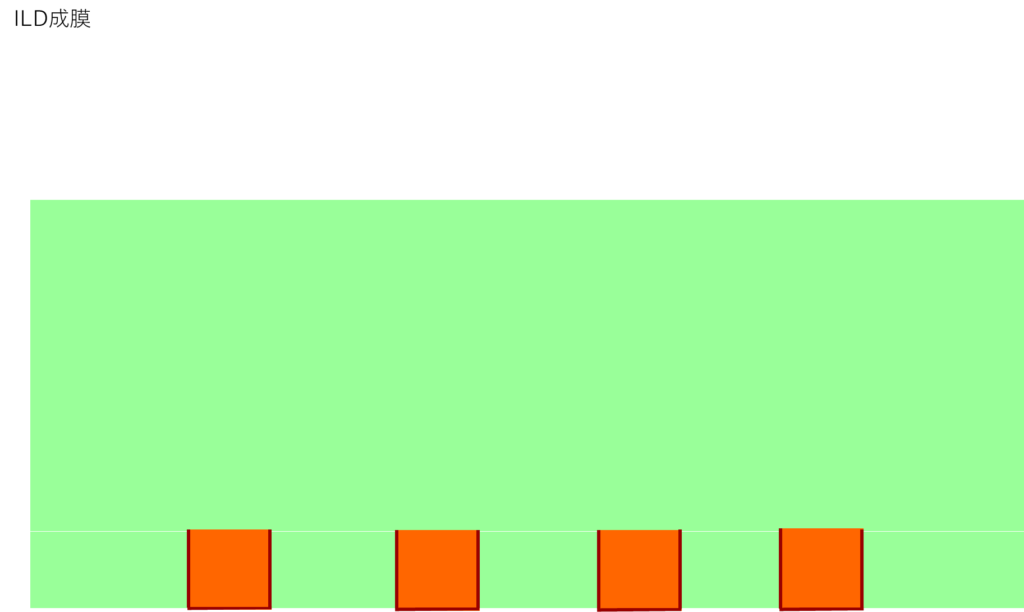

8:ILD成膜

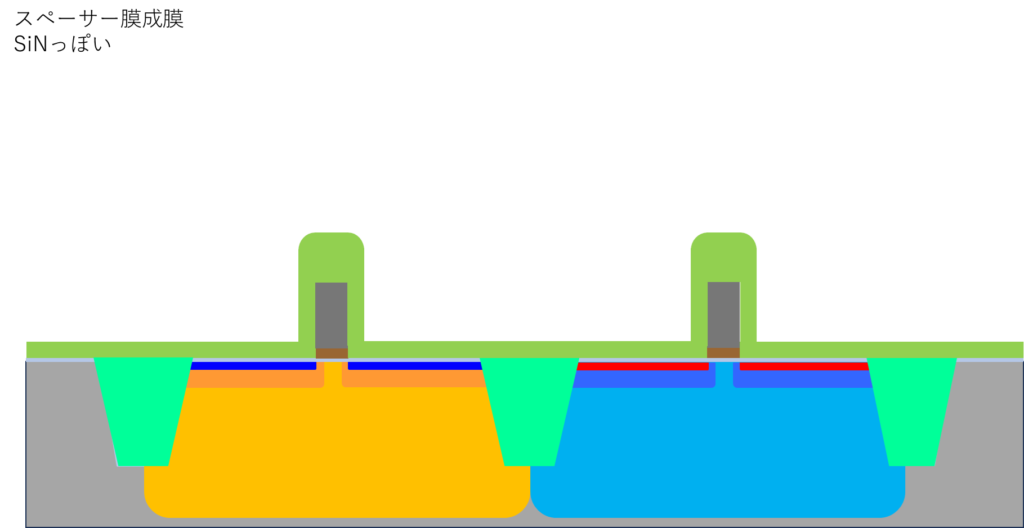

シリサイドが形成できたら、次はLiner SiNを成膜します。

このSiNの目的は2つあり、トランジスタへの歪み印加と、コンタクト形成時のエッチストップレイヤです。

SiNは、成膜条件によって引っ張り歪みを掛けられるもの(Tensile Stress Liner)と、圧縮歪みを掛けられるもの(Compressive Stress Liner)の2種類があります。

PMOSには、SiGe領域で一軸圧縮歪みを掛けていますが、NMOSでは引っ張り歪みを掛けると電子の移動度が上がることが知られています。

NMOSには引っ張り歪みを、PMOSには圧縮歪みを掛けるとそれぞれのキャリアの移動度を上げられます。

おそらく、NMOSにはTensile Stress Liner SiNが使われていると思われるんですが、今回は単純なLiner-SiNの形で図を作っています。

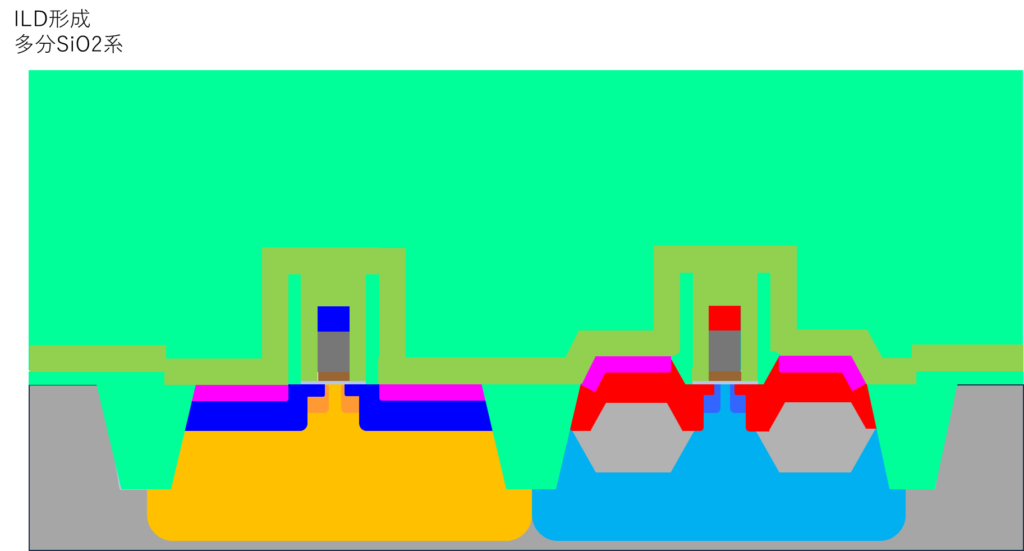

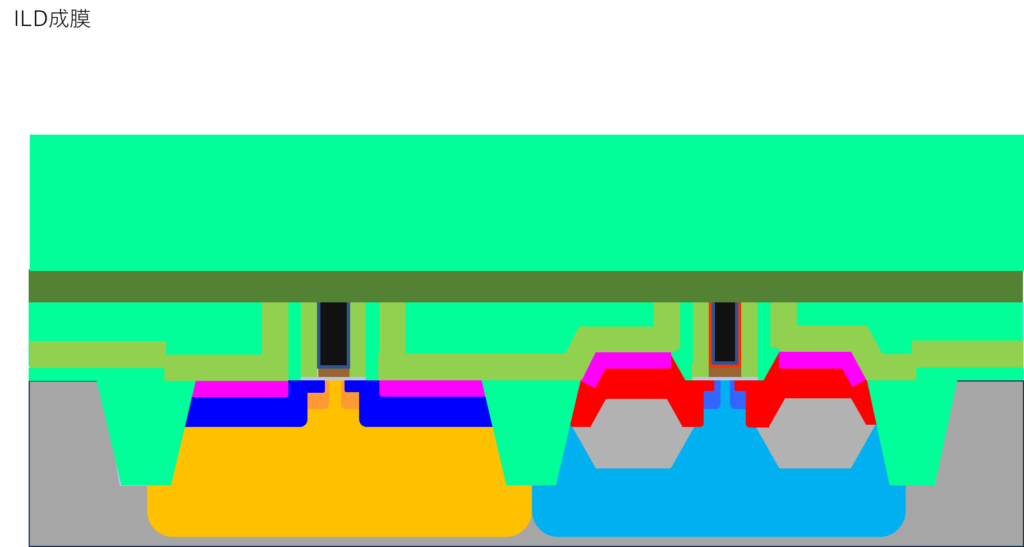

そして、平坦化のためにILDを成膜します。

おそらくSiO2系の絶縁膜だと考えられます。

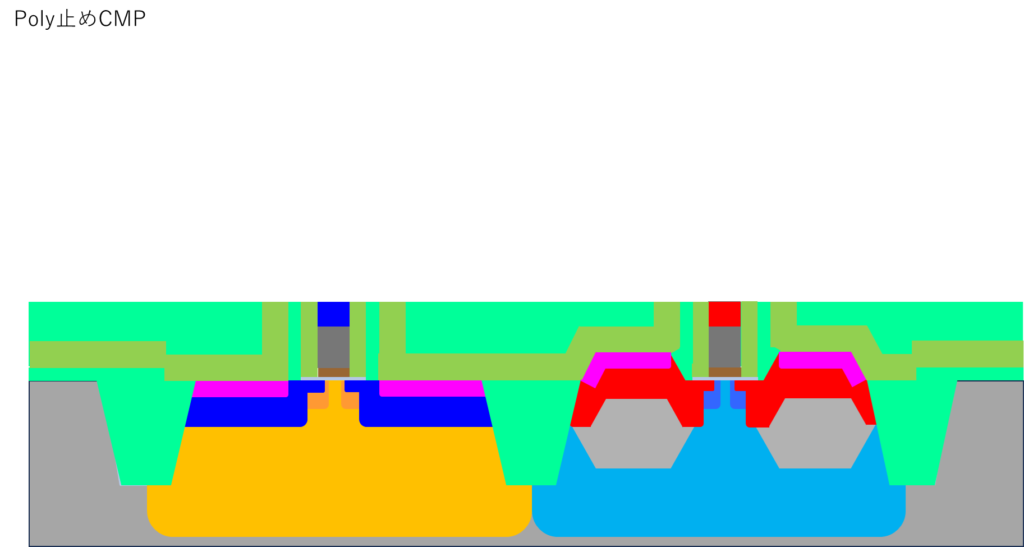

このあと、Dummy Gateのpoly-Siを金属に置き換えるために、ゲートのpoly-Siを抜く必要があります。

ゲート領域のみに穴をあけてやる必要が出てきます。

ではどうしたらいいのかというと、ゲートの頭止めでCMPを掛けてやります。

SiNの部分は、ドライエッチングで切っているかもしれませんが、CMPしてやることでゲート領域のみを露出することができました。

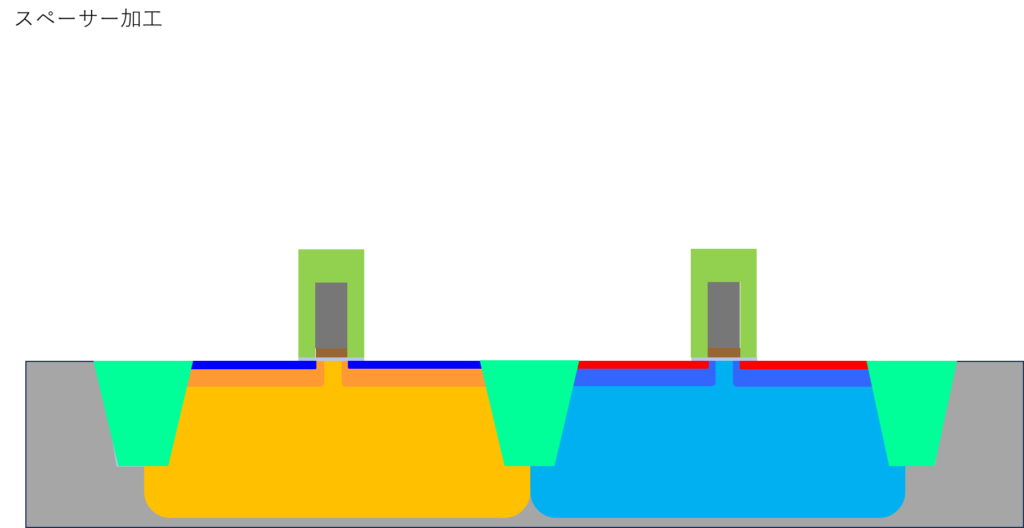

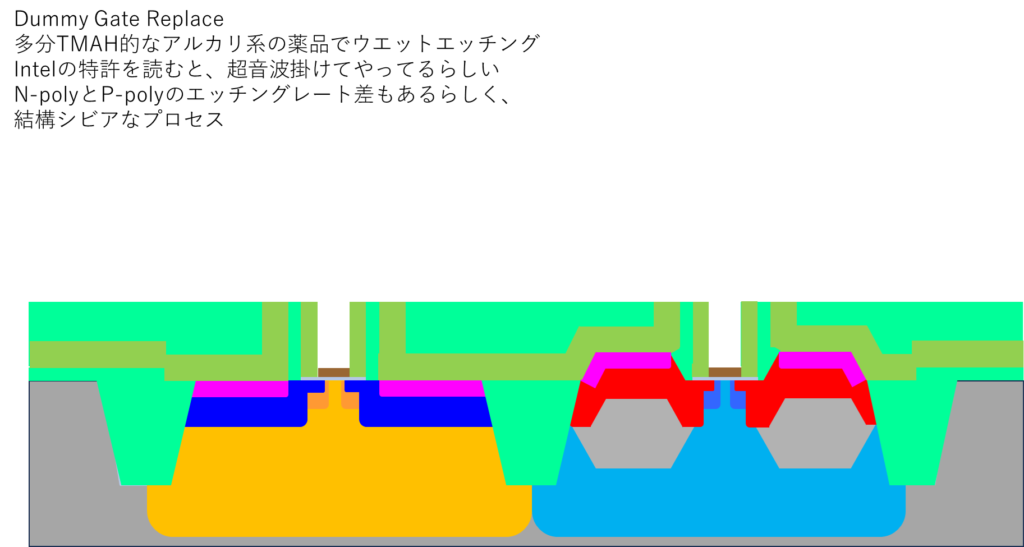

9:Dummy Gateリプレイス

さて、ゲートのpoly-Siが露出したので、ここからDummy Gateのリプレイスを行います。

具体的にどんな薬液が使われているのかは書かれていませんが、アルカリ系の薬品でウエットエッチングしているようです。

Intelの特許を見ると、アルカリ系の薬品で超音波を掛けながらエッチングすると良いという記述がありました。

この時、エッチングするのをpoly-Siだけにとどめておくのが重要です。High-k絶縁膜止めでエッチングしてやらないと、チャネル部のSi基板もエッチングされてしまいます。

また、エッチングするpoly-SiはN型polyとP型polyになっているので、P/Nによるエッチングレート差もあるようです。

この辺のDummy Gateのエッチングは、うまくできるエッチング条件があるんだと思われます。結構シビアなプロセスです。

ここで、Dummy Gateをエッチングするのが、45nmのゲートラストのプロセスの中でもハイライトです。

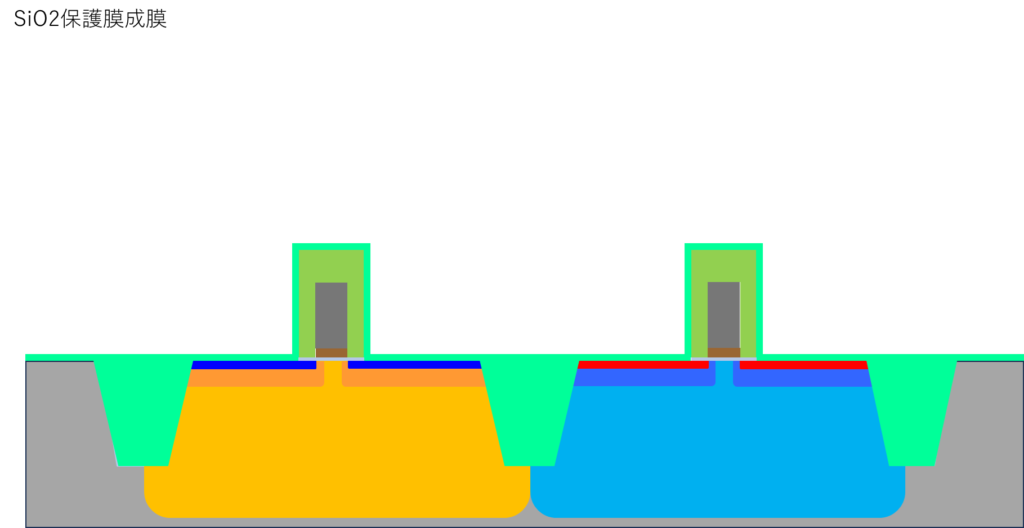

10:Gate Stack形成

Dummy Gateを抜くことができたので、改めてGate Stack構造を作っていきます。

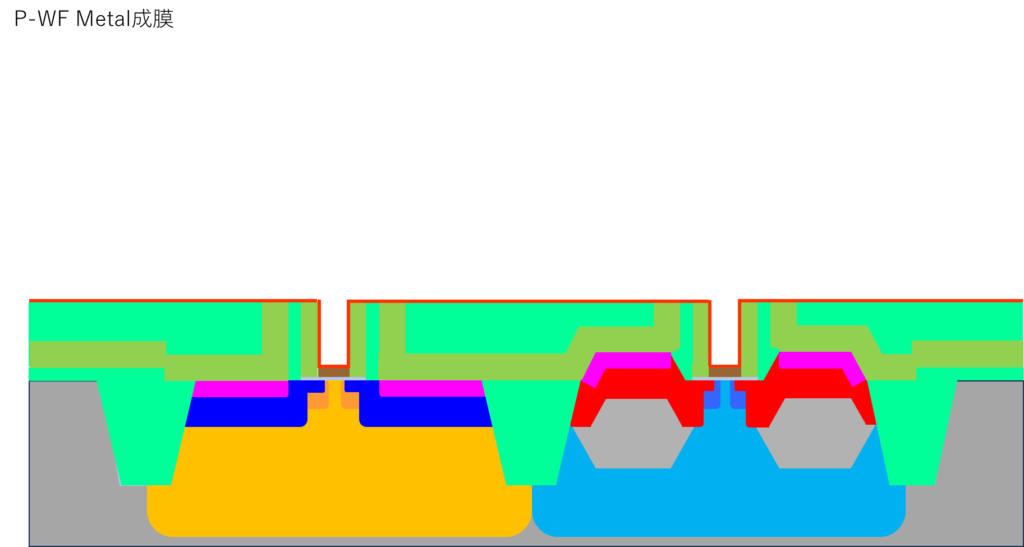

最初に、P型のWork Function Metal(WF-M)を形成します。

ここで、WF-Mが出てくるのは唐突ですが、High-k絶縁膜を適用してゲートラスト構造を取らなければいけなくなった理由に直結しています。

理由を書き出すと長くなるので、この記事ではそんなもんなんだと思ってください。詳しくは別記事で書く予定です。

ゲートラストプロセスだと、P型・N型それぞれで、別のWF-Mを使っています。

P型のWF-Mを成膜すると、このようになります。

P型のWF-Mは、全面に成膜されます。

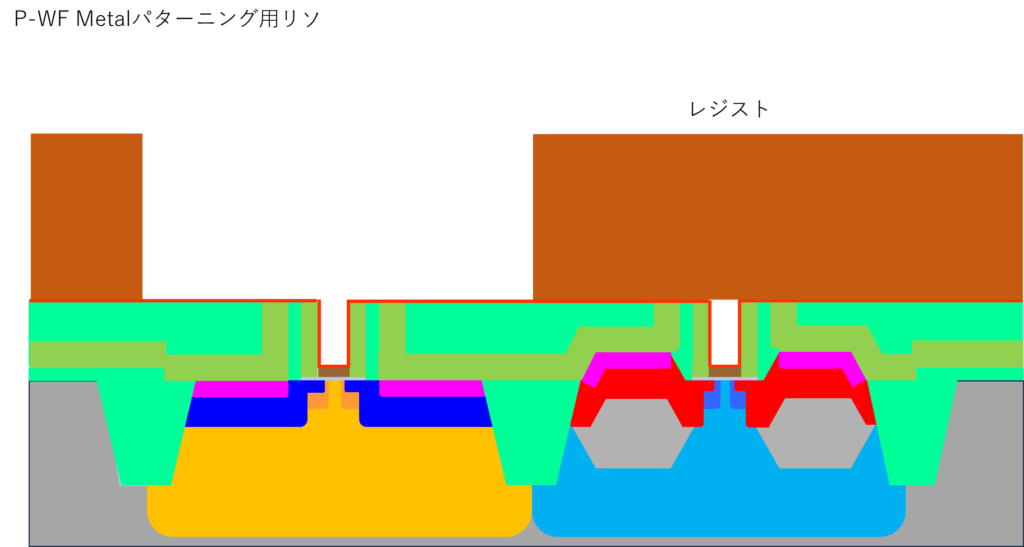

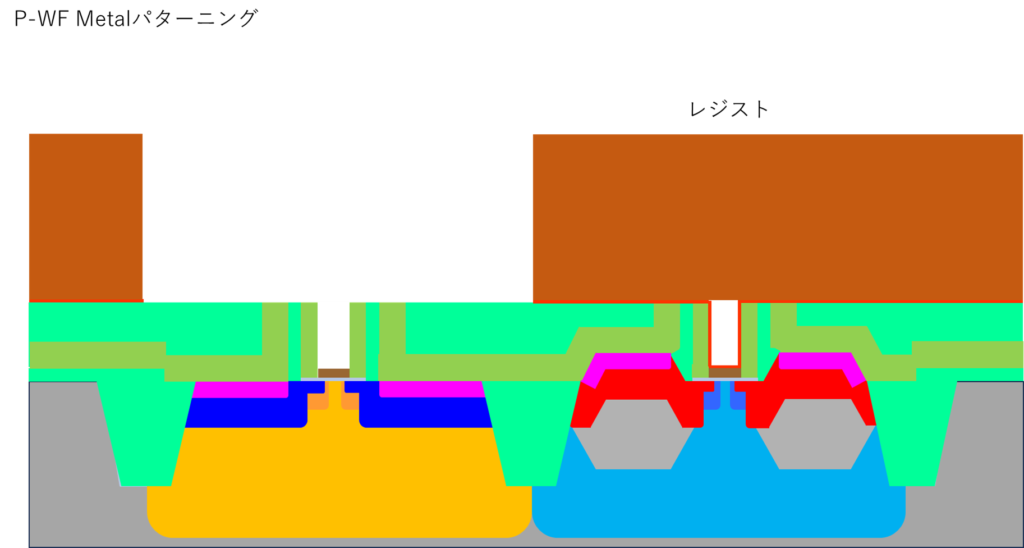

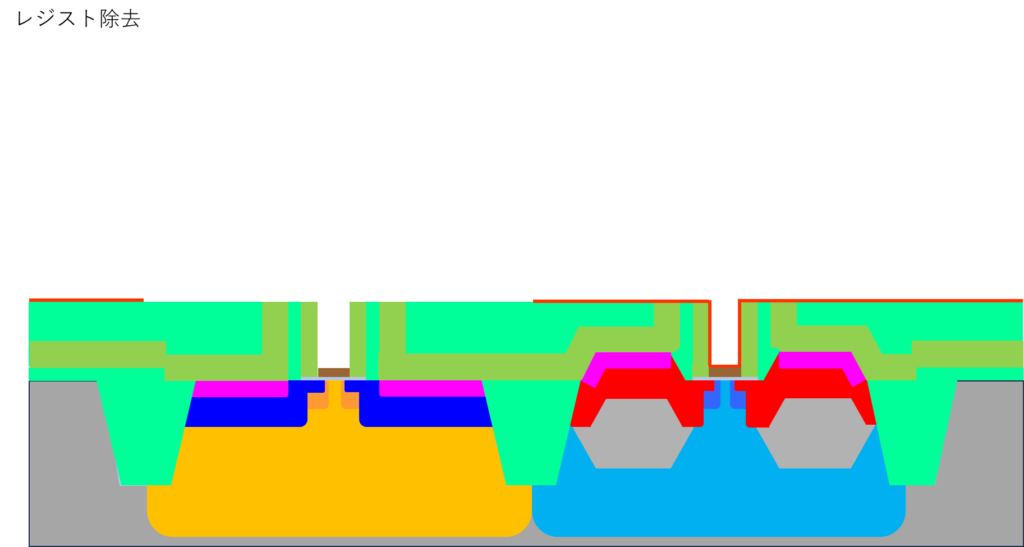

NMOSには、別のWF-Mをつけるので、N型領域についているP型のWF-Mを除去するためにリソグラフィーを行います。

ウエットエッチングでP型のWF-Mを取り除くとこのようになります。

レジストを除去してやると、P型領域にはP型のWF-Mが、N型領域はWF-Mがついていない構造になります。

P型のWF-Mを先に付けているのは、ウエットエッチングで処理しやすい材料だからだと考えられます。

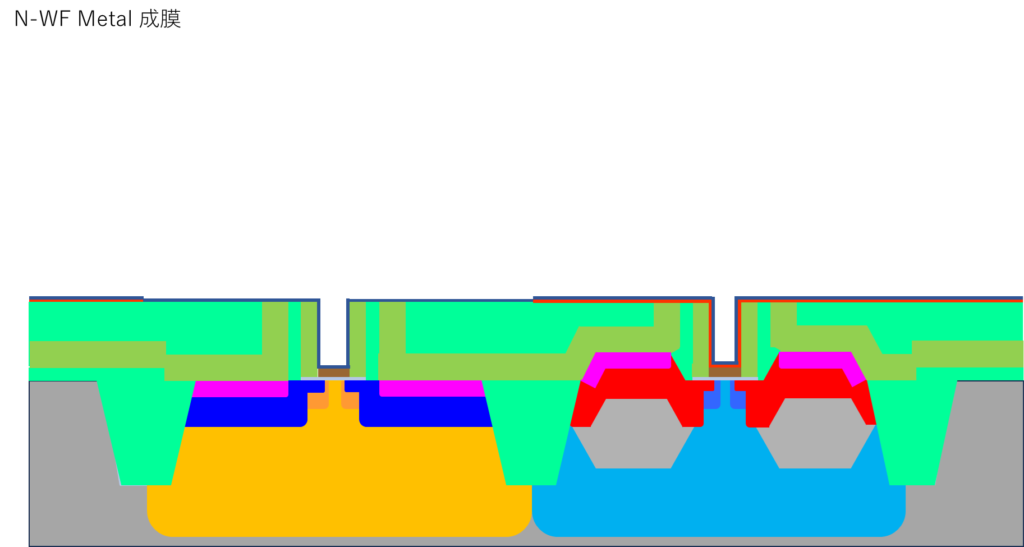

続いて、N型のWF-Mを成膜します。

WF-Mは、High-k絶縁膜に接触している金属の種類が重要なので、P型のWF-Mの上にN型のWF-Mがついていても特に問題ありません。

なので、N型のWF-Mの成膜後は特にエッチングはしません。

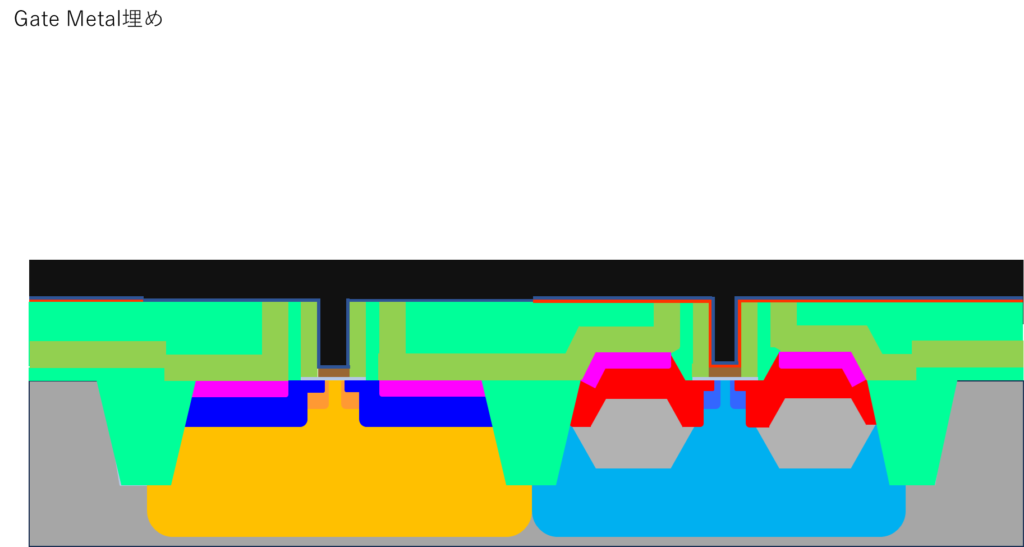

そして、Gate領域を導電性の良い金属で埋め込みます。どうも、Cuとかではなく、Alのような金属が使われているようです。(Intelの特許を見た感じの話なので、実際には違う金属かもしれません。)

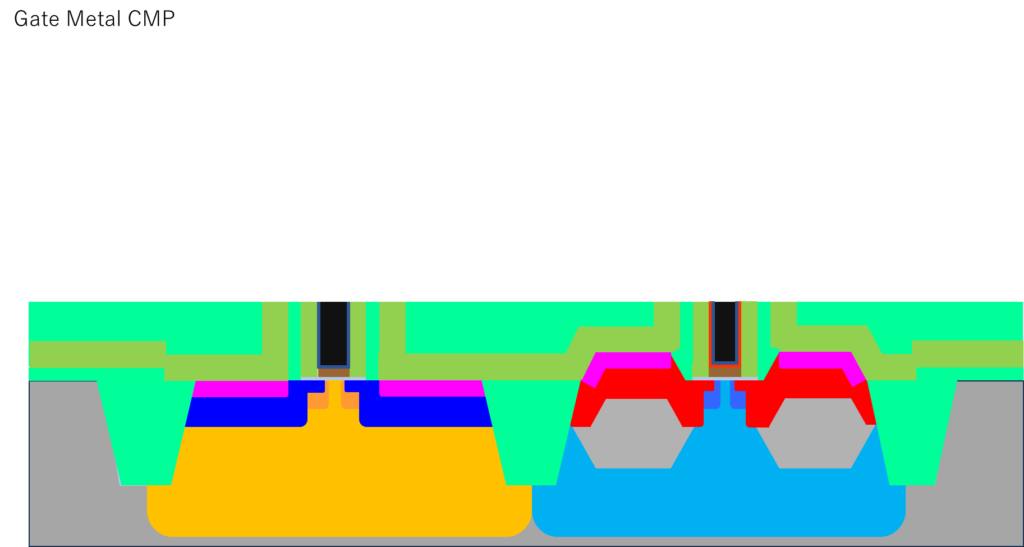

そして、Gate MetalをCMPして埋め込んでやると、このようになります。

やっとこれで、ゲートラストプロセスの山場である、Dummy Gateのリプレイスおよびゲートスタックの形成が終わりました。

ここからは、形成したトランジスタに対して配線をつなげる工程に入ります。

11:コンタクトプラグ形成

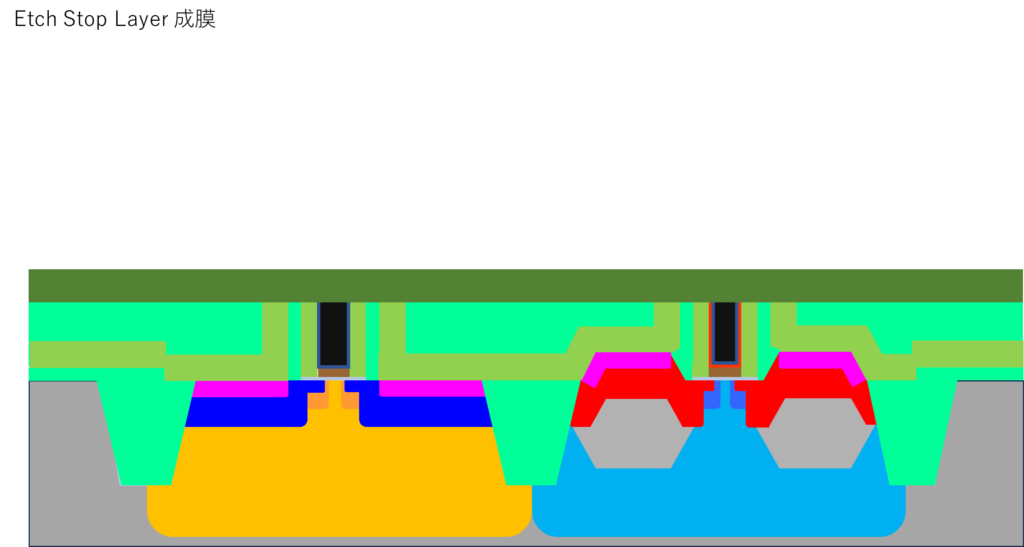

Gate Stackの形成が終わったので、層間膜を形成しコンタクトプラグを形成します。

まず、金属ゲートの上に、Etch stop Layerを成膜します。(材質までわからなかったです)

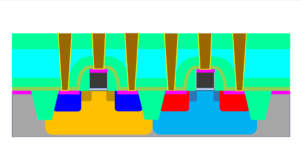

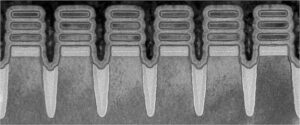

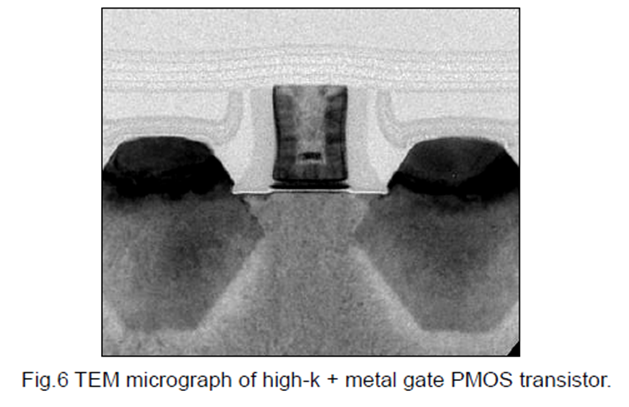

ここまできたので、2007年にIntelがIEDMで発表したPMOSの断面写真と比べてみましょう。

A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon,9 Cu Interconnect Layers, 193nm Dry P atterning, and 100% Pb-free Packaging

(IEDM 2007でのIntelの発表)より引用

この記事は、IntelがIEDMで発表した論文のプロセスと写真と、Intelの特許からデータを引っ張って作っています。

当たらずも遠からず、くらいの断面になっているのではないかと思います。

構造を描くうえで、色々悩んだ部分はありますが、それなりのものにはなっているのではないかと思います。

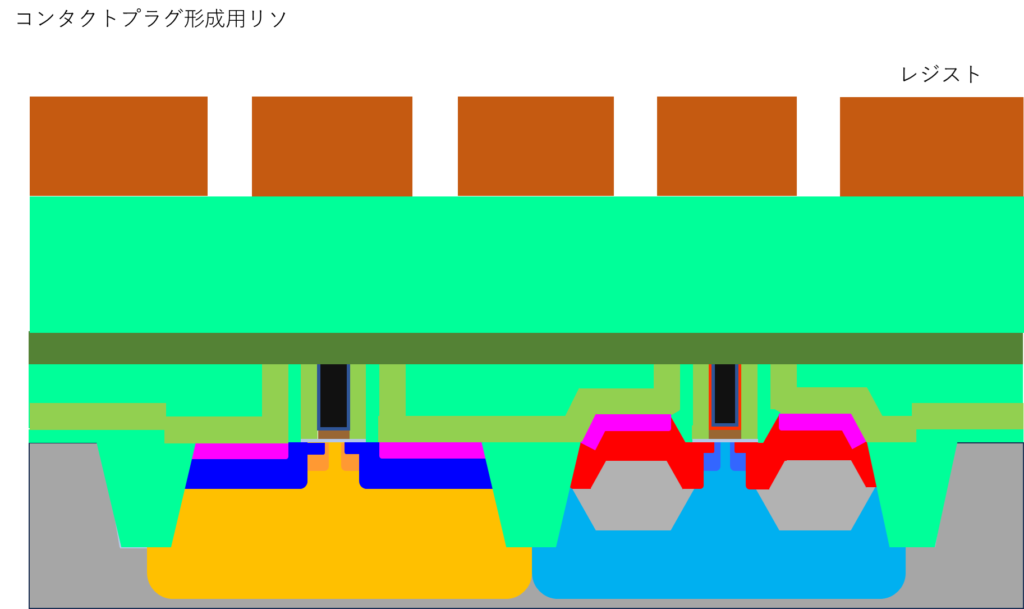

さて、層間膜を形成してコンタクトプラグを作っていきましょう。

層間膜を形成して、コンタクトプラグを作っていきます。おそらく、コンタクトプラグはTi/TiNのバリアメタルとWになっているようです。

コンタクト形成用のリソグラフィーを行います。穴をあけたい領域だけ開口する形になります。

開口した穴の形に合わせてコンタクトプラグ用の穴をエッチングすると、このようになります。

図では、端折っていますが、上からエッチングしていき、Etch Stop Layerで一度止めて、Etch Stop Layerの加工ステップが入り、SiO2の加工ステップが入り、最後にLiner SiNの加工が入ると思われます。

NMOSとPMOSで、コンタクトプラグを落とす高さがずれているので、Liner SiN層で高さの差を吸収するようにしているのでしょう。

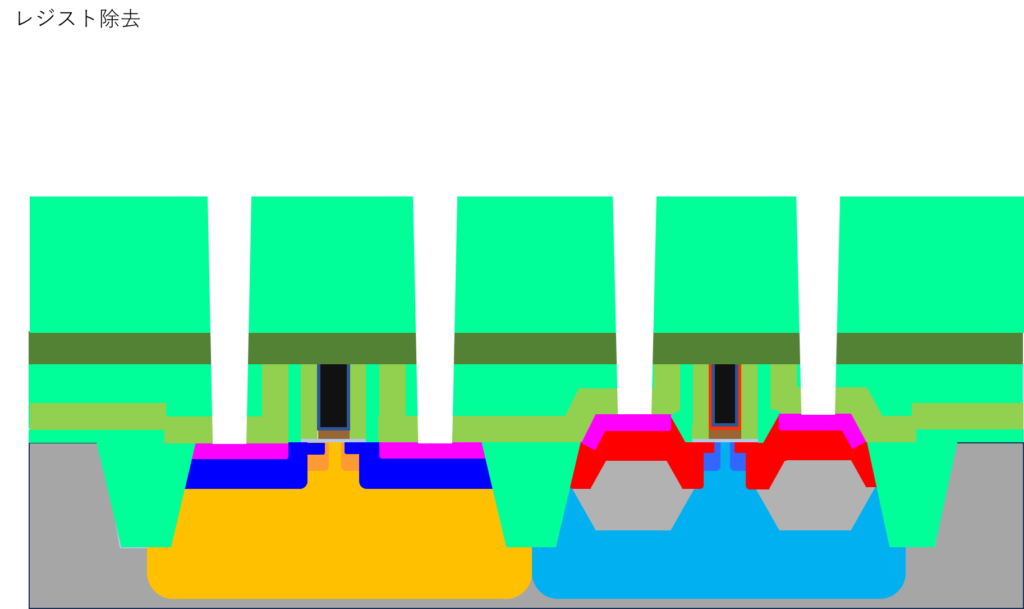

コンタクトプラグの加工後にレジストを除去してやると、こんな断面になります。

ここまでくると、それっぽくなってきましたね。

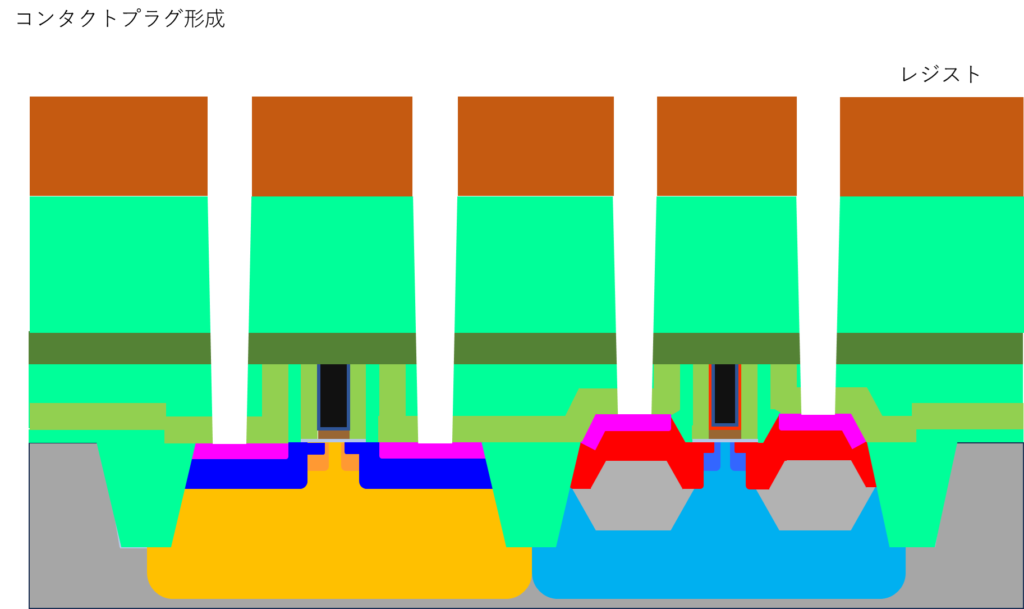

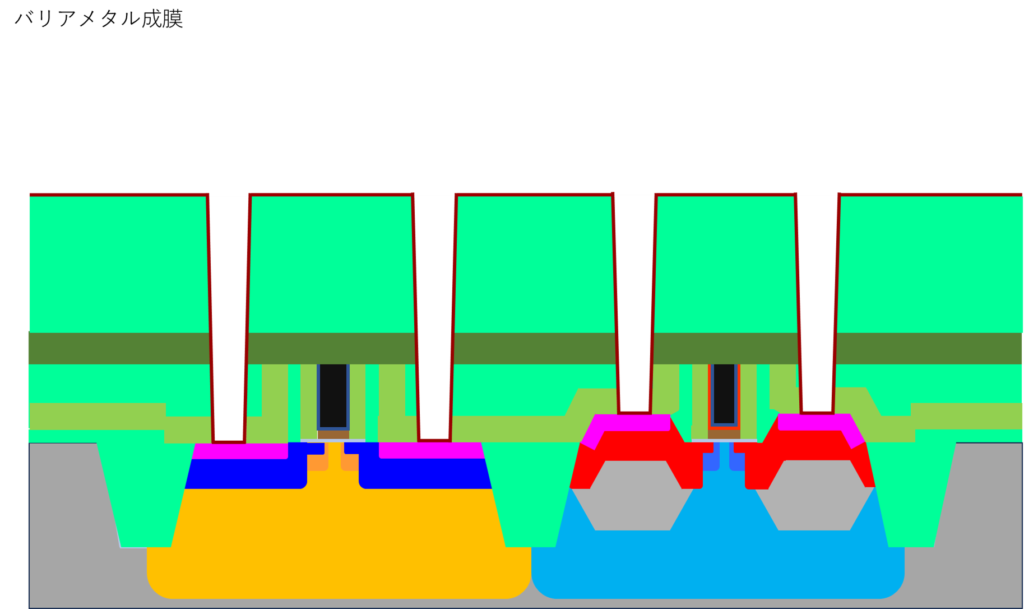

コンタクトプラグの中を、金属で埋めていきます。W配線だと、バリアメタルはTi/TiNになると思われます。

まず、バリアメタルを成膜してやります。

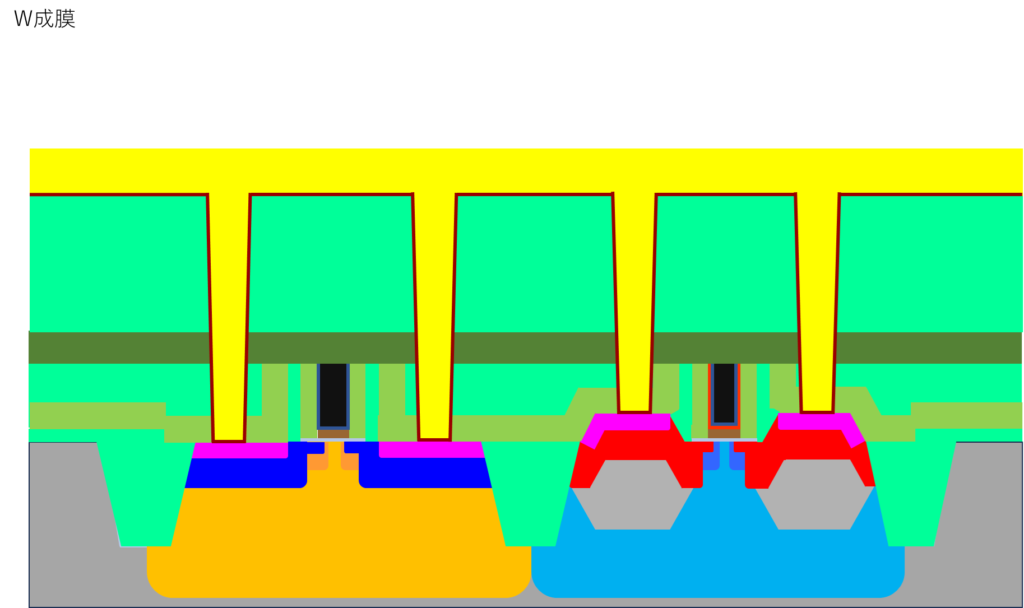

バリアメタルが成膜できたら、Wを埋めていきます。

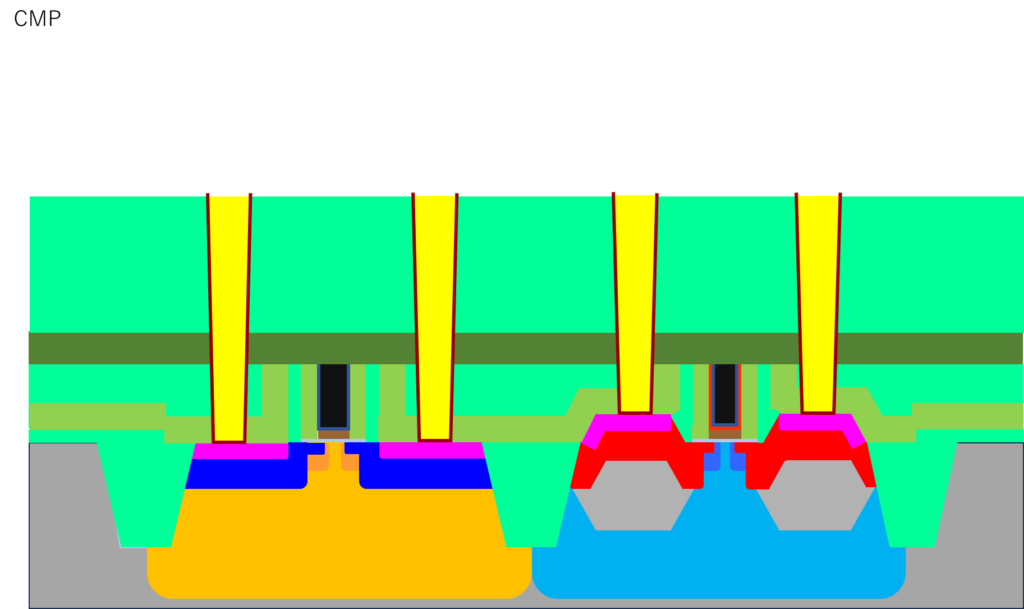

そして、CMPを掛けてやれば、コンタクトプラグが完成します。

これでコンタクトプラグまで作れたので、あとは配線工程になります。

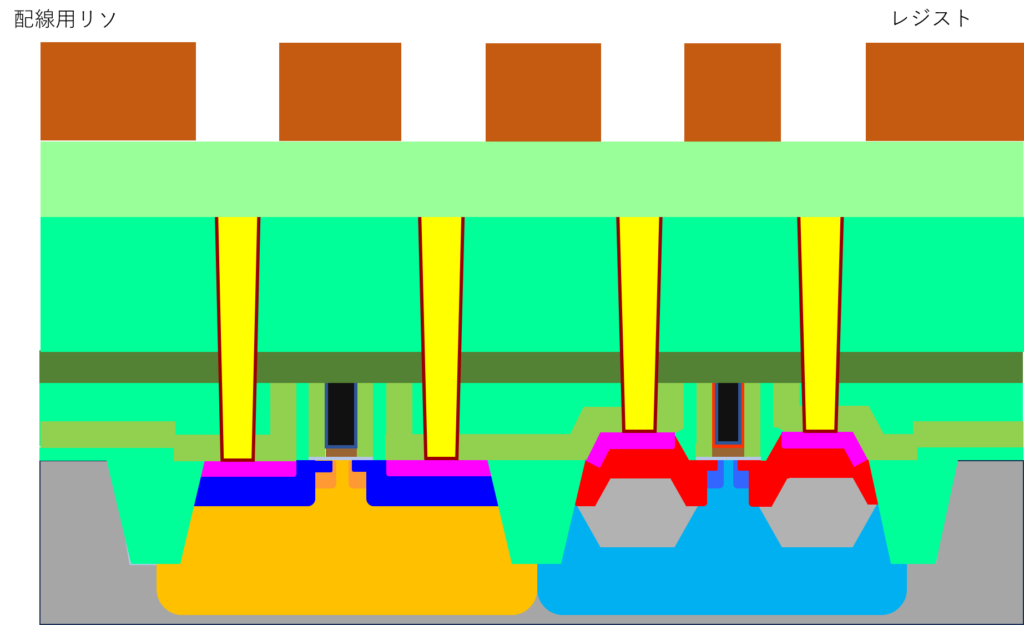

12:配線+Via形成

配線工程は、基本的に絶縁膜を成膜して、Viaと配線を加工して、Cuで埋めることの繰り返しです。

Cuシングルダマシンとデュアルダマシンのプロセスを取り上げて、あとは繰り返しなので省略します。

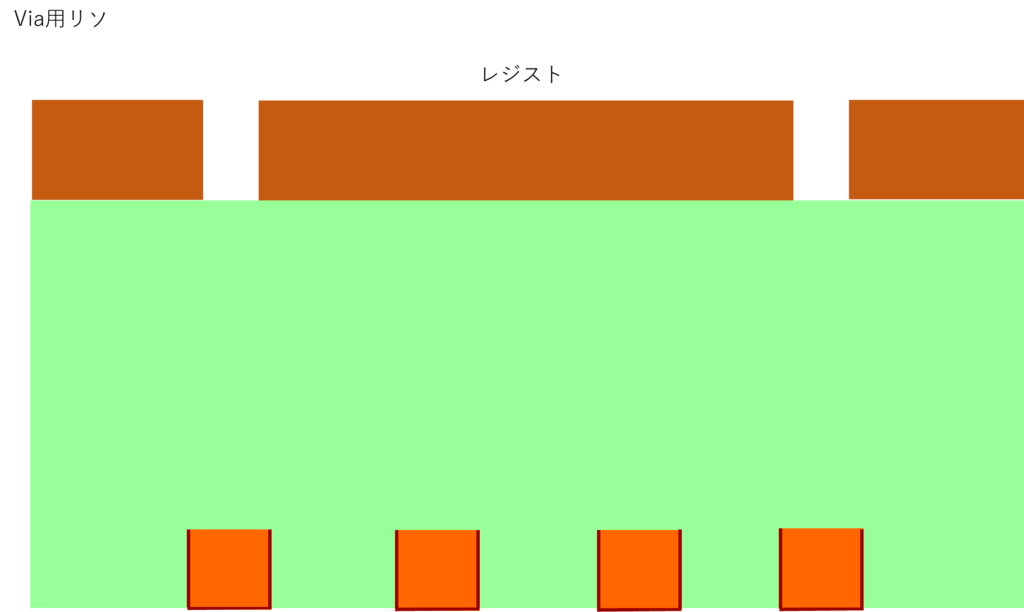

まずは、コンタクトプラグ形成後の層にILDを成膜します。Cu配線なので、Low-k膜かもしれません。

ゲート絶縁膜にはHigh-k材料を使ったのに、今度はlow-k材料かよと思われた方もいらっしゃるかもしれません。

配線層には、low-k材料が必要になります。配線同士の間隔が狭くなると、配線間に寄生容量が発生します。キャパシタの容量は、「誘電率」と「配線間の距離の逆数」に比例します。

配線間の距離を広げられないのであれば、配線間の絶縁膜の誘電率を下げる必要があります。そこで、誘電率が低い材料(low-k材料)を使う必要が出てきたということです。

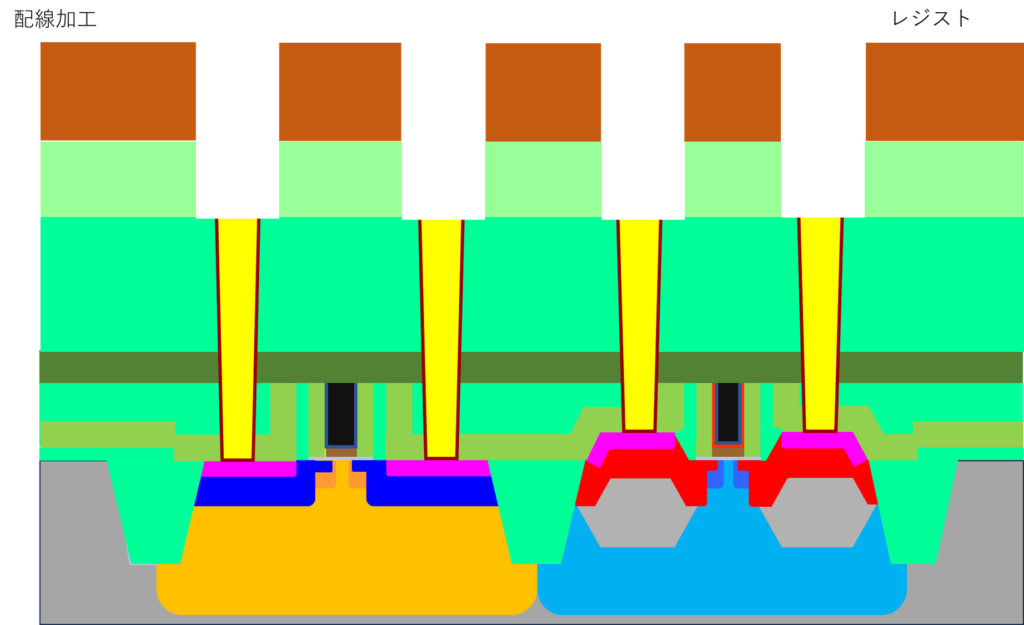

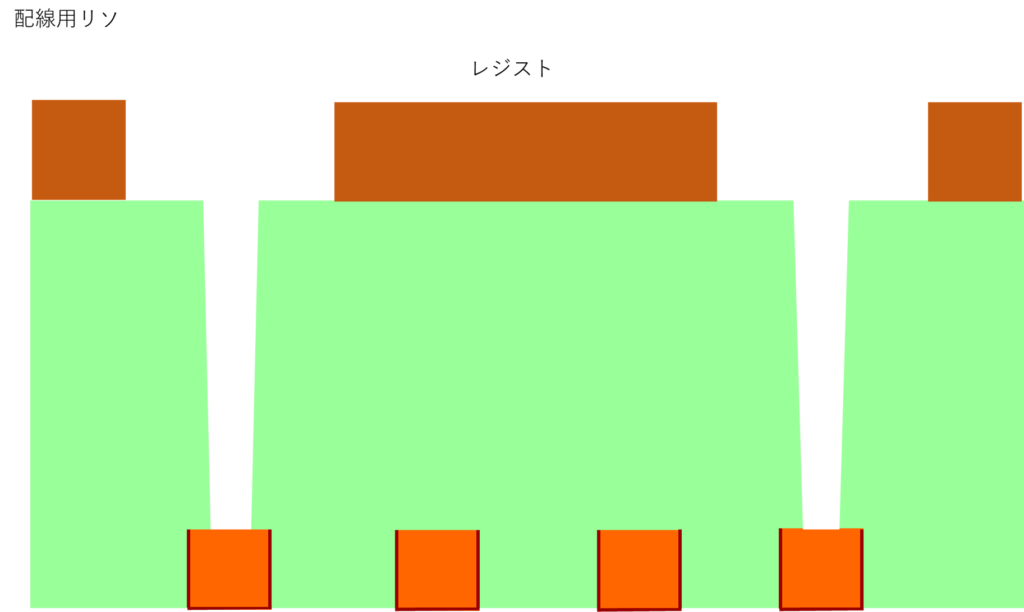

配線用の加工をするために、リソグラフィーを行います。

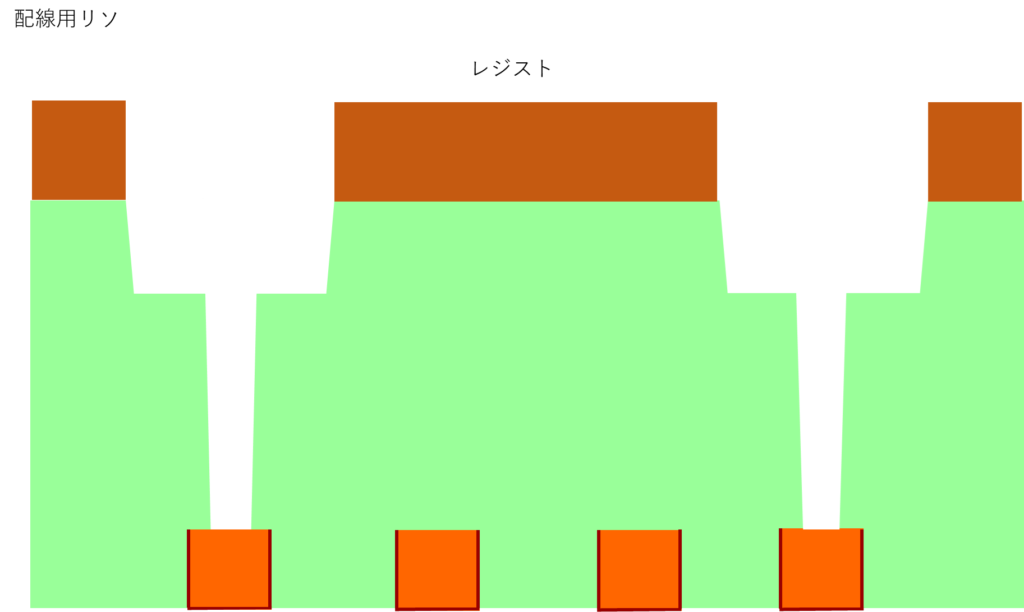

レジストの開口に合わせて、ドライエッチングを行うとこのようになります。

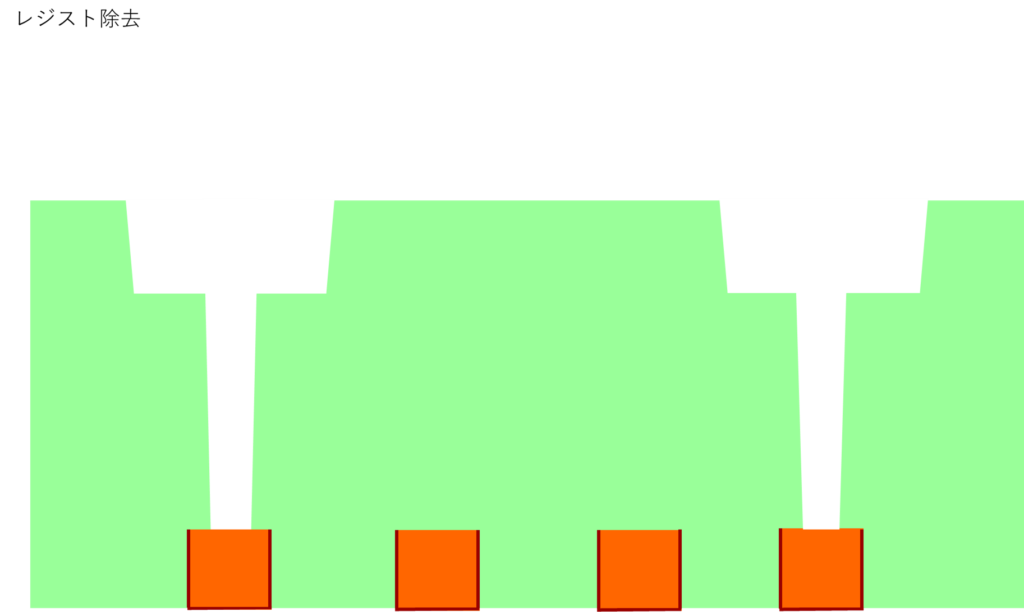

レジストを除去してやると、配線の溝ができました。

この配線層は、Cuシングルダマシンプロセスで作られていると思われるので、シングルダマシンのプロセスを見ていきます。

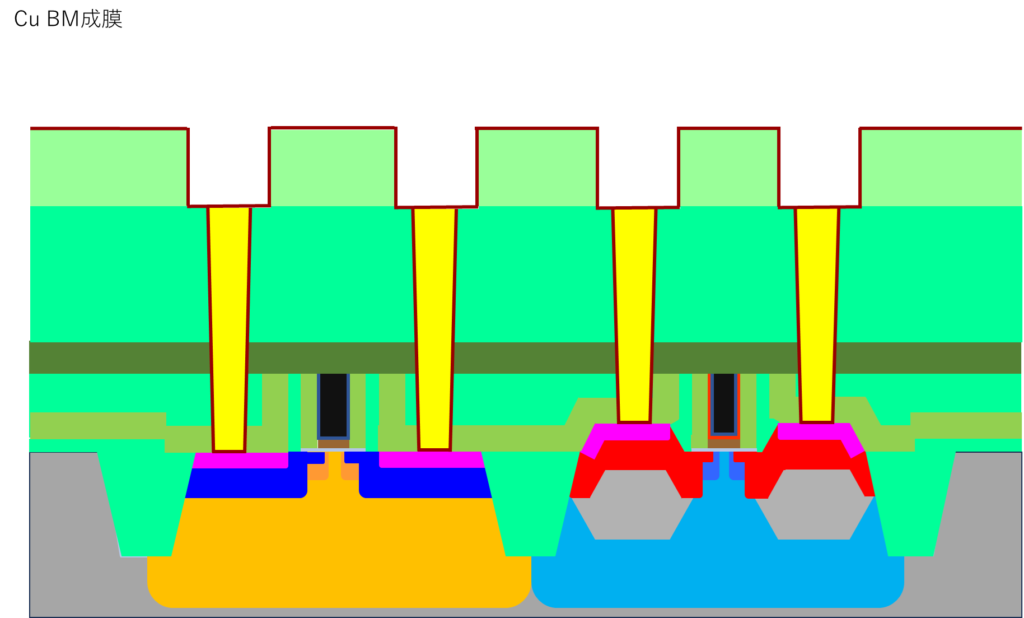

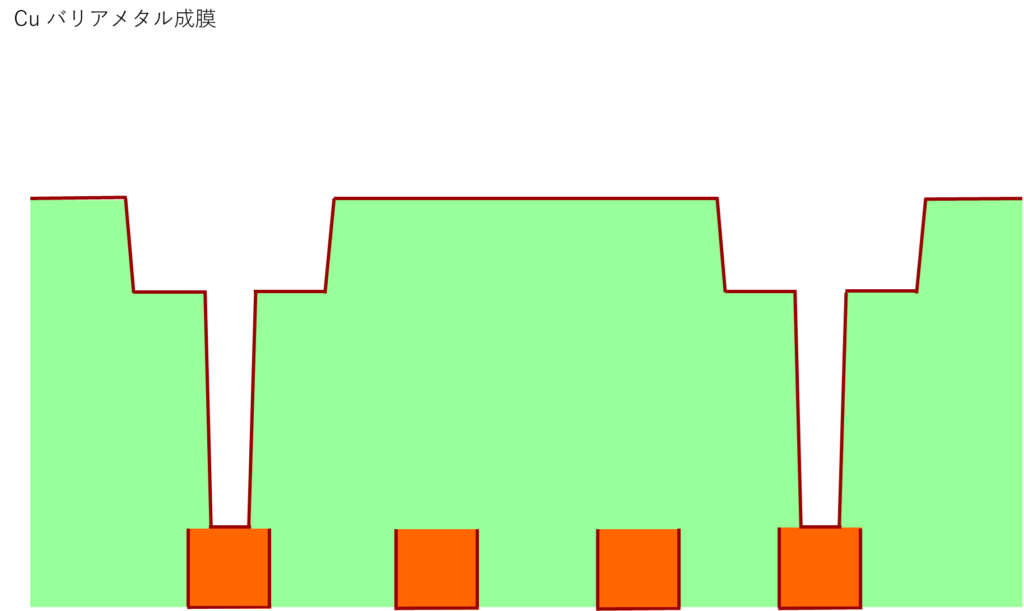

配線用に作った溝に対して、Cuを埋め込んでいくわけですが、まずはバリアメタルをつける必要があります。

Cuは、SiO2での拡散速度が速いので、バリアメタルをつけてやらないと、配線の外側に拡散していってしまいます。

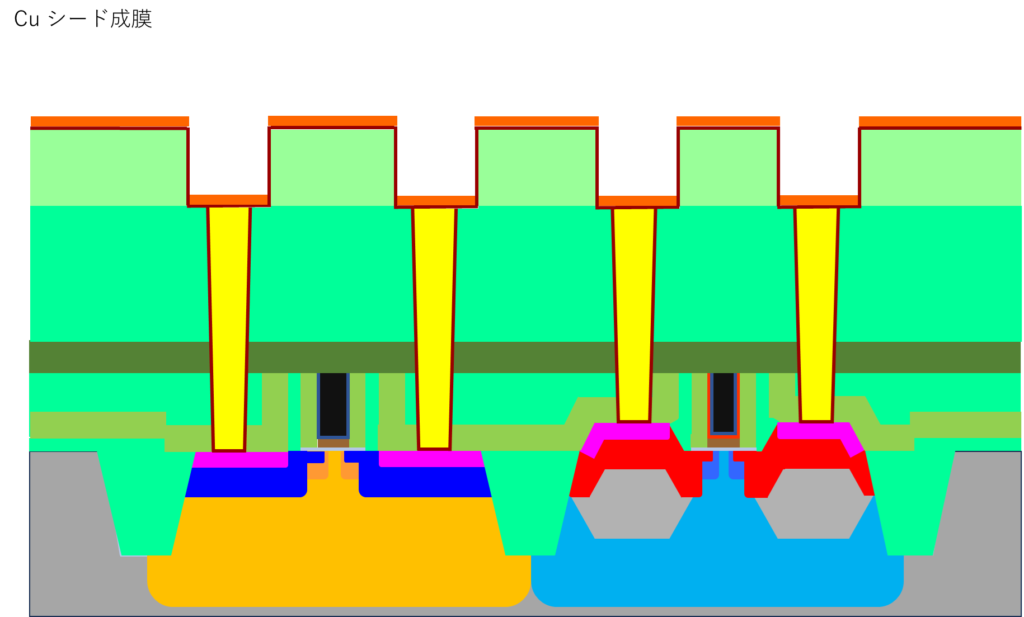

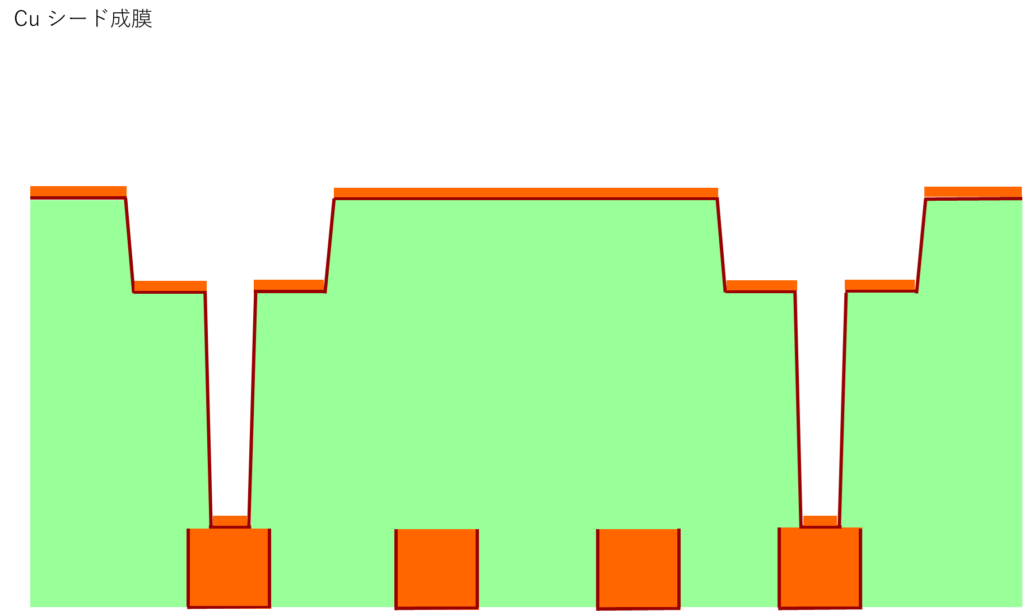

バリアメタルを成膜したあと、Cuのシード層を成膜します。

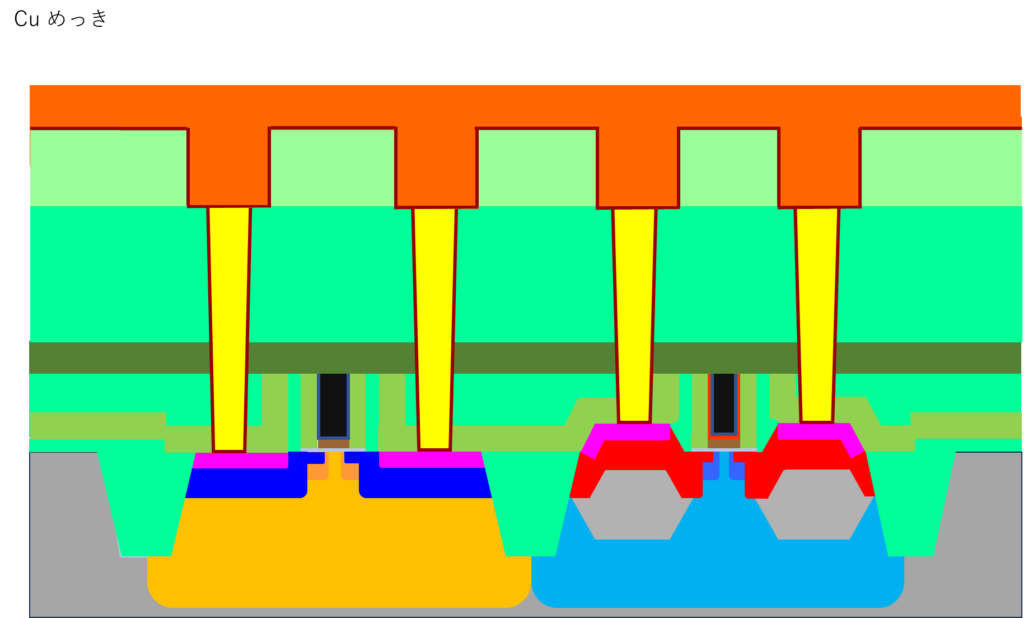

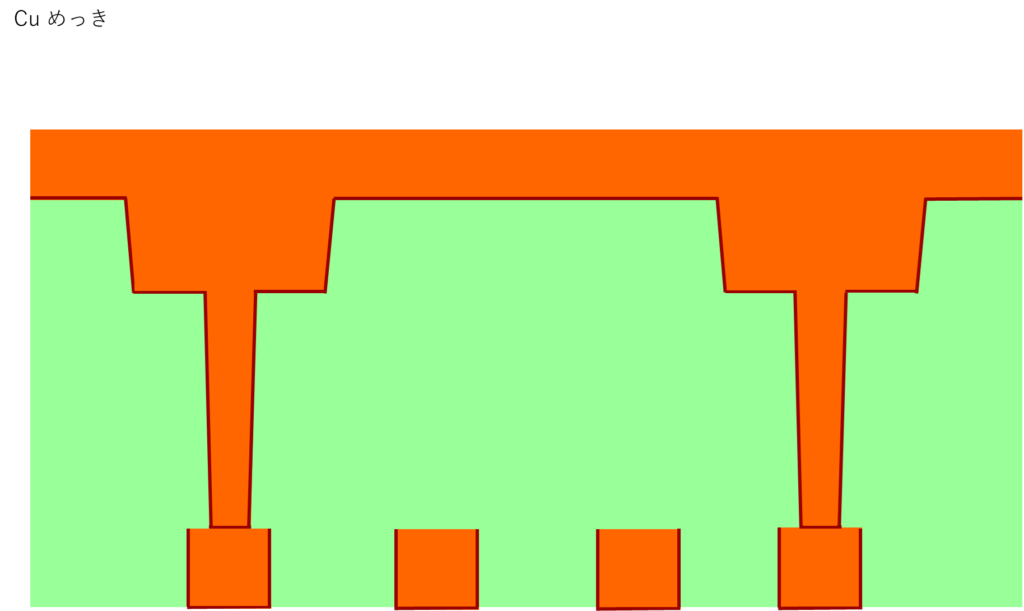

シード層が形成できたら、シード層を種にCuをめっきしていきます。

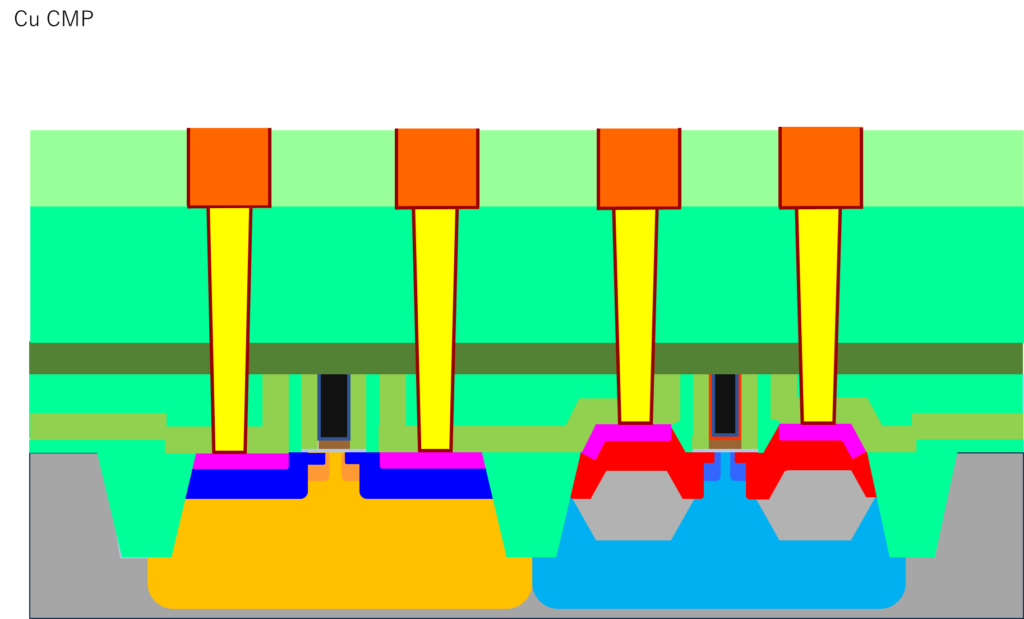

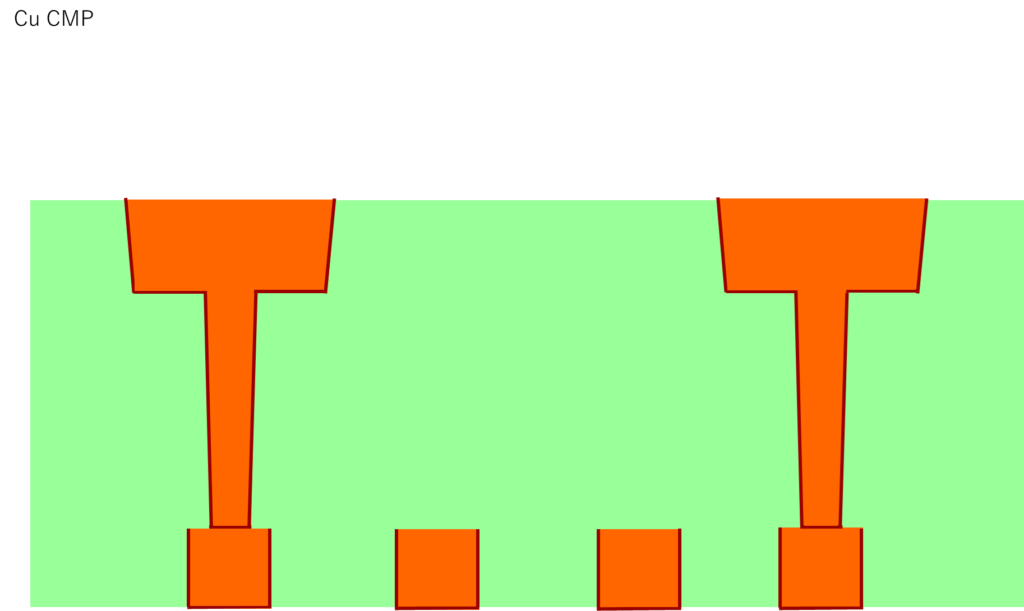

Cuめっきで配線層を埋めることができたので、最後にCMPしてやればCu配線の出来上がりです。

ここまでが、Cuのシングルダマシンのプロセスです。

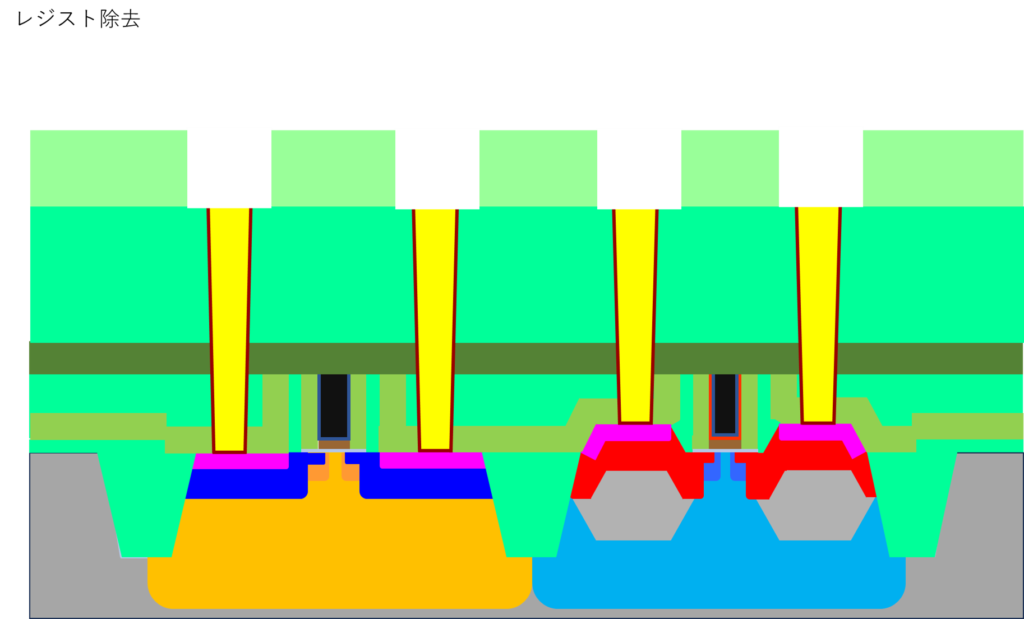

次は、Cuのデュアルダマシンのプロセスを紹介します。デュアルダマシンでは、下の配線とつなぐViaと配線自体を同時に作ってしまいます。

まずは、先ほど形成したCu配線の上に絶縁膜を成膜します。(高さの関係で、先ほど作ったCu配線より下側は省略しています。)

最初に、Viaの穴を掘るためのリソグラフィーを行います。

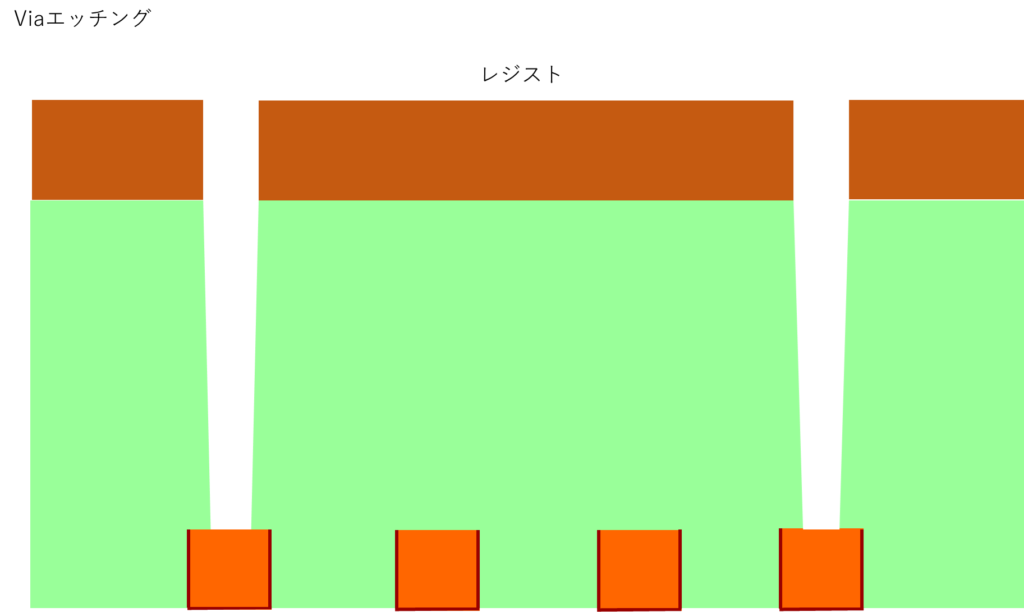

開口に合わせて、Viaの加工を行います。

そして、レジストを除去してやると、Viaだけがあいた状態になります。

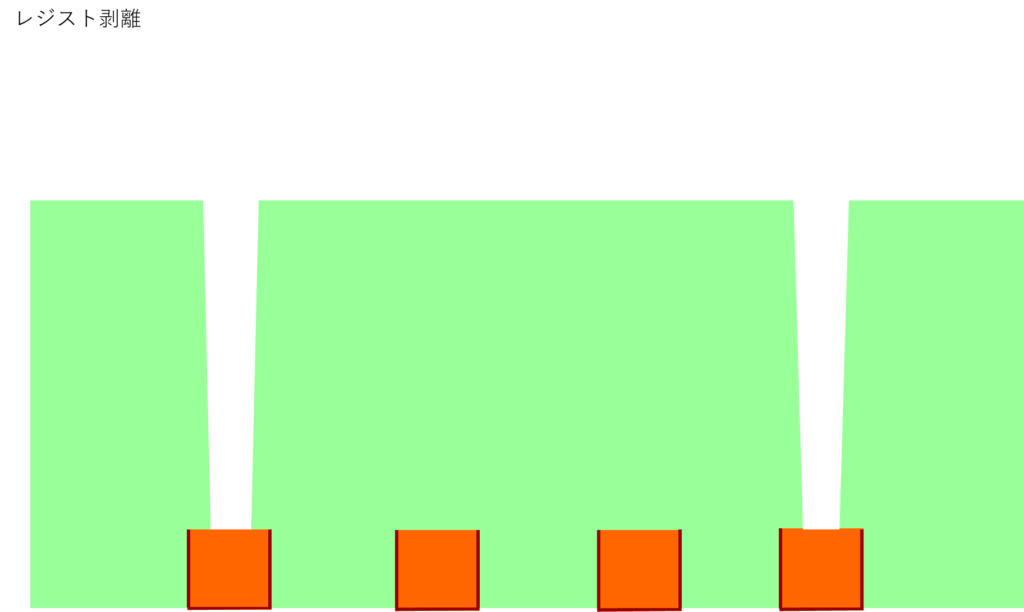

次に、配線用のリソグラフィーを行います。

配線の深さに合わせて、溝を掘ります。

そして、レジストを除去してやります。

こうすることで、Viaと配線を一括でCuで埋めることができます。

Cuで埋める場合の手順は、シングルダマシンの時と一緒で、バリアメタル・シード・めっきの順番です。

まず、バリアメタルを成膜します。

次に、Cuシードを形成します。

シードをもとに、めっきでCuを埋めます。

最後にCMPしてやることで、配線とViaを一括で作ることができました。

デュアルダマシンのメリットは、単純にCuを埋める工程が半分で済むことと、Viaと配線の接続不良を考えなくていいことがあります。

シングルダマシンで、Viaと配線を別々に作った場合、加工量が不足しているとViaと配線間がオープンになるリスクがあります。

一方、デュアルダマシンでは、Viaと配線を同時に埋めるので、オープンになるリスクは非常に低いです。

配線層が増えても、あとはこの繰り返しなので、断面の解説はここまでにします。

ゲートラストプロセスの基本構造

45nmプロセスを延々と描きましたが、この世代を取り上げたのは大きく2つの理由があります。

1つ目は、ゲートラスト構造のコンセプトはFinFETになろうが、GAA構造になろうが変わっていないからです。

現代の先端ロジック半導体のゲートスタック構造の始祖が、45nmプロセスのゲートラスト構造だと考えているわけです。

2つ目は、プレーナー型の世代で、製造プロセスが大きく変わったタイミングだからです。

ゲートラストは、ゲートスタック構造を変えるので、従来のプロセスと比べると、プロセスが大きく変わっています。プロセスを変えるということは、考えないといけないことが増えるので、題材としては非常に面白いです。

製品という面から見ると、45nmプロセスはレガシーと呼ばれる世代になっていますが、技術的には非常に面白い要素が詰まっている世代だと私は考えています。

レガシープロセスだと侮ることなかれ

45nmプロセスはレガシーと呼ばれますが、トランジスタ構造を勉強しようとしたときに、なんとか理解できるプレーナーの世代なのではないかと思います。

High-k絶縁膜でなぜMetal Gateを使わなければならなかったのかまで考えると、非常に深い理由があります。

商業的には重視されない世代かもしれませんが、今から半導体デバイスを学ぼうとする人からすると、非常に良い世代だと思います。

逆に言うと、45nmプロセスがわからないと、それ以後のプロセスは非常にわかりにくいので、今から学ぼうとする方にも非常におすすめです。

まとめ

この記事では、45nm世代のCMOSプロセスの断面を描くことで、ゲートラスト構造のプロセスを解説しました。

いや、図描くだけで大変でした。それでも、これが役に立ったと思っていただける方が1人でもいらしたら、幸いです。

記事の内容に明らかな間違いや、誤植、誤解を招く表現等がありましたら、コメントかお問い合わせフォームでご連絡いただけるとありがたいです。(基本的に、頂いたコメント等には全てお返事しております。)

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント