みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、180nm世代のCMOSプロセスを断面に焼き直していくことで、CMOSのプロセスを解説していきます。

冒頭から宣言しますが、この記事めちゃくちゃ長いです。(17000字あるのと、図が50枚以上あります。)

180nmプロセスについて

最初に、180nmプロセスについて簡単に解説します。

180nmプロセスは、2000年前後のロジック半導体の最先端プロセスでした。20年以上前の話です。

今では、レガシープロセスと扱われる世代です。(安く作れるという意味では、非常にありがたいんですが。)

そもそも、この記事を書こうと思ったきっかけは、東洋経済新報社の記事の中で180nmプロセスのモデルプロセスが出ていたことです。(記事は下記リンク先から読めます。有料会員限定です。)

https://toyokeizai.net/articles/-/743738

あくまでも、モデルプロセスなので、実際に記事中で出されていたプロセスで製品が製造されていたわけではないそうですが、それでもオープンな媒体にCMOS製造のプロセスが出ることは珍しいです。

そこで、モデルプロセスの工程を1つずつ追っていけば、180nmプロセスのモデル断面が作れるであろうというのが、私の目論見でした。

ただ、180nmプロセスといえど、最初から最後まで並べると約300工程あります。

まあまあ大変だろうなと思ってはいましたが、想定以上に大変でした・・・

ここからは、180nmのプロセスを1から追っていきます。元のプロセスには、検査工程が入っていますが、製造プロセスとして断面形状が変わらないので検査工程に関してはスキップしています。

また、実際に180nmプロセスの製造などに携わったことが無いのと、素人が書いているので、ずれている点や誤記等があれば教えていただけると幸いです。

ベアSi~STI形成

CMOSの製造工程は、ただのシリコンウエハからスタートします。

まずは、表面の洗浄を行って、次に表面を酸化します。(この酸化のことを、犠牲酸化と呼んだりします。)

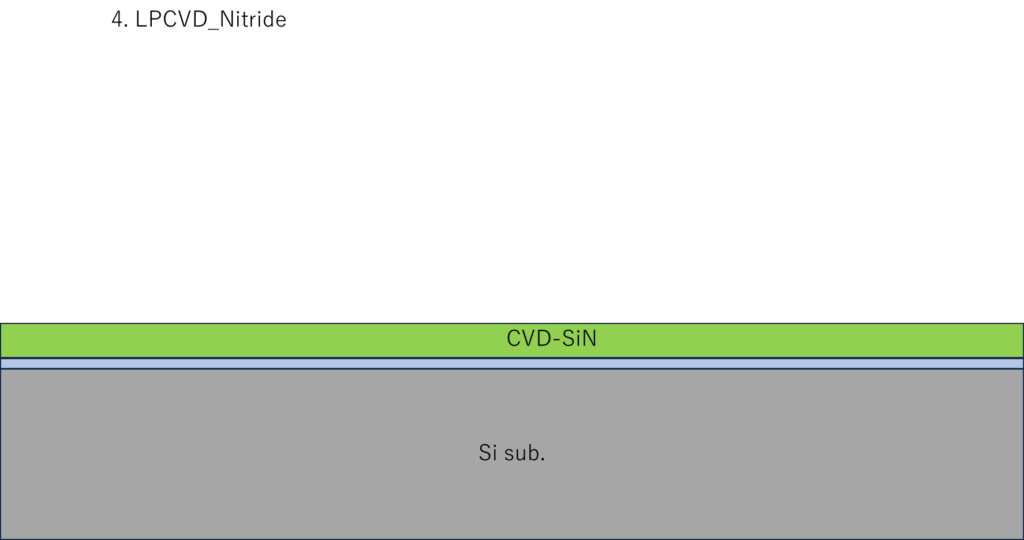

次に、CVD-SiNをつけます。

簡単のために、Siウエハの表面側の断面しか書いていませんが、実際の製造プロセスを考える時には、ウエハの裏面やエッジ部(ベベルと呼んだりします)もケアしなければなりません。

表面に回路を作るのに、裏面も気にするのか?と思われるかもしれないですが、裏面も重要なんです。

半導体の製造プロセスに詳しい方であればご存知でしょうが、シリコンウエハに付ける膜は、成膜方法によって裏面につくものとつかないものがあります。

裏面についてしまう膜を扱う時には、ついたあとどんな挙動を示すのかを考えていく必要があります。

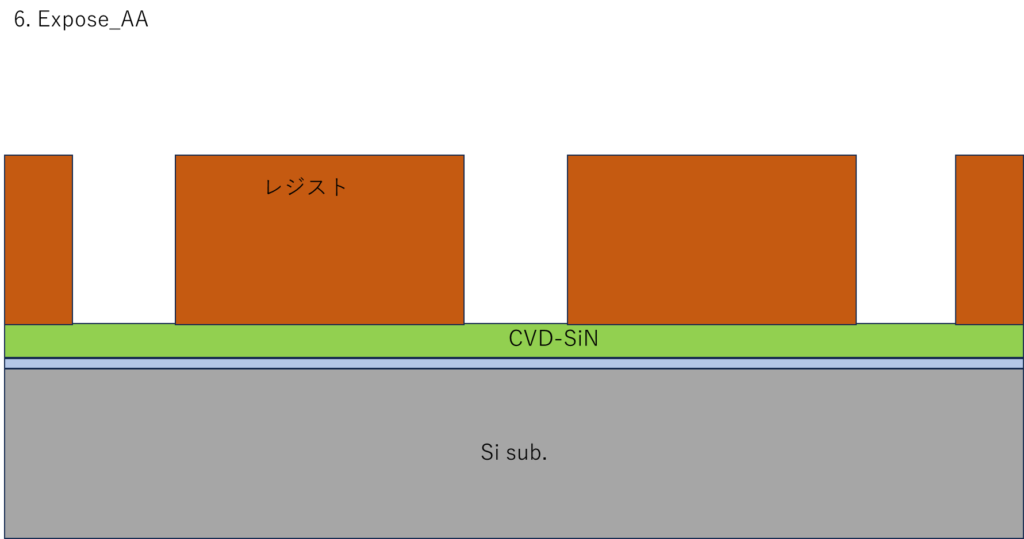

SiNを表面に貼れたら、次はAAと呼ばれる領域を形成します。

AAは、最終的にCMOSを構成するトランジスタが載る領域です。最初はよくわからないと思いますが、あとから振り返れば何をやっていたのかわかるようになります。

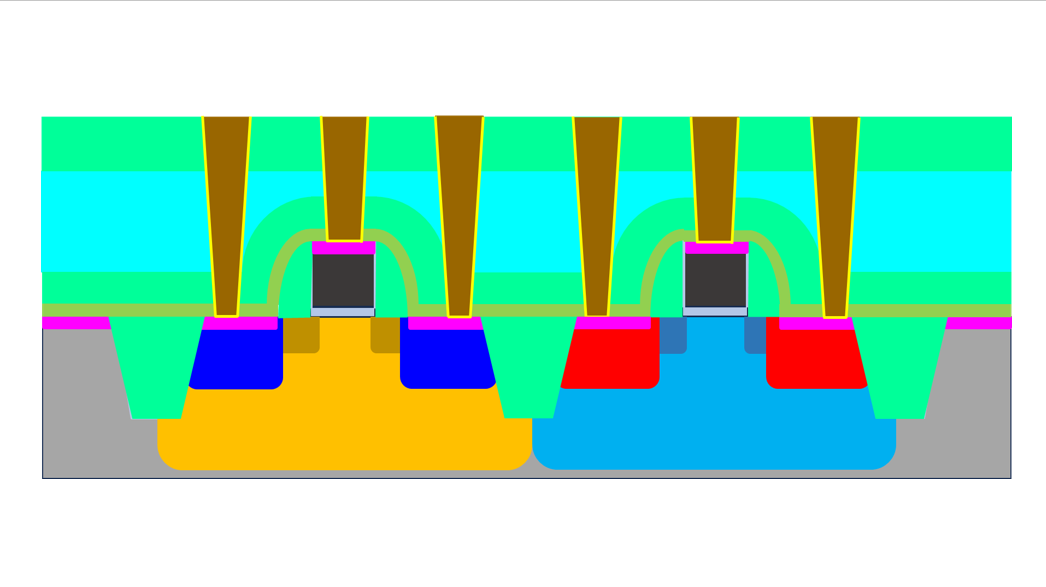

AAの領域にはCMOSを構成するトランジスタが作られますが、CMOSはNMOSとPMOSの2種類から作られています。

そして、NMOSとPMOSを分けるだけではなく、同じ種類のトランジスタ(NMOS同士・PMOS同士)であっても、1つ1つのトランジスタを電気的に分離してやる必要が出てきます。

素子を分離するために、溝(STIと呼ばれます)を掘るんですが、その領域を作るためにリソグラフィーを行います。これが、Expose_AAの工程の意味です。

ちなみに、リソグラフィーに関しては、断面の解説では綺麗に露光されたあとの形を描いています。

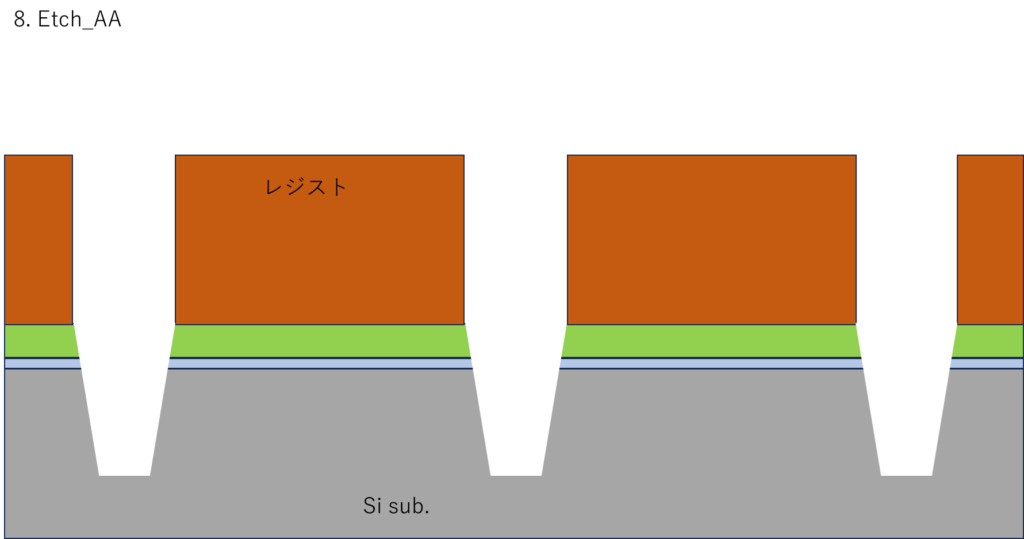

綺麗に露光できたとすると、次は素子分離のための溝を掘っていくことになります。

素直に溝を掘ると、溝が垂直に掘れそうですが、実際は垂直に掘ることはできません。

ほんのちょっとですが、テーパー角がつきます。STIを深く掘るのは結構大変なのを強調するために、溝にテーパー角をつけた絵にしています。

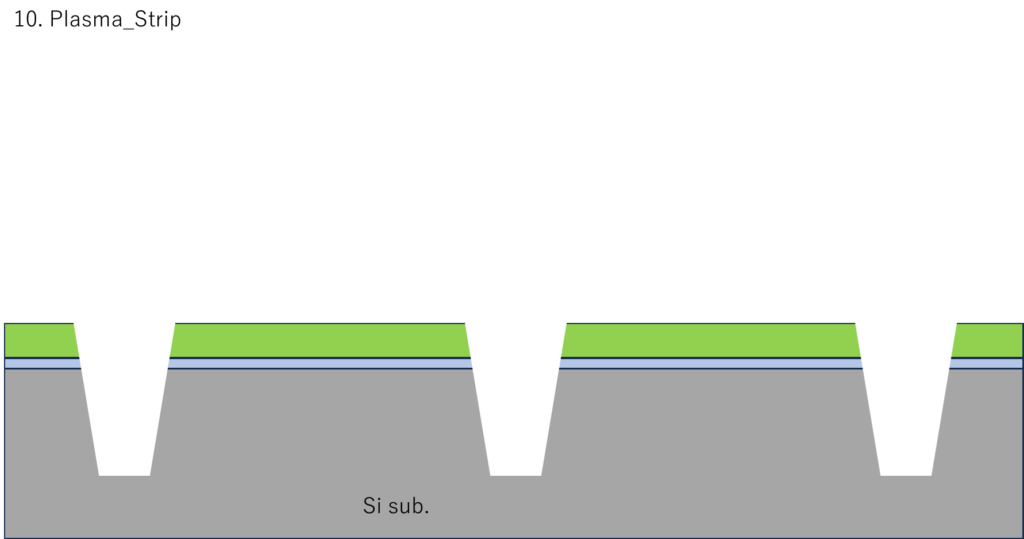

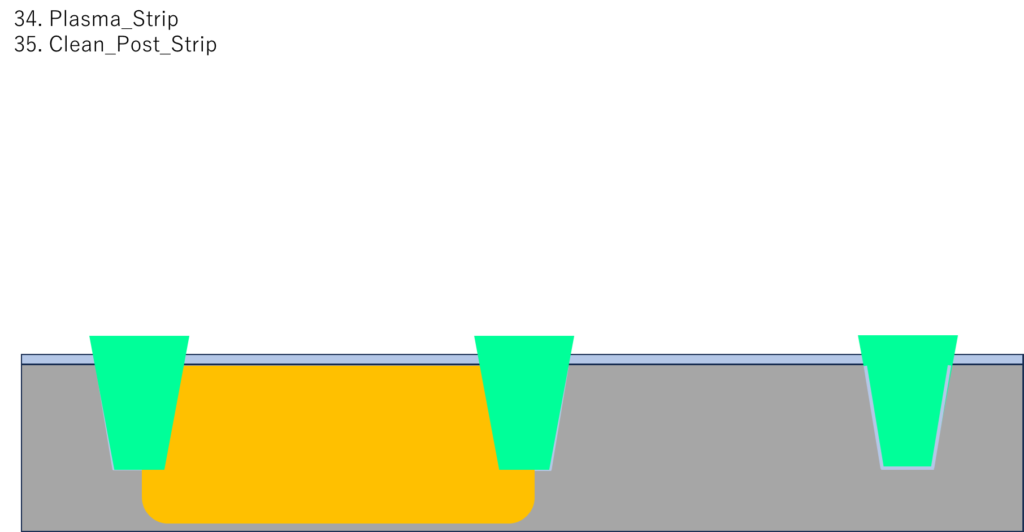

レジストは、有機物の膜なので、基本的に加工を行ったあとは、はがしてやる必要があります。

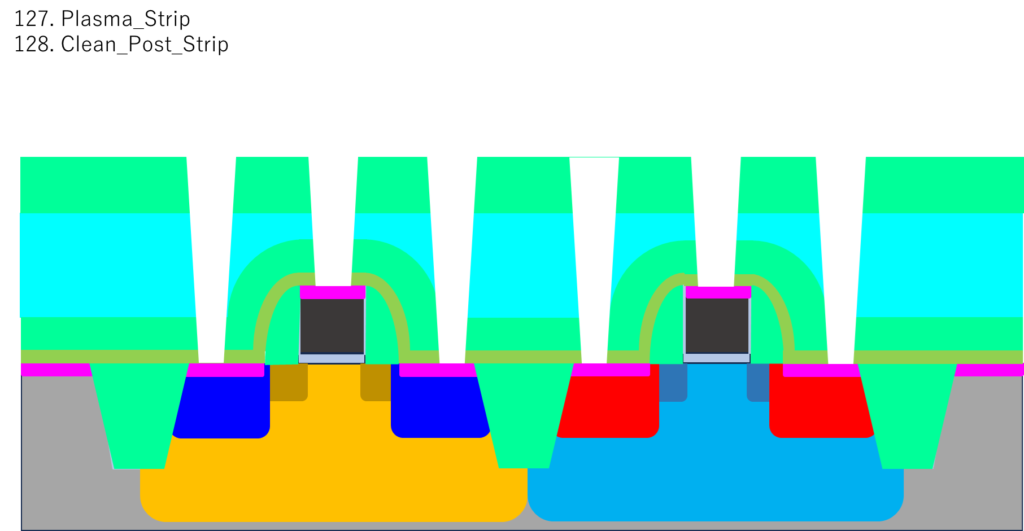

AAの加工用に使ったレジストを取ってやるのが、Plsma_Stripの工程です。

レジストの剥離方法も、酸素プラズマで灰化してしまう方法(アッシング)と、硫酸と過酸化水素の混合液(硫酸過水とかSPMと呼びます)に入れて、剥離してしまう方法があります。

180nmのモデルプロセスは、基本的にプラズマ酸化してしまう、アッシング処理が多かった印象です。

さて、アッシングしてやるとレジストが取れました。

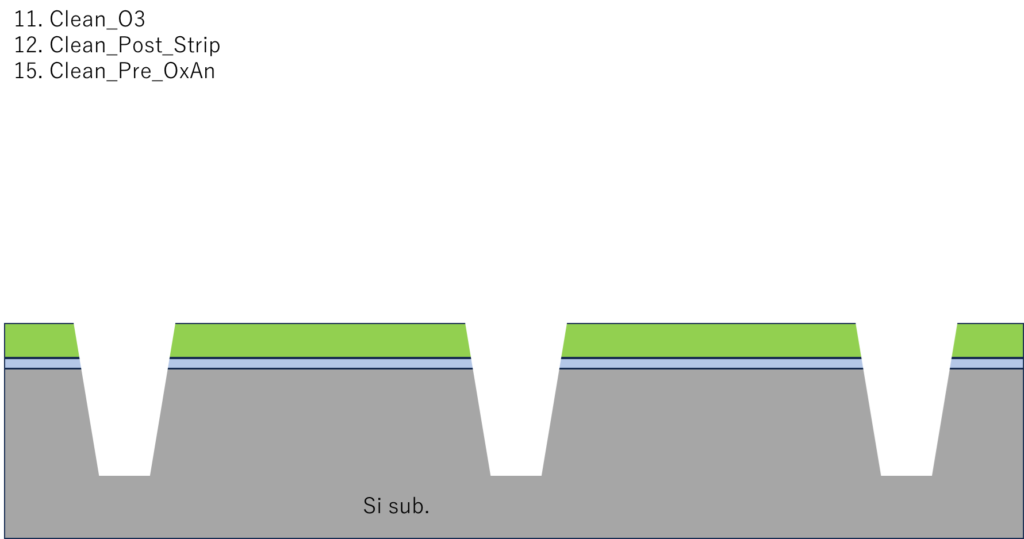

断面としては変化がありませんが、O3洗浄等が入っています。

細かい処理条件が書かれていないので、何をやっているのか具体的にはわかりませんが、おそらくパーティクル除去と酸化前の洗浄を行っているんだと考えられます。

洗浄を行ったあとに、Oxidation(酸化)が入ります。

断面のどこが変わったの?と思われるかもしれませんが、ちょっとだけ変わっています。溝の表面がうっすら水色に変わっているのがおわかりいただけるでしょうか。

STIを掘った領域のSiの表面を熱酸化することが、この工程の目的です。

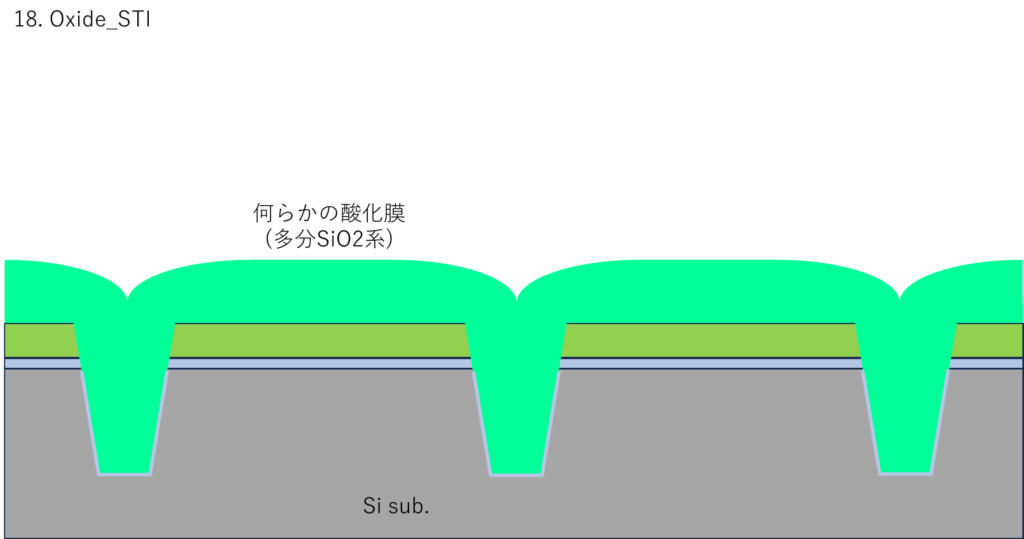

Oxide_STIの工程では、素子分離のために形成したSTIを酸化膜で埋めます。

なぜ酸化膜で埋めるのかということですが、酸化膜は絶縁物なので都合がいいからです。

溝の中が埋まるように成膜しないといけないので(完全には埋めないプロセスも成立できないことはないんですが、複雑なのでここでは省きます)、表面部分は厚めに成膜されています。

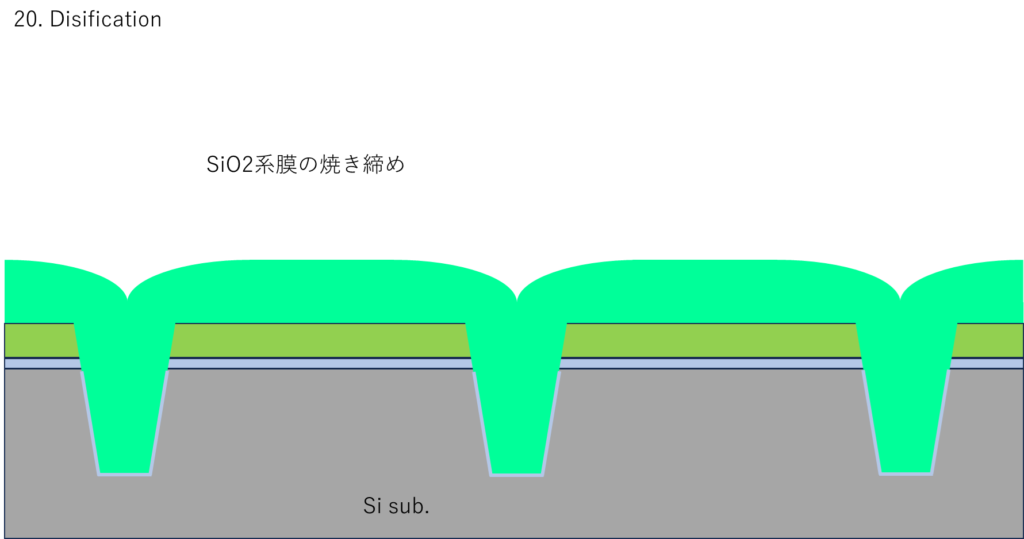

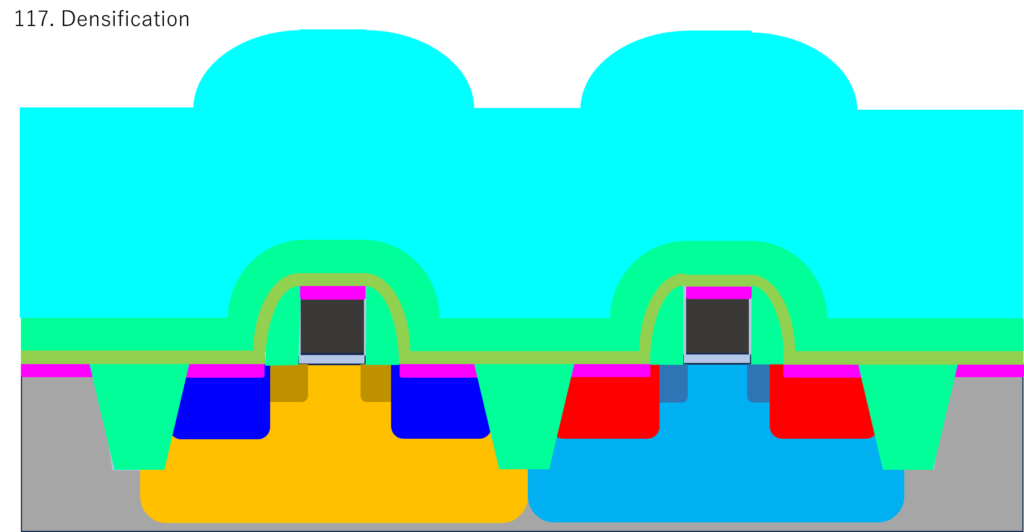

Densificationでは、先ほど製膜した酸化膜の焼き締めを行います。

酸化膜と一言で言っても、スカスカな膜から非常にしっかりした膜まで色々あります。

おそらく、STIの埋め込みに使われている酸化膜は、スカスカな膜なので焼き締めを行っているんだと考えられます。

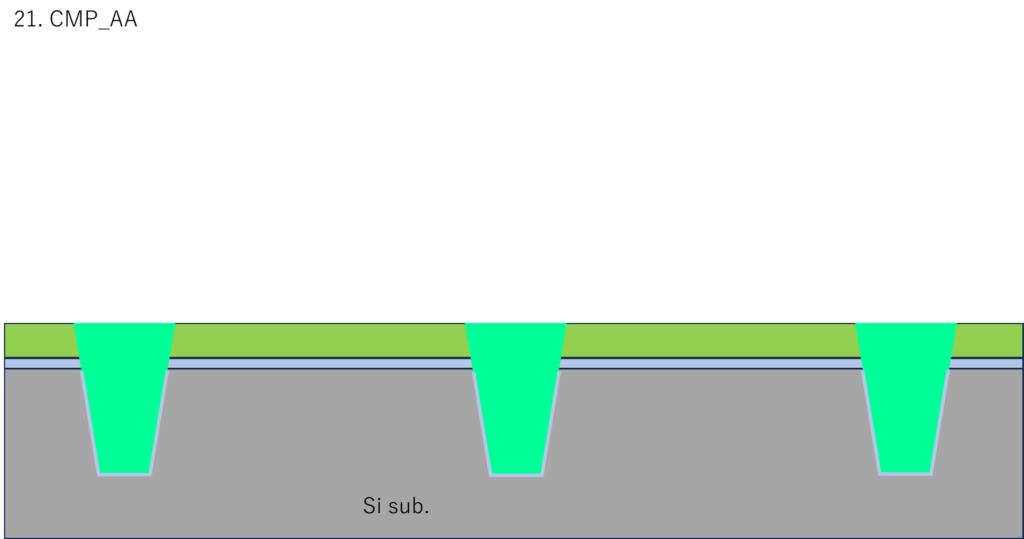

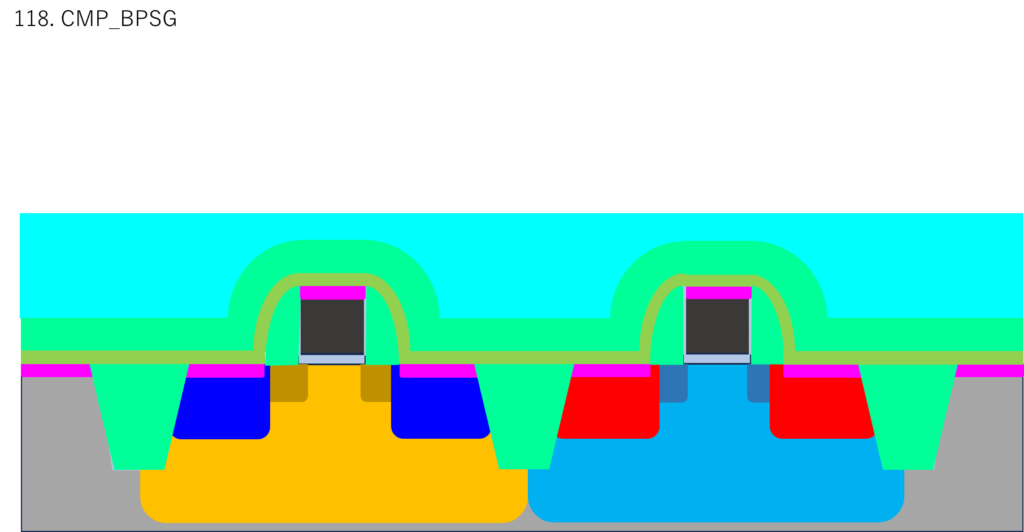

焼き締めを行ったとは、CMPで表面を平坦化します。酸化膜を削っていって、SiNの表面でCMPを止めることで、STIの溝の内部だけを酸化膜で埋めることができます。

単純に、素子分離ために溝を掘って中を酸化膜で埋めるだけでも、これだけの工程が必要になります。

STIを酸化膜で埋めることはできましたが、表面にSiNが残ったままの状態になっています。

この状態だと、あとの工程に進むことができないのでちょっとした工夫がいります。

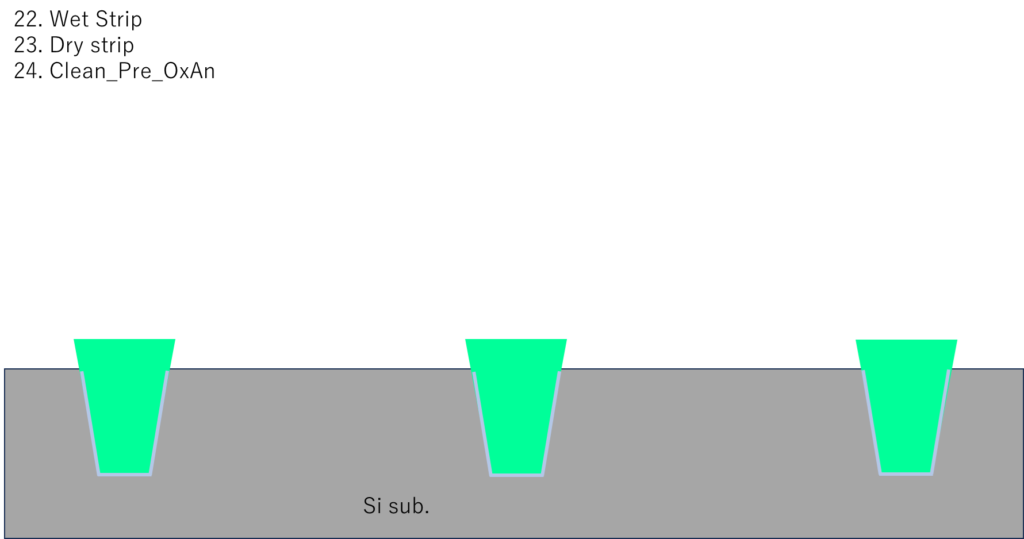

Wet_Stripの工程が入ってきます。具体的にどんな薬液で処理しているのかは書かれていませんが、おそらくSiNを抜く薬液処理だと考えられます。

多分、リン酸でSiNを抜いているんだと想像しています。SiNを抜いてやって、表面側のSiO2を取ってやると、このような断面にたどりつきます。

ここまでで、STI形成は完了です。断面だけ見ると、溝を掘って酸化膜で埋めただけですが、それなりに手間がかかっているのがおわかりいただけたでしょうか。

CMOSの製造プロセスは、まだまだ先は長いです。300工程あるうちの24工程目なので、10%くらいなんです。

STI形成ができたので、AA領域に素子を作りこんでいくフェーズに移ります。

Well/Channel形成~ゲート加工

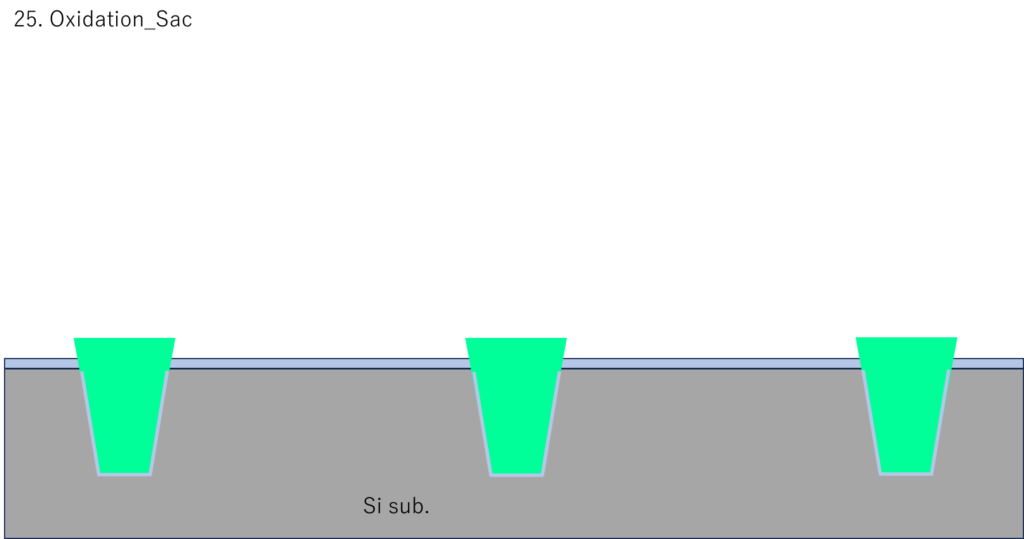

STIが形成できたので、ここからAA領域に素子を作りこんでいきます。まずは、表面をもう一度酸化します。

Oxdation_Sacと書かれているのは、犠牲酸化のことを意味しているのでしょう。

犠牲を英語だとSacrificeと書きます。Sacはここから来ていると考えられます。

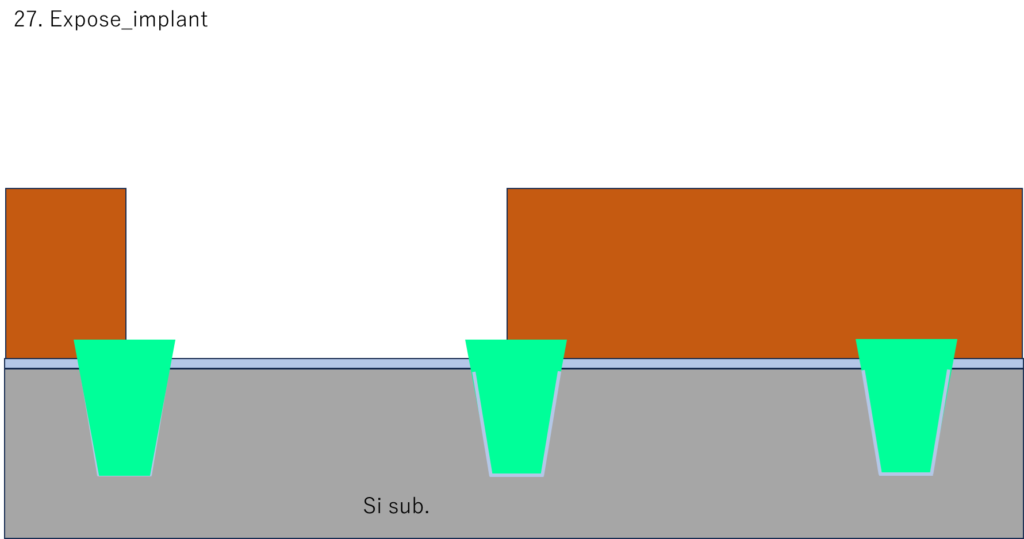

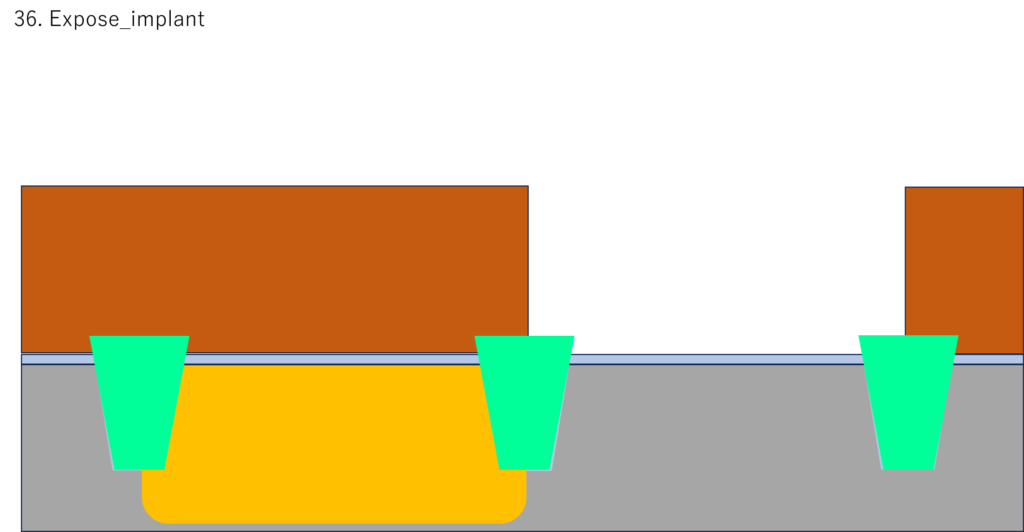

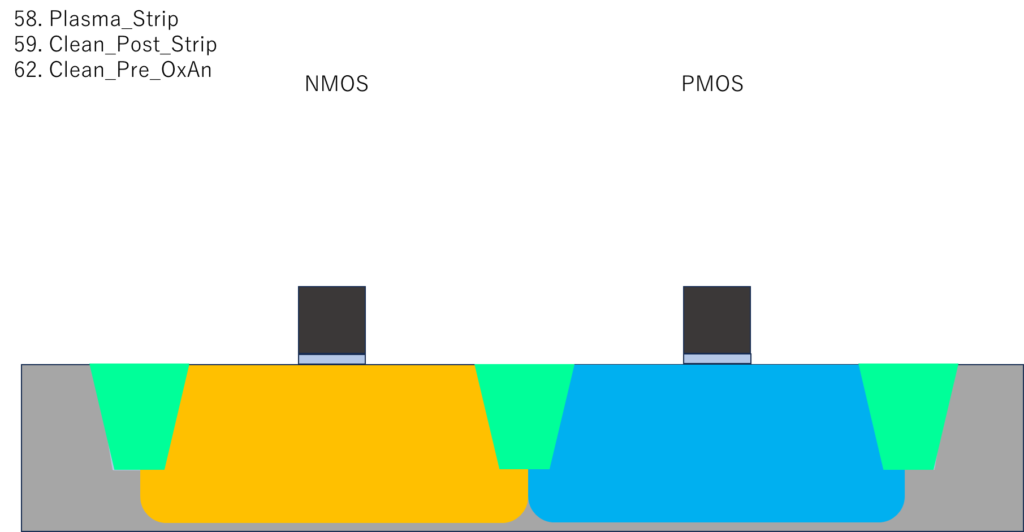

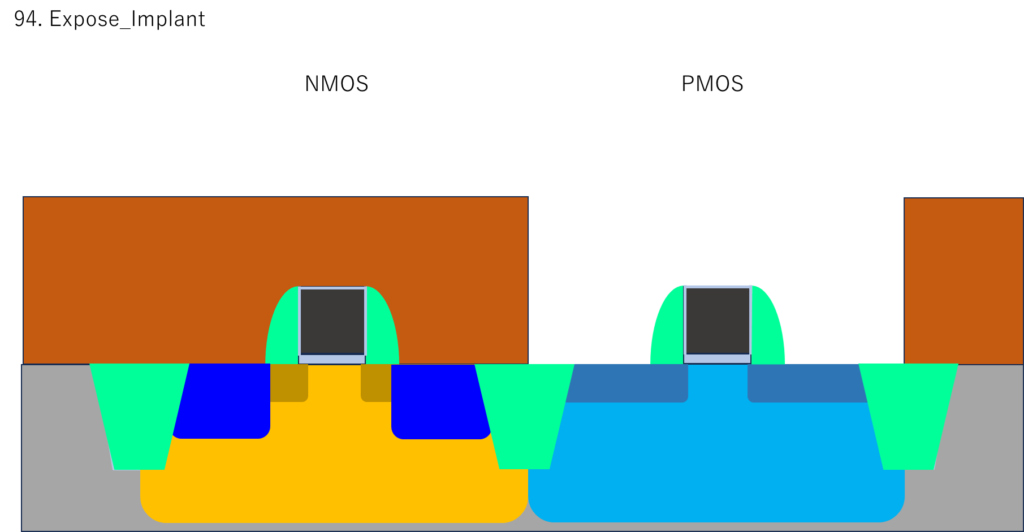

Expose_Implantという工程が出てきました。180nmのモデルプロセスでは、イオン注入用のリソグラフィーのことを、Expose_Implantと書いているようです。

これは、何のために行っているのかというと、シリコン基板へのイオン注入をやりたい場所だけ、レジストの窓を開けて、他の部分にはイオン注入で注入するイオンが入らないようにしているわけです。

半導体製造プロセスでは、イオン注入というのは欠かせない工程です。シリコンに対して、不純物であるイオンを注入してやることで、シリコンの極性をP型とN型に作り分けています。

CMOSには、NMOSとPMOSの2つがあります。PMOS用とNMOS用では使われるイオンの種類や濃度が違います。

つまり、PMOSとNMOSのそれぞれについて、別のイオン注入を行う必要があります。そのため、リソグラフィーを使ってイオン注入をしたい領域のレジストだけ開口してやる工程が必要になってくるわけです。

この図では、左側にNMOSを右側にPMOSを描いていくので、それぞれのイオン注入の開口を分けています。

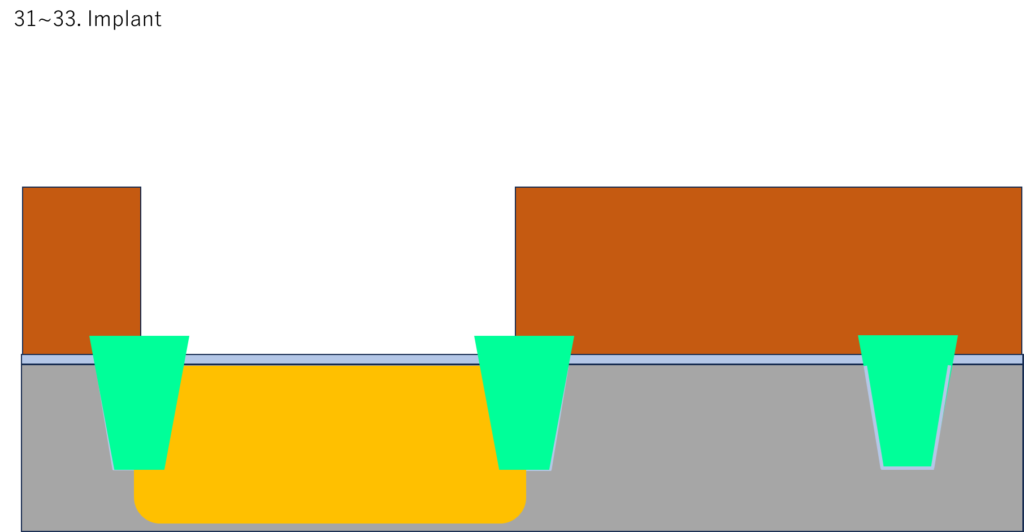

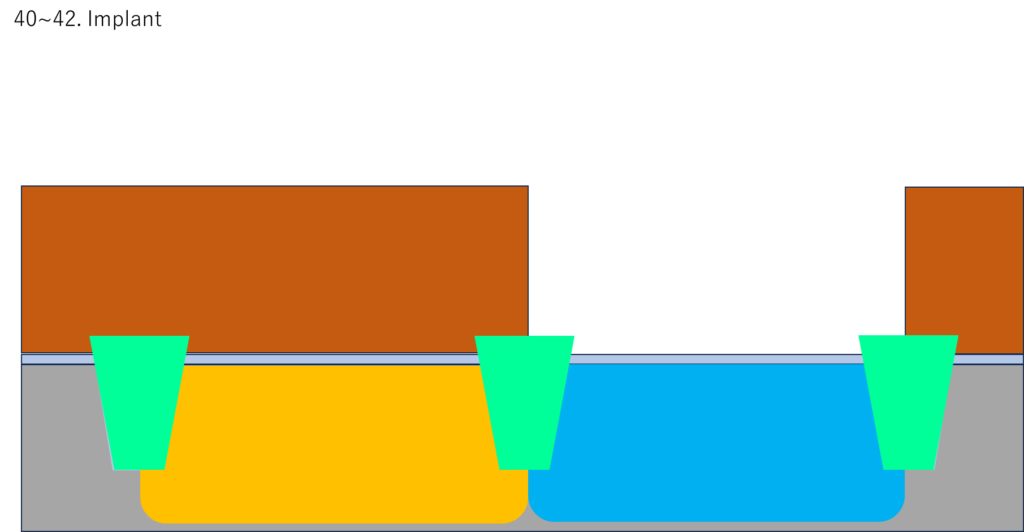

イオン注入を行うと、レジストの開口部だけにイオンが入ります。(図の中で黄色に示しているの部分です。)

モデルプロセスでは、イオン注入の工程が3段階に分かれています。この行程では、WellやChannelと呼ばれる部分のイオン注入を行っていると推定されます。

シリコン基板の深い部分まで、イオンを注入する必要がある場合、イオン注入の装置の加速電圧を大きくしてやる必要があります。

イオン注入装置は、加速電圧やイオンを入れる量によって分かれているので、3つのプロセスに分かれていると考えられます。

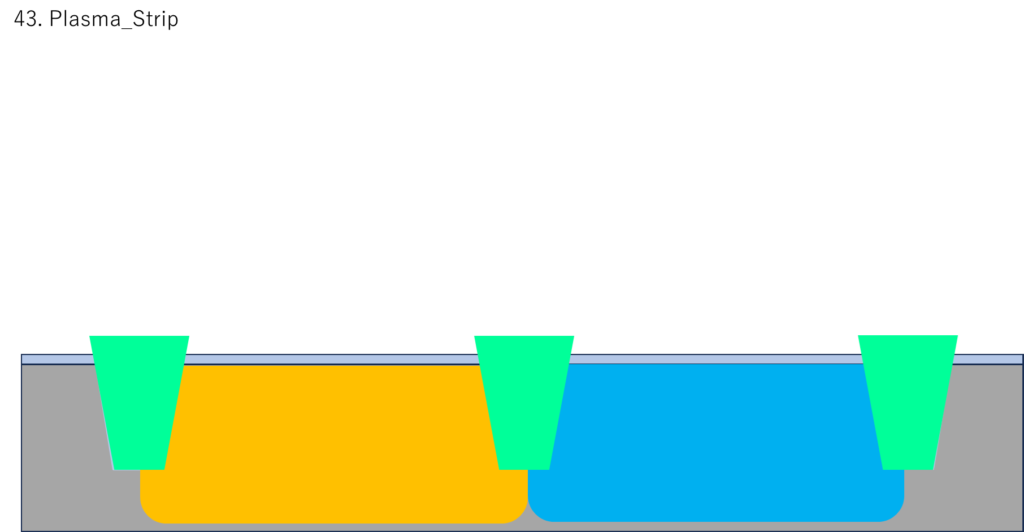

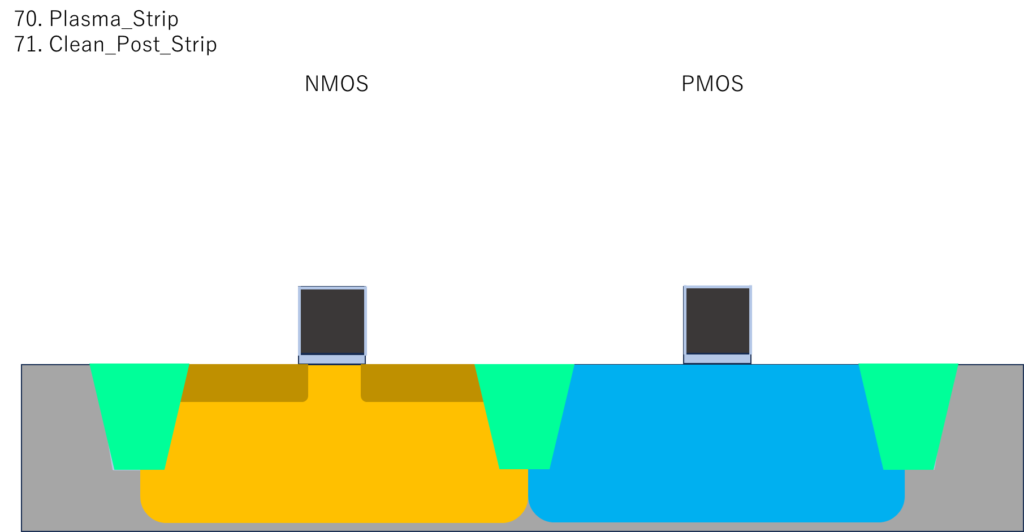

イオン注入が済んだら、レジストは用済みなので除去してしまいます。

レジストを取ってやると、NMOSのWellとChannel部分だけ、イオンが打ち込まれた断面になりました。

NMOSとPMOSの両方を作る必要があるので、今度はPMOSに対してもWellとChannelのイオン注入をやっていきます。

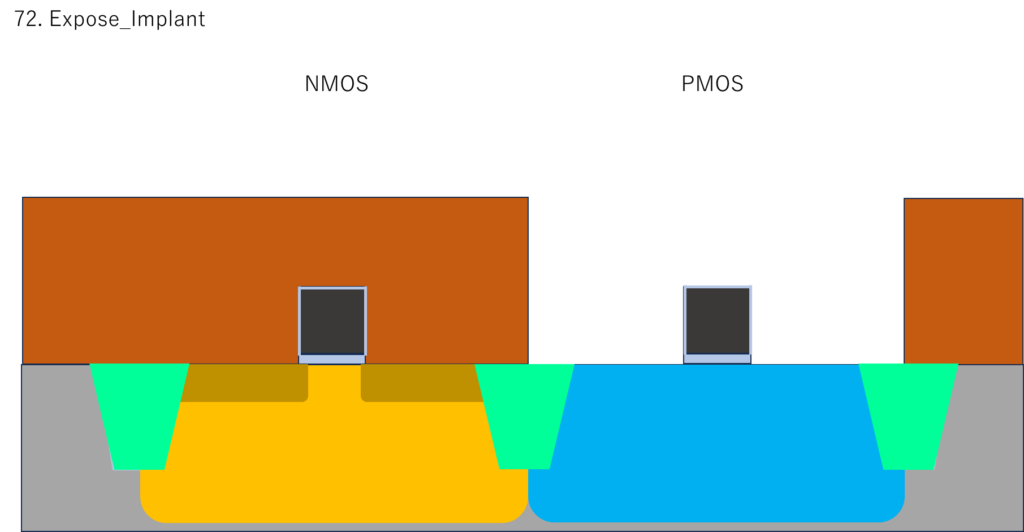

イオン注入を行う前に、PMOS部分だけ開口するようにレジストの窓をあけてやります。

この時、レジストでNMOS側を覆ってやらないと、せっかく先ほど作ったNMOS領域のイオンの分布が変わってしまいます。

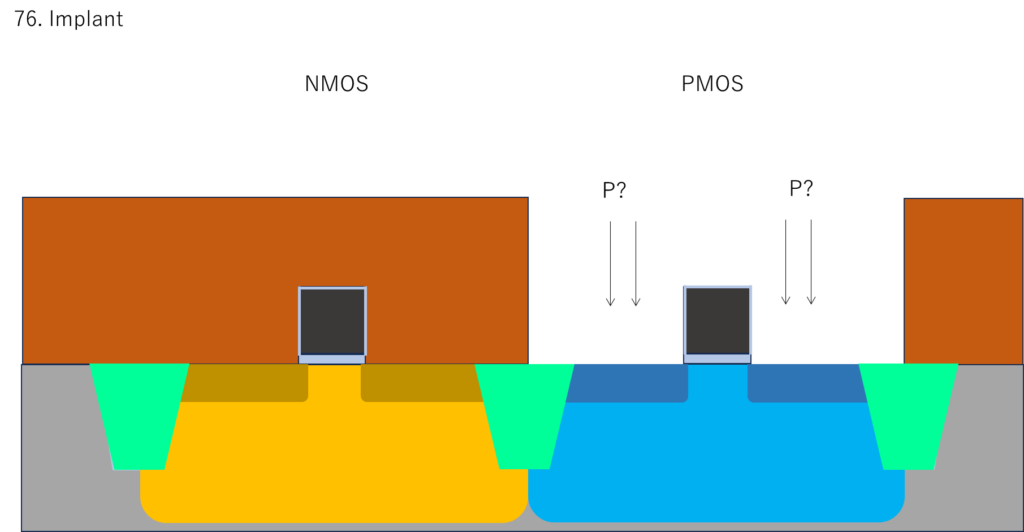

そして、PMOSのWellとChannel領域のイオン注入を行うとこのようになります。

PMOSのWellとChannel領域は、青色で示した色になっています。

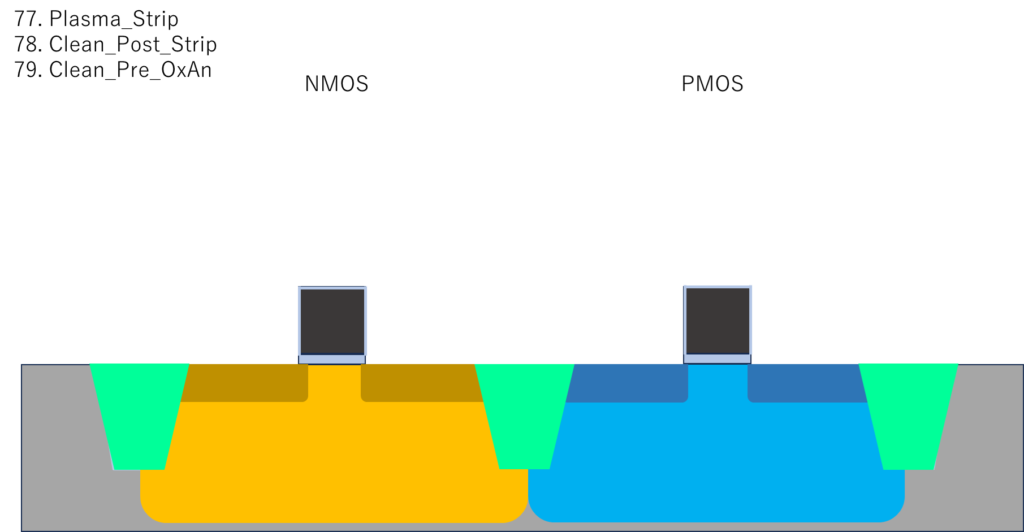

そして、レジストを除去してやるとこのようになります。

これで、NMOSとPMOSのそれぞれの領域に、WellとChanne向けのイオンが打ち込まれた状態になりました。

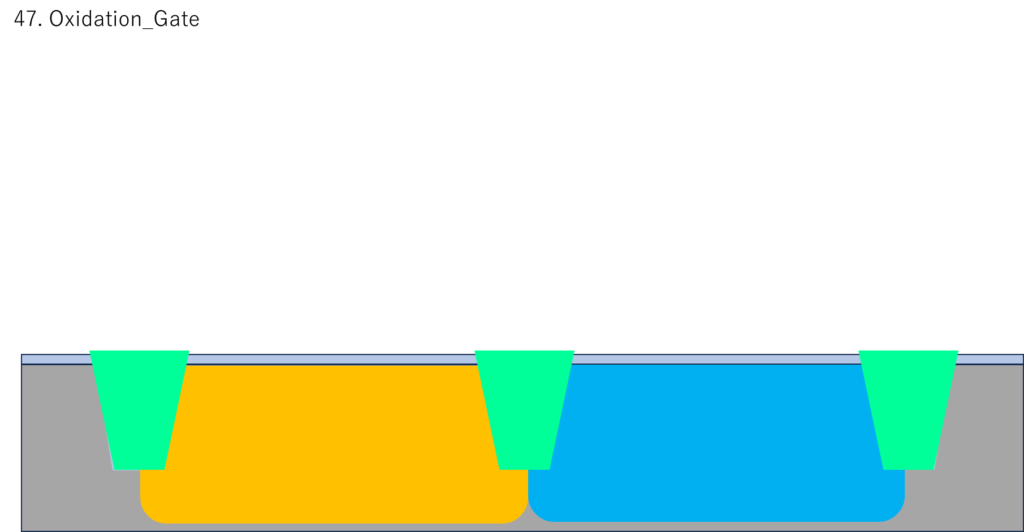

このあと、NMOSとPMOSのゲート酸化膜を形成していく必要があります。

ゲート酸化膜形成は、CMOSの形成プロセスの中でも非常に重要です。酸化膜の膜厚が変わったりすると、MOSトランジスタの性能にダイレクトに効いてきます。

また、ゲート酸化膜は条件にもよりますが、高温(1000℃近い)温度で行うため、前処理として薬液処理が行われていることが多いです。

3つくらい、薬液処理が並んでいますが、最後にO3で処理してやって、ゲート酸化膜形成に入ります。

ゲート酸化膜は、180nmプロセスであれば、基本的に熱酸化SiO2で作らられているはずです。High-K/Metal Gate構造になると、この辺が変わってきますが、それ以前であればSiO2系の膜で作られていると思います。

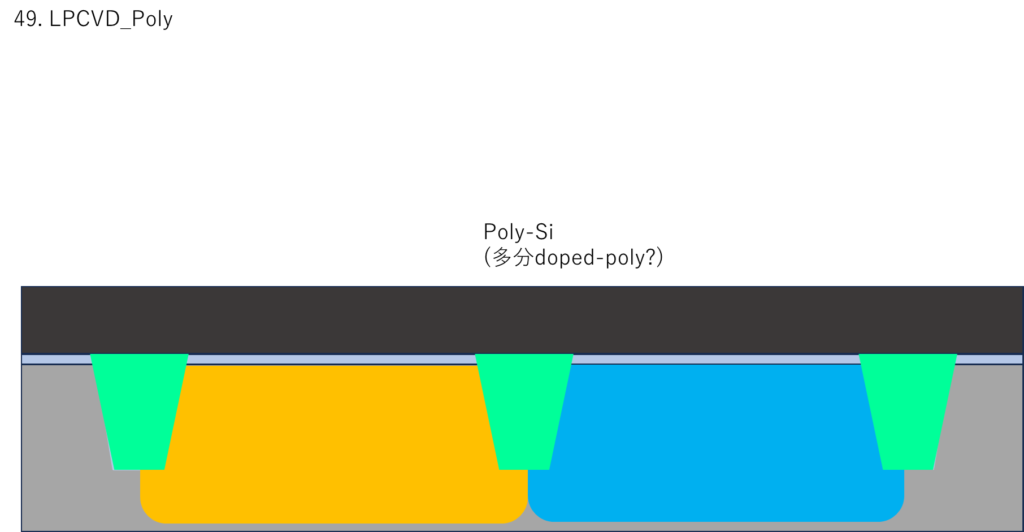

ゲート酸化膜が形成できたら、この上にゲート電極を積んでいきます。

ゲート電極は、180nmプロセスではpoly-Si(多結晶シリコン)が使われていたようです。

LPCVDでpoly-Si膜を形成しているので、シリコンの表面側(本当は裏側も)はpoly-Siで覆われる形になります。

このあと、ゲート酸化膜の次に重要なゲート電極の加工に入ります。

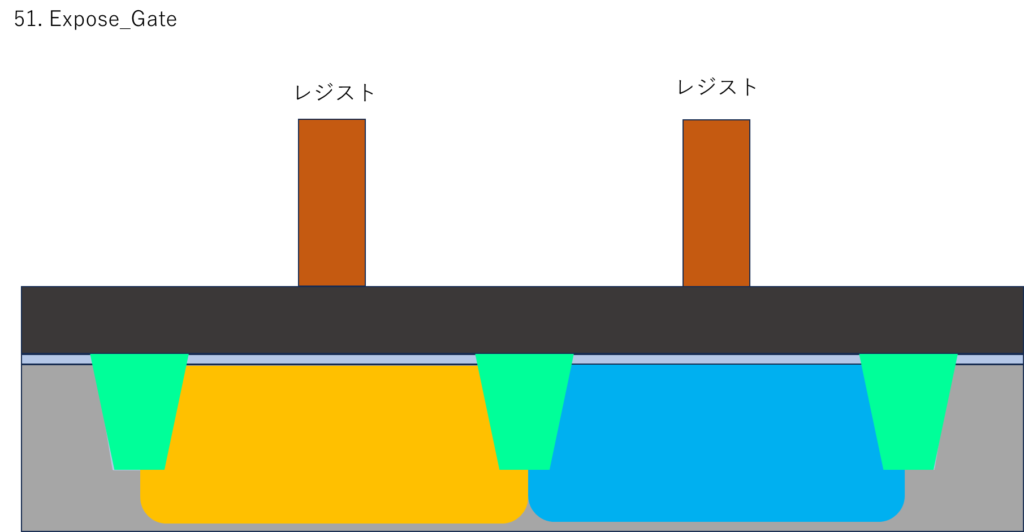

成膜したpoly-Siの上にレジストで、ゲート電極用のパターンを形成します。

180nmくらいの世代であれば、トランジスタの最小寸法はこのゲート電極の長さだったのではないかと思われます。

FinFET以降の世代にになってからは、ゲートの長さが最小寸法ではなくなってしまったようですが、昔のプロセスノードはゲート長をベースに語られたいたんだと考えられます。

ゲートの長さがトランジスタの最小寸法であれば、必然的にゲート電極形成のためには、その世代で一番狭い寸法が作れる露光機が使われます。

180nmのモデルプロセスでは、Litho_2048と書かれていたので、おそらくKrF-dryの露光機が使われていたんだと推測されます。

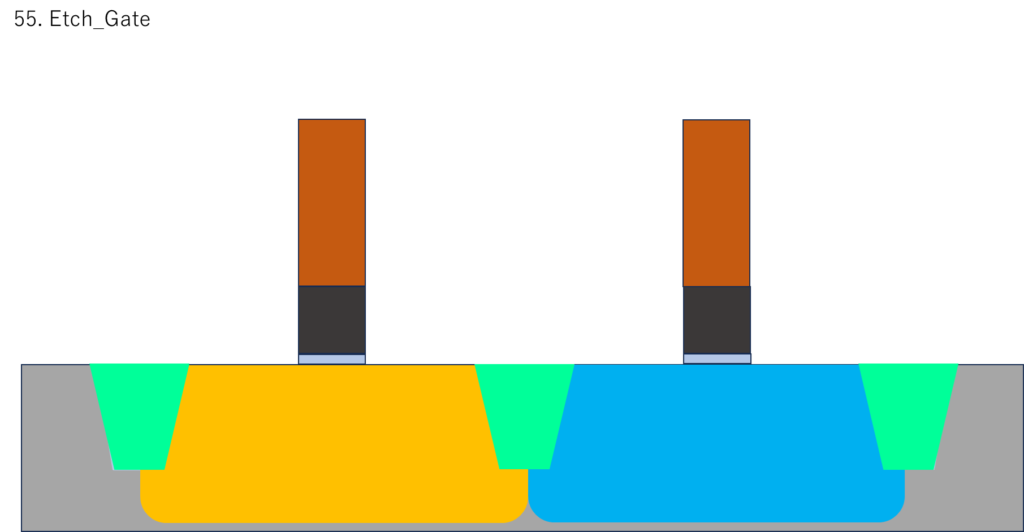

露光がうまくできたら、次はゲート電極の加工です。

ゲート電極を加工された経験がある方から見ると、こんなきれいに加工出来たら苦労しないんだけど・・・と言われそうですが、模式的にきれいに切れた断面を描いています。

少しマニアックな部分ですが、ゲート電極の加工はウエハ全体の中で、電極として残す部分は非常に小さいです。このことは、ゲートの部分以外は、poly-Siは無い状態にしないといけないことを意味しています。

そうすると、ウエハの全面を見た時に、ゲート電極の削り残しがあってはいけないことになります。

これが結構厄介で、削り残しがあると後の工程に影響が出るので(ダスト等になって飛散するリスクなどがあります)、オーバーめにエッチングしないといけません。

そうすると、断面をみて頂ければわかるんですが、Si上のゲート電極部分以外の酸化膜はエッチングされたような状態になることが想像できます。

プロセスから断面を考えるのは、この辺も考えないといけないので、ちょっと難しいんですよね。

少しマニアックな話になりましたが、ゲート電極の加工が無事終わったら、レジストを除去していきます。

いくつかウエット処理を行えば、NMOSとPMOSのそれぞれに対して、ゲート電極が加工できます。

この辺までくると、トランジスタらしくものに近づいてきたように見えるのではないでしょうか。

それでも、62工程目なので300工程のうちの20%程度です。CMOSのプロセスは、まだまだ続きます。

スペーサー形成~高濃度拡散層形成

ゲート電極の構造を作るところまで進んだので、スペーサーを作る工程に入っていきます。

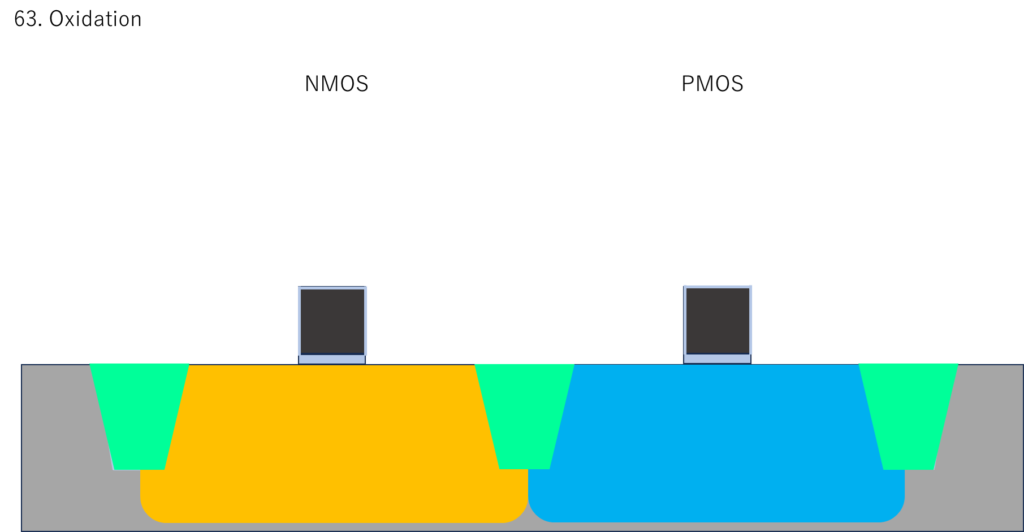

スペーサーを形成する前に、熱酸化が入ります。

目的は、はっきりと書かれていませんが、ゲート電極を加工したあとのPoly-Siの表面を酸化膜で覆ってしまうことではないかと考えられます。

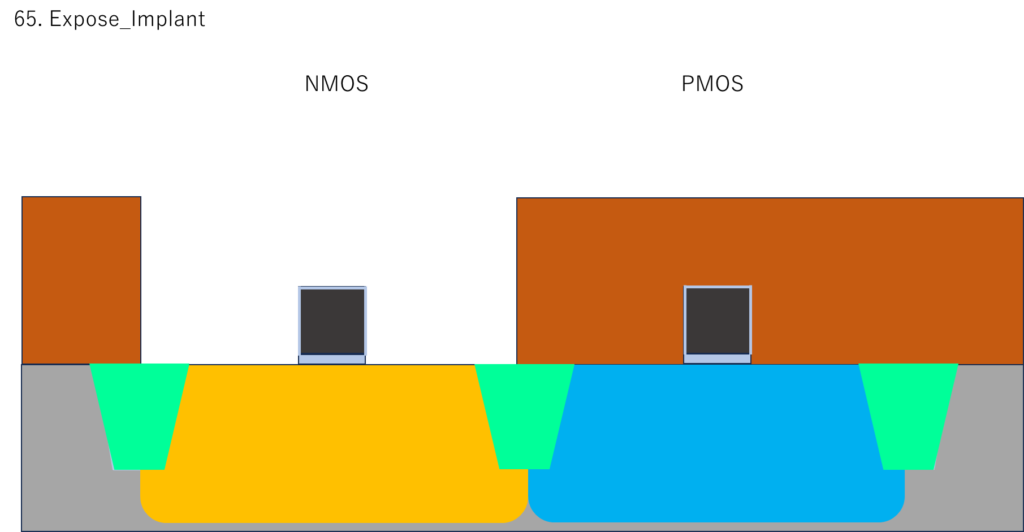

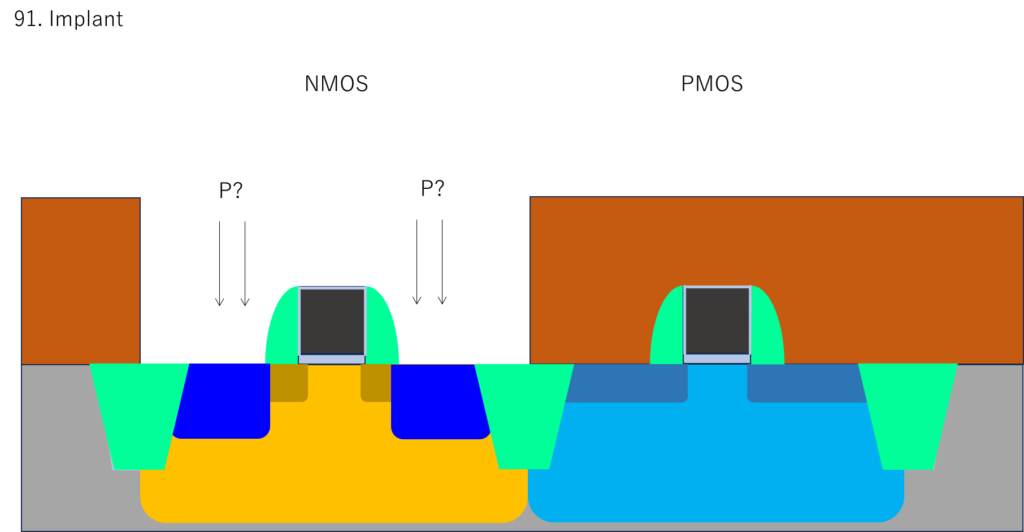

スペーサーを作る前に、NMOS・PMOSそれぞれで、イオン注入の工程が入ります。

イオン注入条件が詳しく書かれていないので推測ですが、NMOS・PMOSそれぞれに対して、逆の種類のイオン(NMOSであればP型のイオン、PMOSであればN型イオン)を入れているのではないかと考えています。

理由としては、ゲートの長さが短くなると、短チャネル効果というものが出てきます。

短チャネル効果の影響は色々ありますが、単純にゲートの長さを短くしていくと、MOSトランジスタ動作をしなくなってしまうというのが一番の課題です。

これを抑制するために、NMOSにはP型のイオンを、PMOSにはN型のイオンを注入しているんだと思います。

理由はマニアックなので、詳しく知りたい方はデバイスの本でも読んでみてください。(Pocketとか、HaloとかExtensionと入れると、細かいところは出てくると思います。)

とりあえず、ここでNMOS・PMOSでそれぞれ別々のイオン注入が入ってきます。

NMOS向けのイオン注入のために、レジストでNMOS側だけを開口するとこのようになります。

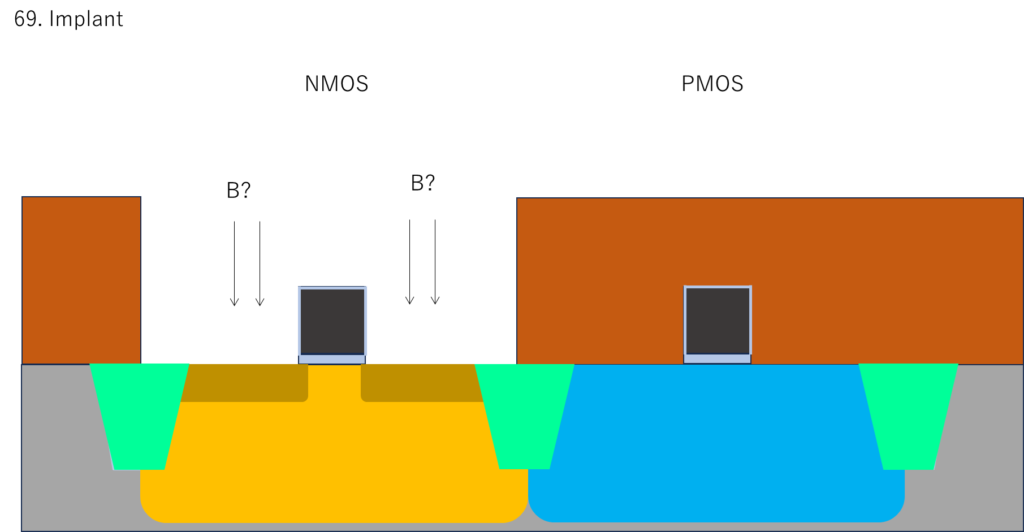

この状態で、NMOS向けのイオン注入をすると、このようになります。

NMOSに対して、逆の極性のイオンを打つので、B(ホウ素)を打っているのではないかと思います。Bは、半導体デバイス関連の人は、ホウ素と呼んでいることはほとんど聞いたことがなく、大抵の人はボロンと呼んでいる気がします。

ホウ素もボロンも文字数一緒なのに、なぜなんでしょうね?

新しくイオン注入した領域は、少し濃い黄色(黄土色かな?)にしています。これは、WellとかChannelよりも高い濃度で打たれていることを暗示しています。

具体的にどの程度の濃度を入れるか等は、そのまま各社のノウハウに直結するので公開されることは普通ないです。

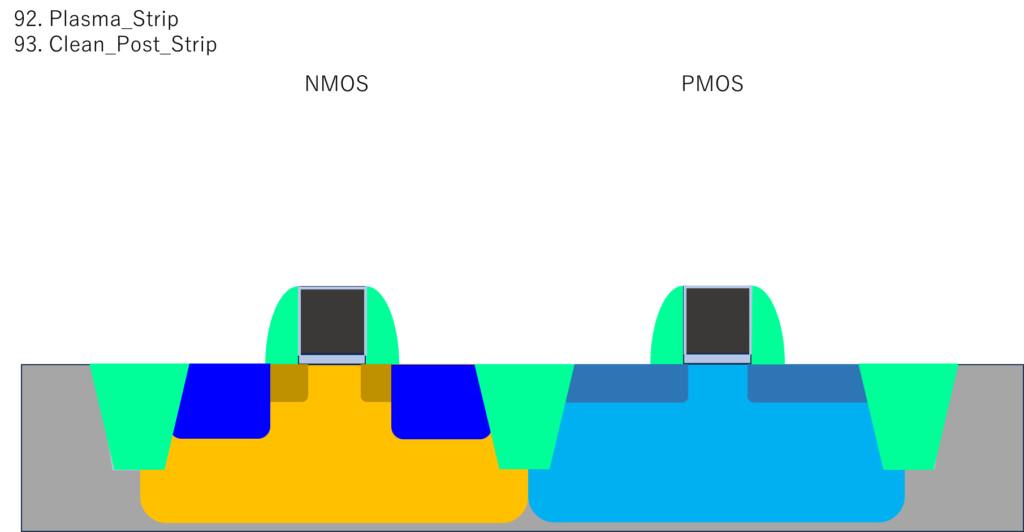

イオン注入が終わると、レジストは除去します。レジスト除去後はこのようになります。

NMOS側のイオン注入が終わったので、PMOS側も同様にイオン注入をしていきます。

PMOS側だけ、レジストで開口をあけてやります。

開口した部分にイオン注入をしていきます。

この時、PMOS側に入れるイオンは、おそらくP(リン)です。

半導体の極性にN型とP型がありますが、注入するイオンの名前にもP(リン)があるんです。

この時はPMOS側にPを打つんですが、PMOS側にPを打ってしまうと悲惨なことになる工程もある(というか、その方が多い)ので、慣れていない方は気を付けてくださいね。

慣れてくると、PMOSでPを打ってはいけない工程はわかってくるんですが、PMOSにPを打つ工程もあるので、最初は難しいところでしょう。

そして、イオン注入用に使ったレジストを除去してやるとこのようになります。

ここまでくると、NMOSとPMOSが対称的な構造をしているのが見えてきます。

今後も、基本的に対称の構造を作ることになります。

このあと、ゲート電極の横にスペーサーを作っていきます。

スペーサーの役割をちゃんと説明するのは難しいんですが、簡単に書くと、スペーサー形成後に高濃度拡散層というものを作ります。

高濃度拡散層は、名前の通り不純物を高濃度に注入して作る領域です。

デバイス的な観点では、高濃度拡散層がゲート電極に近すぎると、トランジスタのオンオフをコントロールするのが難しくなるので、高濃度拡散層とゲート電極の距離を取るためのものだと思ってください。

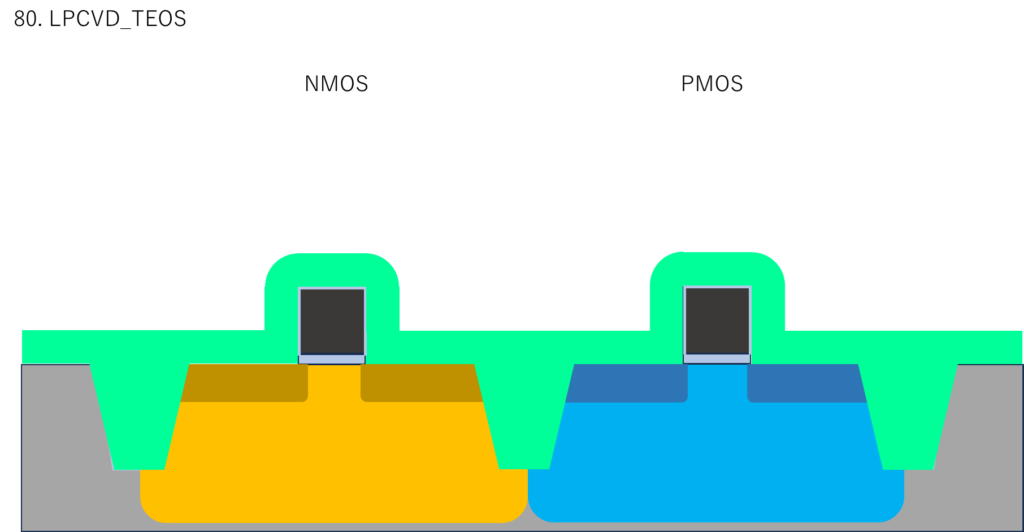

どうも、180nmのモデルプロセスではスペーサーはSiO2で作っているようです。

スペーサーの作り方としては、ウエハの全面にSiO2を成膜して、レジストを付けずに全面エッチングする方法を取ります。

文字で書いてもわかりにくいので、とりあえず全面にSiO2を成膜した図がこちらです。

SiO2はTEOS-SiO2を使っているようです。

TEOSは、テトラエチルオルトシリケートの略で、SiO2を成膜するときの材料として使われます。SiO2を成膜するときの材料は色々あるので、区別するためにTEOS-SiO2と呼ばれることが多いです。

TEOSの話は置いておいて、ウエハ全面にTEOS-SiO2を成膜すると、こんな感じで付くんです。

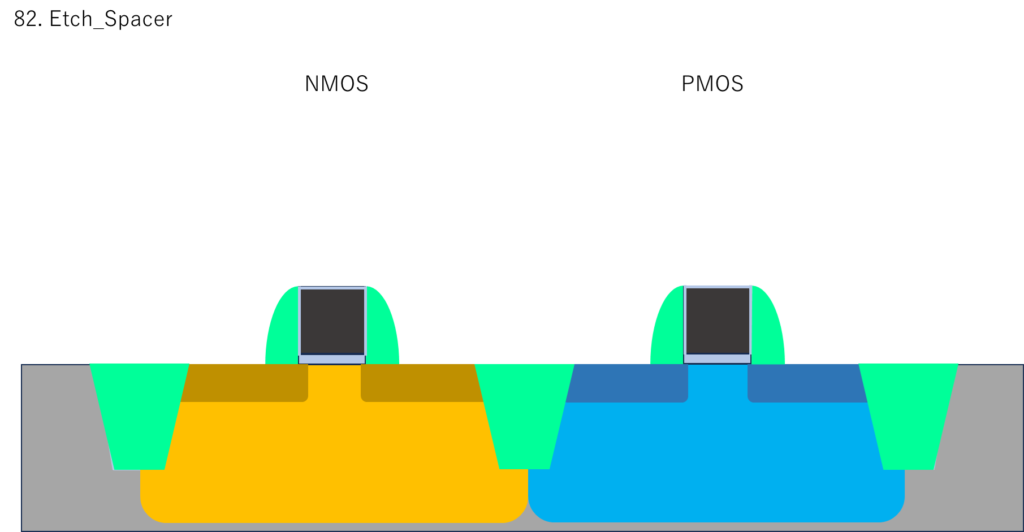

これを、レジストを付けずに全面エッチングすると、どのようになるでしょうか?

答えを書いてしまうと、このようになります。

ゲート電極の横だけ、TEOS-SiO2が残って、他の部分は全てエッチングされてしまいます。

このように、ゲート電極の側部に残ったTEOS-SiO2をスペーサーとして使っているわけです。

スペーサーの幅は、TEOS-SiO2の成膜量とゲート電極の高さで決まるので、その辺をよく考えて設計していないと、えらい目に遭う可能性があります。

実は、もともとスペーサーは、全面ドライエッチングした時にゲート電極のように表面から立ち上がっている構造の側壁部にどうしても材料が残ってしまうことから発見されました。

ウエットエッチングでは形成されないので、ドライエッチングを使った場合特有の形状です。

プレーナー型のトランジスタを見慣れている方であれば、そろそろトランジスタらしく見えてきたのではないでしょうか。

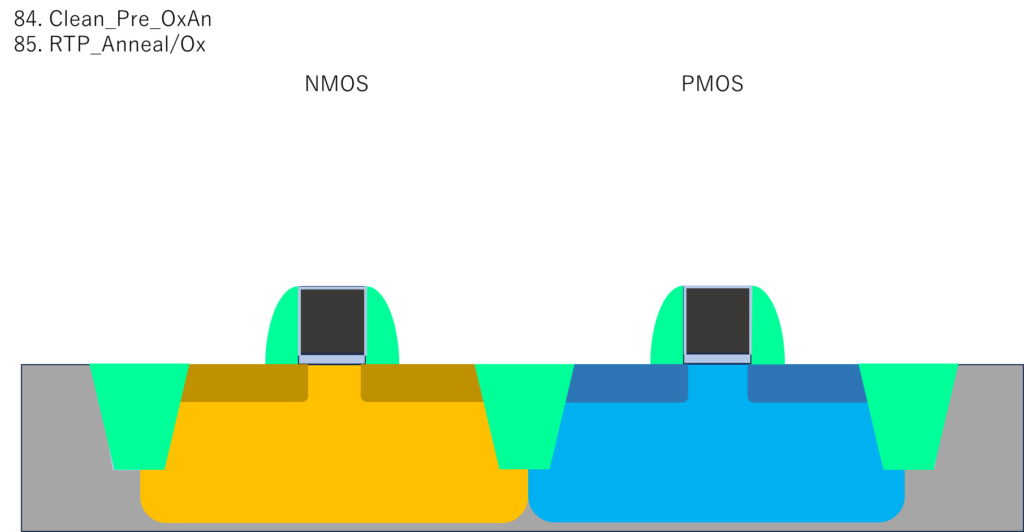

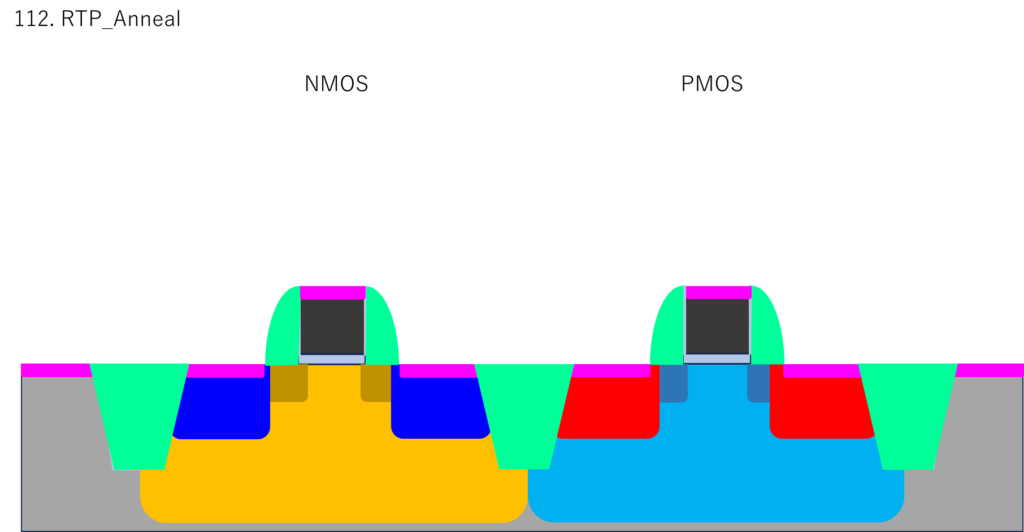

全面エッチングを行って、スペーサーが出来たあと、ウエット処理を行って、RTP_Annealという工程が入れられています。

これは、イオン注入したイオンを電気的に活性化するための工程です。

一般的に、イオン注入を行ったあとは、活性化アニールという熱処理を行わないと、注入されたイオンは働いてくれません。

でも、最初にNMOSとPMOSのWellとChannelのイオン注入をしたあとには、活性化アニールの工程はありませんでした。

これにはちゃんと理由があります。ゲート絶縁膜を作る工程で、一般的な活性化アニールの条件よりも温度が高く長時間の熱処理が行われています。

つまり、WellやChannelのイオン注入のあとは、ゲート絶縁膜の形成工程で活性化アニールを兼ねていたので、明示的な活性化アニールの工程は入っていなかったわけです。

しかし、スペーサー形成前にイオン注入した場合、ゲート絶縁膜の形成工程のような熱処理が無いので、活性化アニールの工程が入っています。

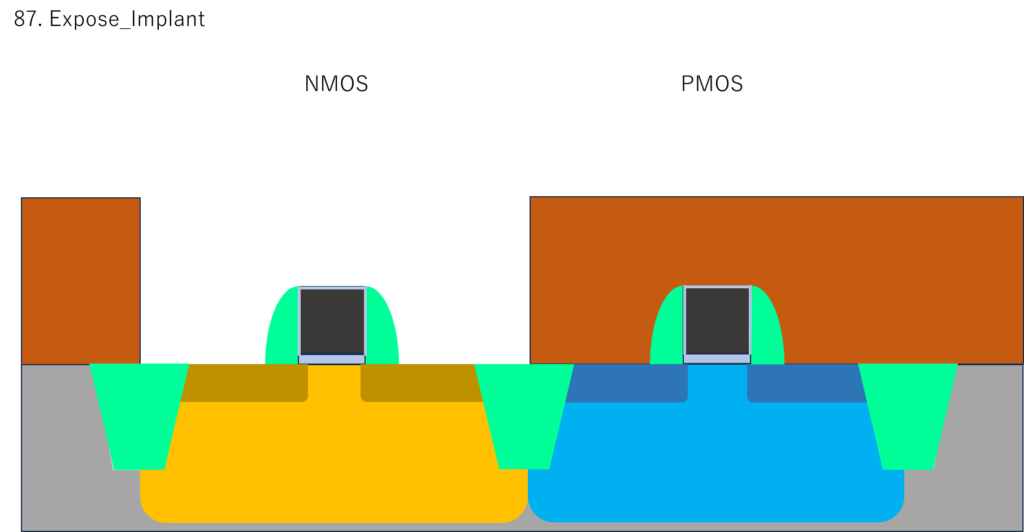

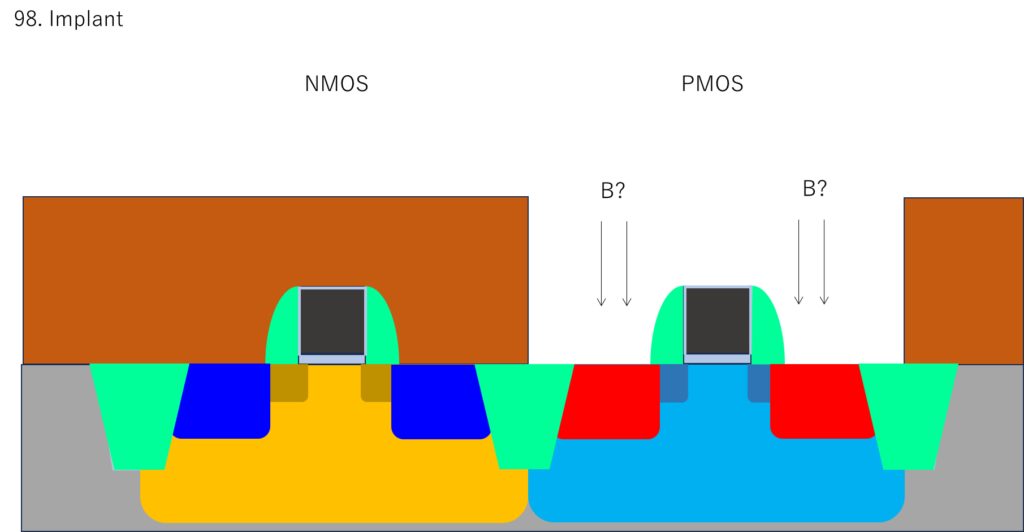

さて、活性化アニールが終わったら、次はNMOS・PMOSそれぞれについて、高濃度拡散層を形成していきます。

高濃度拡散層の形成も、NMOS・PMOSそれぞれ行います。何度もやってますが、NMOS側だけレジストが開口するようにするとこのようになります。

NMOSの開口した部分だけに、NMOS用の高濃度拡散層用のイオン注入を行います。

濃い青色で示しているのが、N型の高濃度拡散層の領域です。

半導体の教科書とかだと、n型の高濃度拡散層をn+と書いてあることもあります。普通の領域よりも、不純物の濃度が高いことを明示的に書いているだけです。

NMOSの高濃度拡散層のイオン注入が終わったら、レジストを除去します。そうすると、このようになります。

NMOSのトランジスタだけ見ると、ある程度完成に近づいています。

PMOS側の高濃度拡散層を作っていないので、次はPMOSの高濃度拡散層を作るために、レジストでPMOS側の開口をあけます。

PMOS側の開口があけられたので、P型の高濃度拡散層のイオン注入をしていきます。

赤色で示した部分が、P型の高濃度拡散層領域です。P型もN型と同様に、p+と書かれることもあります。

(色的に、PMOSの拡散層は濃い黄色なんじゃないのか?と思われた方、大正解です。私も記事を書きながら、色の設定間違えた・・・と思ったんですが、書き直す元気がなく、p+領域は赤色になってます。すみません。)

P型の高濃度拡散層を作れたので、レジストを除去するとこのようになります。

高濃度拡散層のイオン注入がNMOS・PMOSともに終わったので、活性化アニールに入ります。

活性化アニールを行うことで、注入された不純物イオンを電気的に活性化します。

高濃度拡散層を形成するときは、「高濃度」と名前が付く通り、他の工程と比べると不純物を注入する量が非常に多いです。

不純物を活性化ことだけを考えると、十分な温度で長時間熱処理を行うことがベストです。

しかし、熱処理を加えると、シリコンに注入した不純物が拡散しやすくなります。濃度が高いところから低いところに向かって拡散が起こるので、横方向にも縦方向にも不純物が流れていくことになります。

図を見て頂くと、高濃度拡散層はスペーサーとゲートを隔てて向かい合っています。180nmプロセスだと、ゲートの長さは180nm近辺です。スペーサーを含めて考えても多めに見積もって400nm程度でしょうか。

つまり、高濃度拡散層が左右それぞれ200nmずつ拡散してしまったら、トランジスタとしての機能を果たさなくなってしまいます。高濃度拡散層同士が繋がったら、ただの導線といっしょになってしまうからです。

つまり、高濃度拡散層の活性化アニール工程は、不純物の活性化を最大限行いつつ、拡散は最小限に留める必要があるという、トレードオフの関係をうまく両立する必要があるわけです。

この辺のノウハウは、各社持っていらっしゃるんでしょうね。

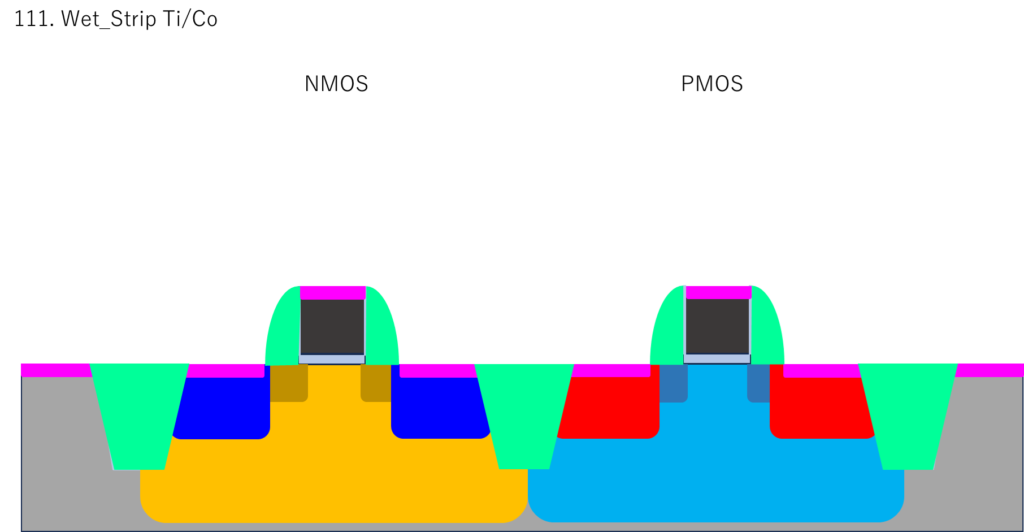

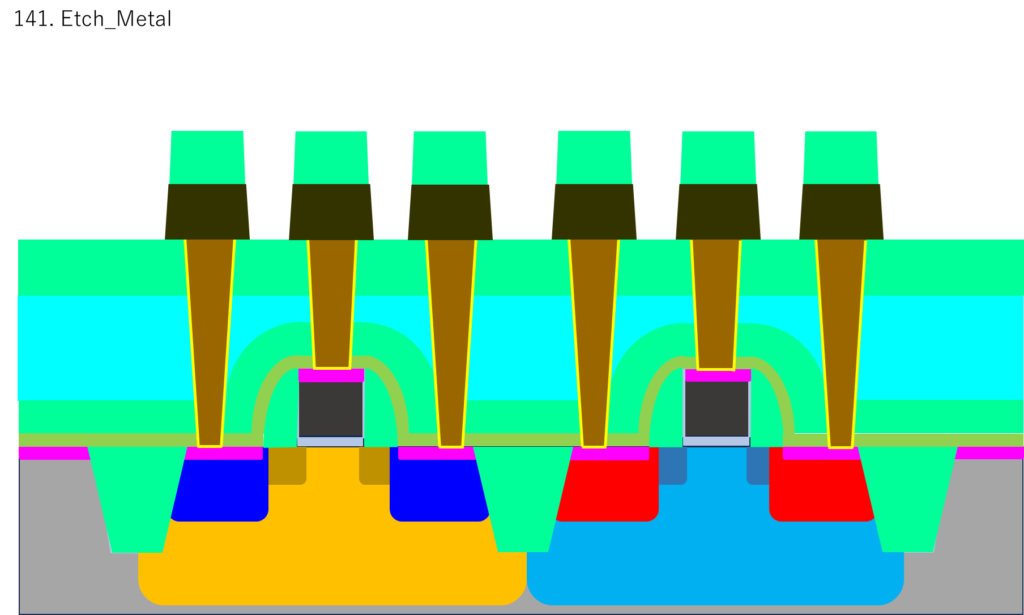

高濃度拡散層の形成まで終わりましたが、このあとシリサイドを形成するプロセスに入ります。

シリサイド形成~コンタクト形成

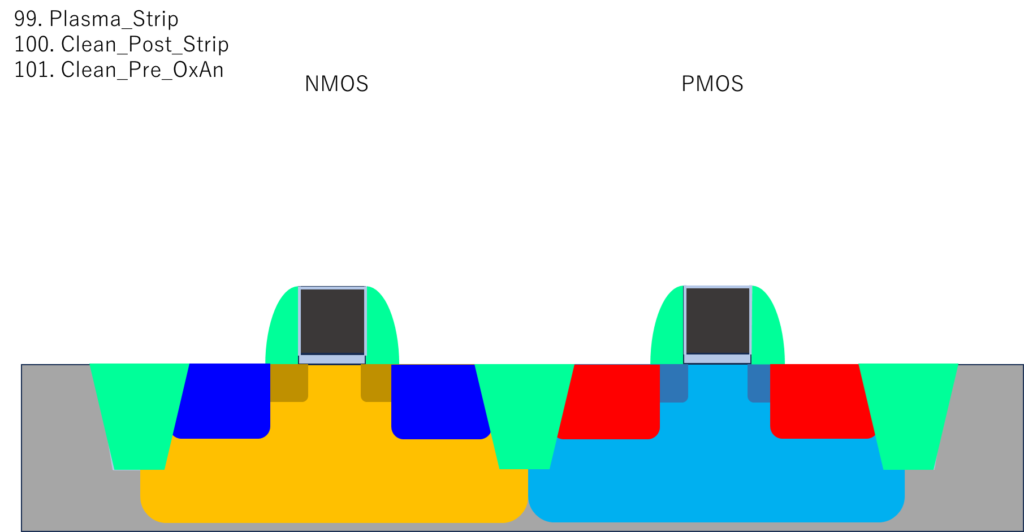

シリサイド形成に入る前に、とりあえず薬液処理が入ります。

この時に、シリコン基板表面の酸化膜を除去しておくのが重要です。

ちなみに、シリサイドというのは、金属とシリコンが反応してできる金属とシリコンの化合物です。

シリサイドを使う理由としては、シリサイド化した領域はシリコン自体よりも抵抗が下がることが一番大きいです。

シリサイドを形成する金属は、W(タングステン)・Ti(チタン)・Co(コバルト)・Ni(ニッケル)などがありますが、180nmプロセスだとCoシリサイドが使われているようです。

たしか、一番最初にシリサイドを作るために使われたのは、Tiで、その次がCoで、もっと先端プロセスではNiが使われているはずです。

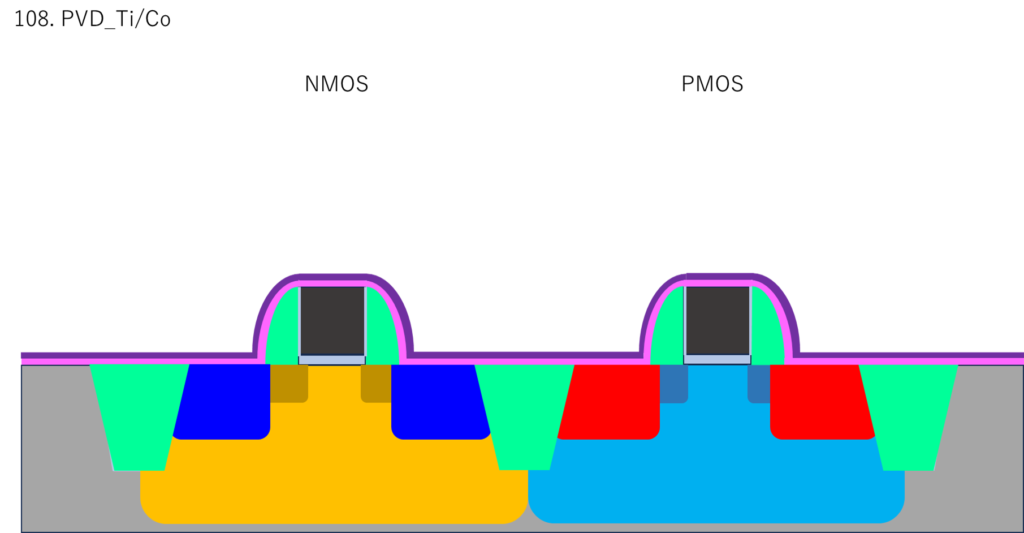

今回は、Coシリサイドのプロセスです。シリサイドを形成するために、全面にTi/Coを成膜します。

全面に金属膜を付けてしまって大丈夫なのか?と感じますが、これが大丈夫なんです。

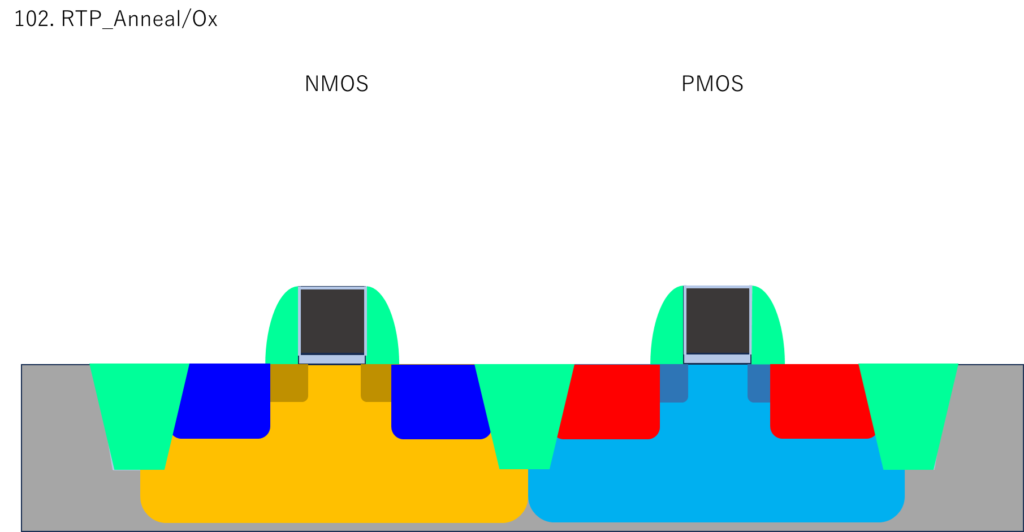

シリサイドプロセスは、金属膜成膜→アニール→未反応の金属を除去→再度アニールのように進みます。

基本的に、金属はシリコンとしか反応しませんし、金属膜が残っていても除去してしまうので、問題ないわけです。

というわけで、1回目のアニールをやってやるとこのようになります。

ちょっとマニアックですが、シリコンと触れている部分はコバルトシリサイド(CoSi)になっていて、絶縁膜上(STIの上やスペーサー上)は金属が反応せずに残っている状態です。

反応せずに残っている金属膜を除去すると、このようになります。

シリコンが出ていた部分だけに、シリサイドが形成できていることがわかります。

金属を除去したあとに、安定化のためにもう一度アニールを行います。

ここまでくると、シリサイド形成まで完了しました。

トランジスタの形成はここまでで終わりです。このあと、各電極に配線をつないでいく、配線工程に移ります。

MOSトランジスタには、ソース・ドレイン・ゲートの電極があるので、まずはそれぞれの電極にコンタクトを取ってやる工程です。

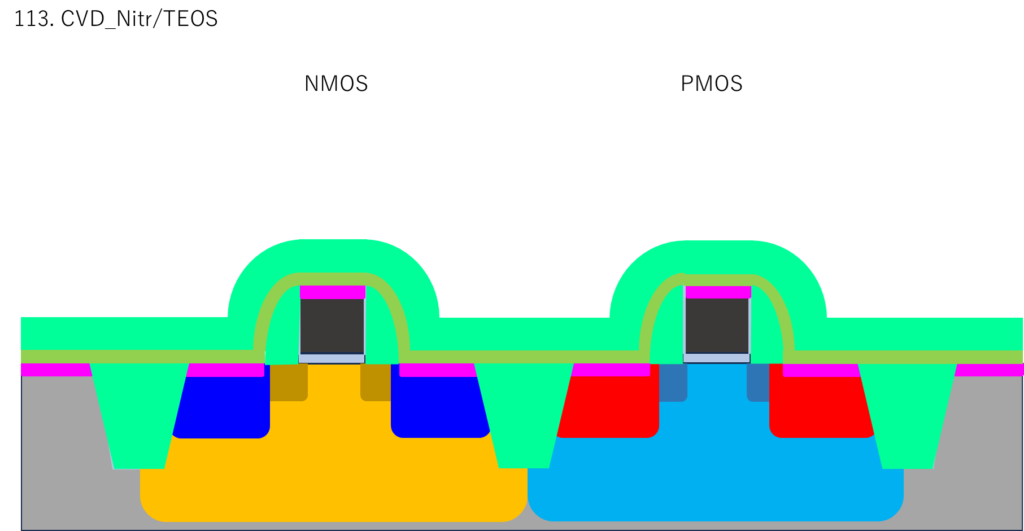

配線を作ってやるうえで、トランジスタの上に絶縁膜を積んでやる必要があります。

膜厚の情報はモデルプロセスに書いてなかったので、適当にかいています。

実際にプロセスを立ち上げるうえでは、この辺の膜厚設計も大事なんですけどね。

最初にSiNをつけて、そのあとTEOS-SiO2をつけているのがミソなんです。(理由はあとでわかります。)

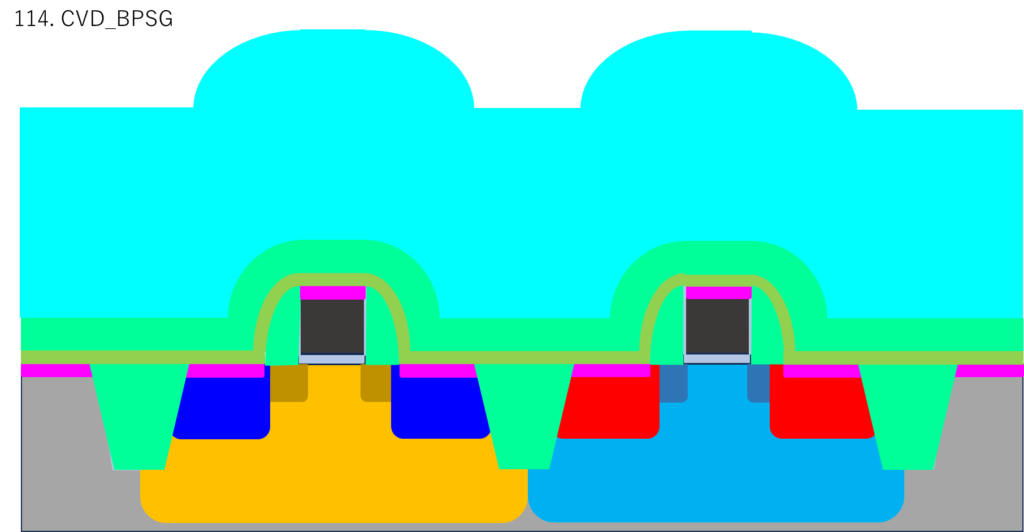

絶縁膜を積み増すために、SiO2系のBPSGを使っています。

BPSGは、B(ホウ素)とP(リン)を多く含んだガラスです。流動性が良いみたいです。その反面、不純物が多く含まれているので、不純物の析出や吸湿性などが問題になることがあります。

BPSGなので、もう少し平坦になるでしょうが、トランジスタの配線工程でCMPが使われる理由を書きたかったので、大げさに描きました。

トランジスタ(正確に表現するとシリコン基板上の段差)があると、絶縁膜を積んでもある程度の凹凸ができてしまうんです。

これを解消するために、CMPが使われす。

モデルプロセスでは、CMPを掛ける前に膜の焼き締めを行うプロセスが入っています。

BPSGだと、膜質自体はあまり良くないでしょうから、焼き締めが必要なんでしょう。ここの膜が、カッスカスだとあとで困ります。

ここまで来たら、CMPを掛けて表面を平坦化します。

マニアックな話ですが、ここのCMPをどこで止めるか?というのは、モデルプロセスを見ただけではわかりませんでした。

というのは、ここのCMPをゲートの頭で止める方法と、絶縁膜の途中で止めるのと2パターンあるんですが、プロセスの安定性という意味では、ゲートの頭で止めた方が良いのではないかと私は思っています。

ただ、CMP_BPSGとしか書かれていないので、BPSG領域でCMPを止めるのかなぁと思って、途中止めの絵にしています。

次の工程で絶縁膜を積み増しているので、ゲートの頭止めなんじゃないかなぁと思いつつ、この辺はCMP工程単独で決まるわけではなく、他の工程との兼ね合いで決まるので、一概にどれがいいとは言えないです。

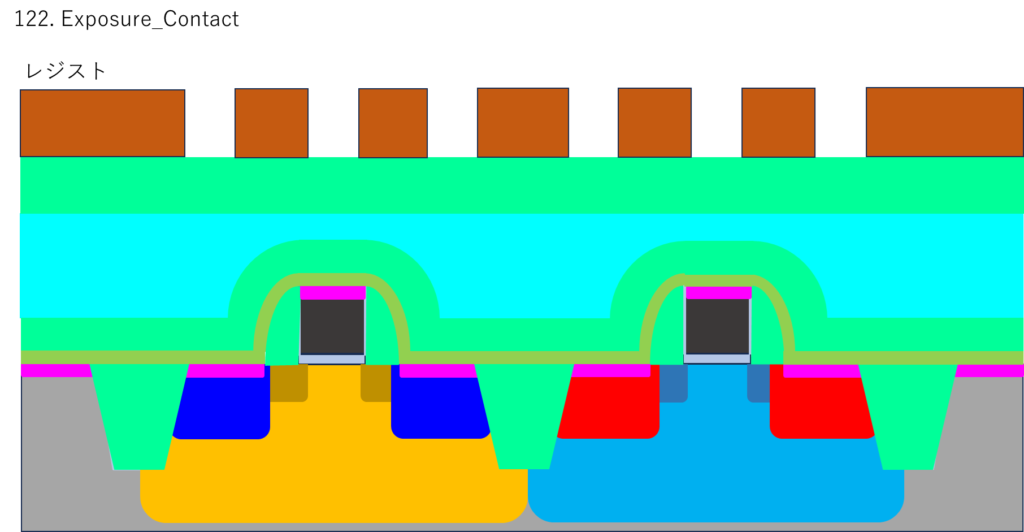

CMPを行ったあと、CVDで絶縁膜を積み増しています。これで、ソース・ドレイン・ゲート電極にコンタクトを取る準備はできました。

ここからは、それぞれの電極にコンタクトを落としていきます。

NMOS・PMOSのそれぞれの電極にコンタクトを落とせるように、リソグラフィーで小さな穴をあけます。

模式的に書いているので、ソース・ゲート・ドレインへのコンタクトが横に並んだ絵になっていますが、通常は横一線に並ぶことはありません。

このコンタクトも、トランジスタの中で小さな寸法が要求される場所の一つです。180nmプロセスでは、248nmのKrFの露光機が使われていたようです。

とりあえず、リソグラフィーで穴をあけることはできたとして、いよいよコンタクトを形成していきます。

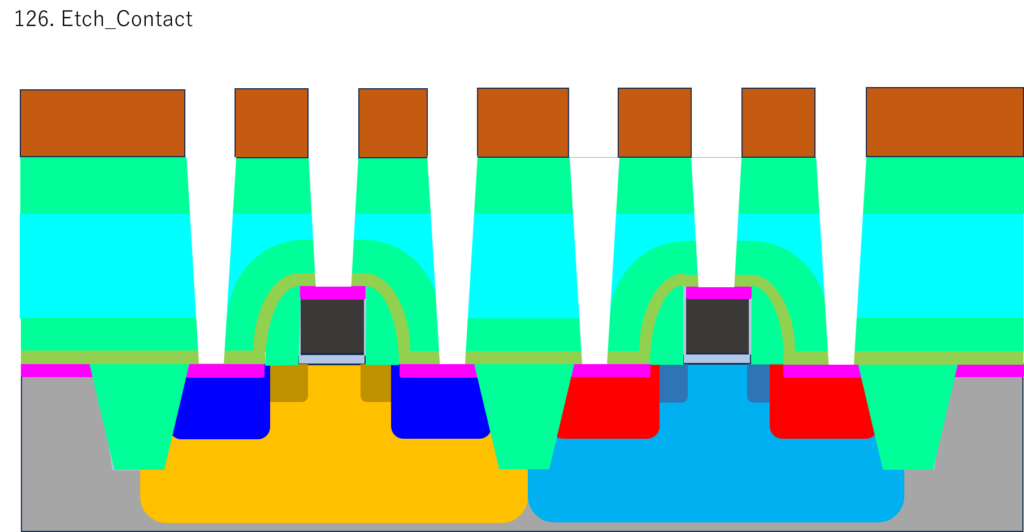

レジストで形成したパターン越しに、コンタクトを取るための穴を掘っていきます。

図の中で、穴にテーパーがついた形になっているのはわざとです。

コンタクトの穴は小さいので、どうしてもエッチングするとテーパーがついてしまいます。つまり、レジストの開口よりも電極にコンタクトしている部分の方が狭くなります。

あとは、ソース・ドレインの部分と、ゲートの部分ではゲート電極の高さの分だけ穴が浅くなっています。

この辺の高さ違いに対する調整のために、SiN層があるんです。

何を言っているのかというと、何も考えずにSiO2とSiNに選択比を持たない条件でエッチングしてしまうと、ゲート電極の部分は過剰にエッチングされてしまうことになるということです。

しかし、過剰にエッチングしてしまうと、ゲート電極部に形成されたCoSi層をエッチングし続けることになるので、あまり良くありません。

そこで、SiO2とSiNに選択比を持たせた条件で最初にエッチングしてやります。そうすると、ゲート電極部もソース・ドレイン電極部もSiO2膜までのエッチングで止まり、SiN膜が残った状態を作ることができます。

そして、最後にSiN膜をエッチングするようにしてやると、ゲート部とソース・ドレイン部の両方に対してオーバーエッチングを減らした条件でコンタクトを形成することができます。

シリサイドを形成したあと、SiN膜をつけてからSiO2をつけていたのは、このためです。

プロセスインテグレーションに関しては、前の工程から種を仕込んでおかないと対応できない部分などがあるので、難しさもあり、面白さでもあると思います。

1つの工程だけを見ていても、気づけないような課題が出てきたりするので、経験が無いとなかなか難しいとは思いますが。

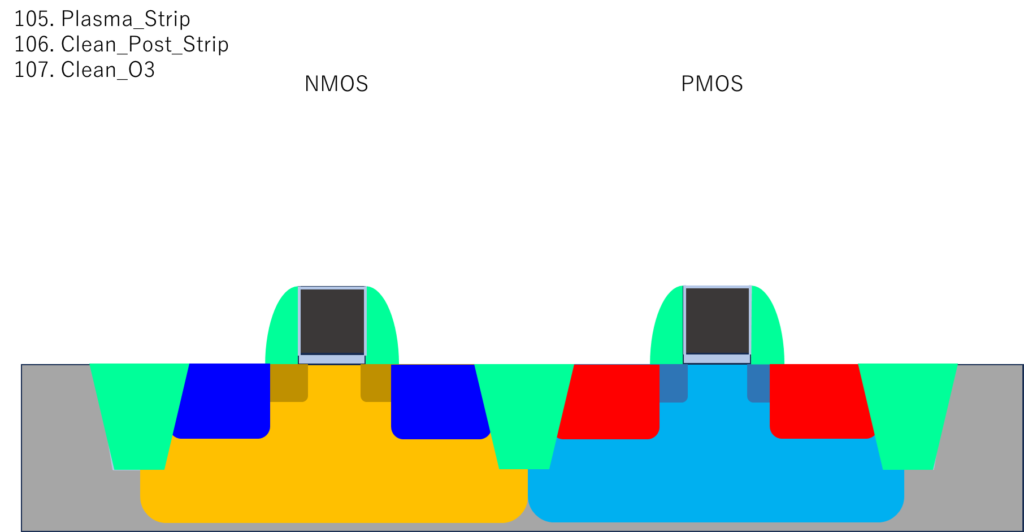

さて、コンタクトの話は少しマニアックになりましたが、穴を無事あけることができたら、レジストを除去します。

これで、コンタクトの穴をあけることができたので、次は穴の中に金属を埋め込むことになります。

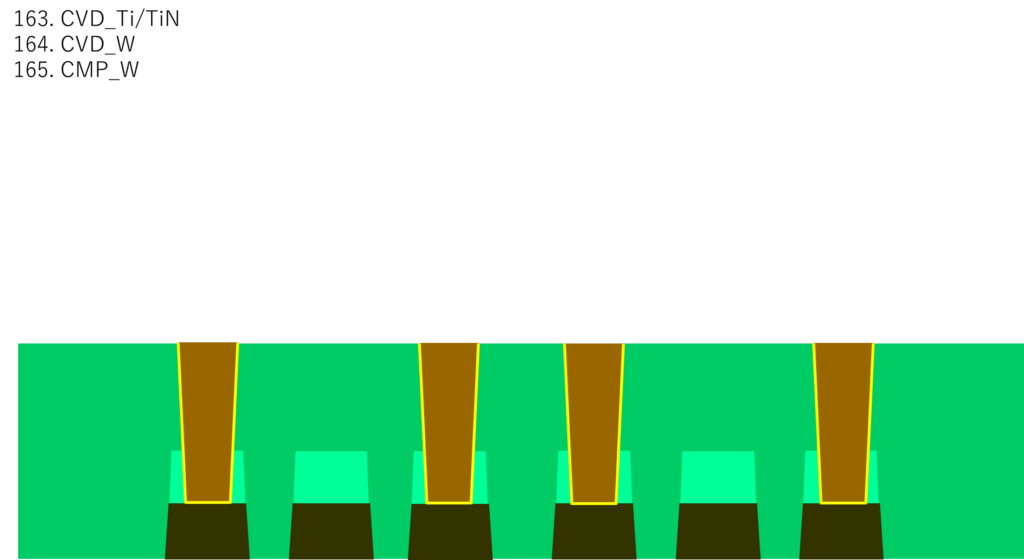

穴の中に金属を埋め込むんですが、180nmのモデルプロセスの場合、メインの埋め込み材にはWを使っているようです。

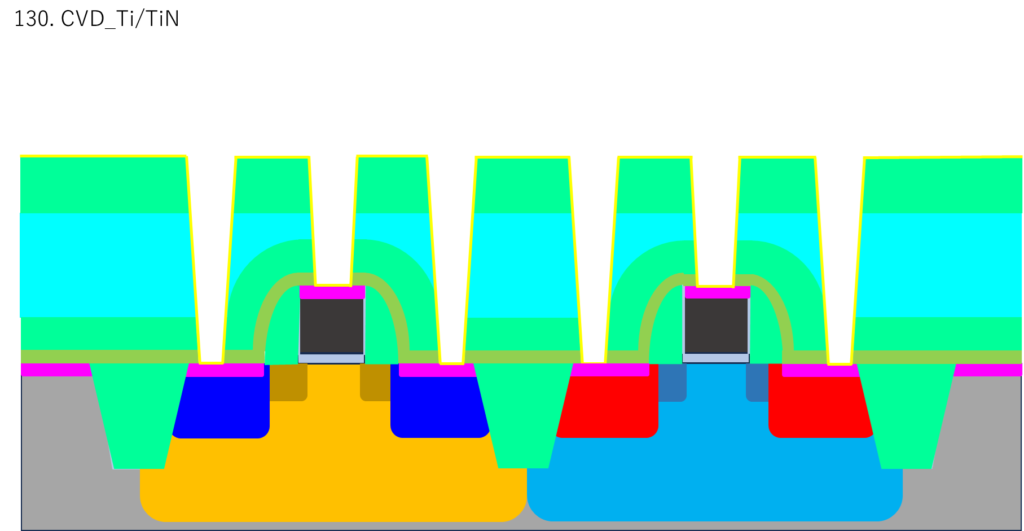

Wでプラグを作る場合、Ti/TiNをバリアメタルとして貼ってからWを埋め込むのが普通です。

というわけで、Ti/TiNを成膜するとこのようになります。

Ti/TiNをわざわざバリアメタルにしている理由は簡単で、Wが拡散していかないようにするためです。

一応、Ti/TiNはCVDで成膜できるので、穴の側壁にも形成可能です。PVDになってしまうと、穴の側面のカバレッジは低いでしょうし、穴底の膜厚も薄くなってしまうので、CVDで成膜できるのはメリットでしょう。

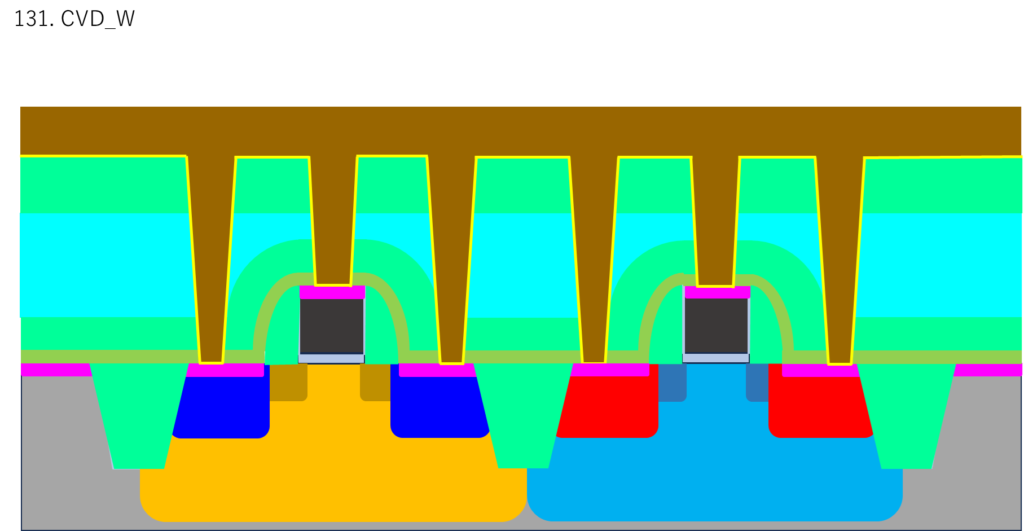

Ti/TiNのバリアメタルが成膜できたら、Wの埋め込みを行います。WもCVDで成膜できます。

図は雑に書いていますが、Wもちゃんと穴の中まで成膜できるような条件にしないと、プラグの途中にボイドが形成されてしまったり、最悪の場合、配線がオープンになってしまう可能性もあります。結構シビアです。

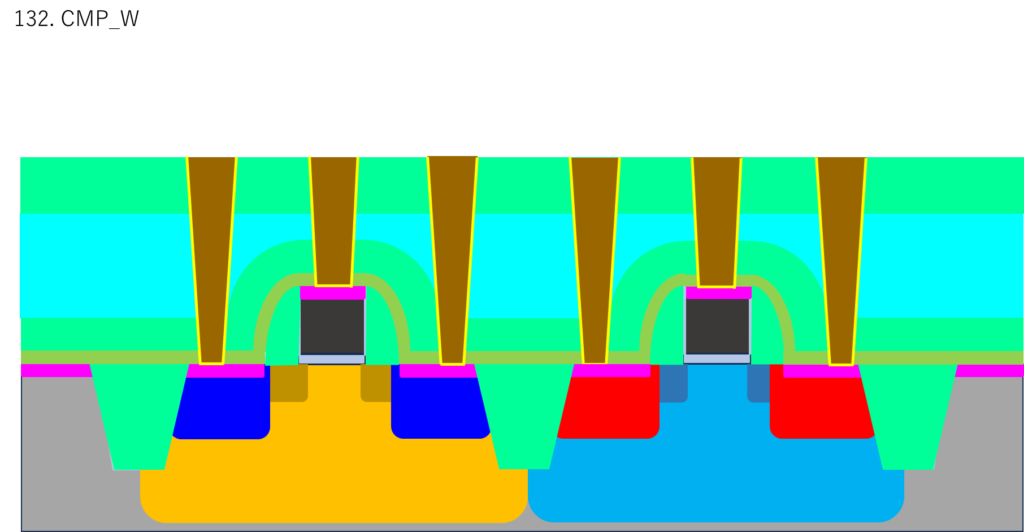

図に示している通り、Wを成膜した状態では、全部のコンタクトプラグがショートしているので、ここからCMPを行っていきます。

これで、コンタクトプラグの形成まで行うことができました。

ここまで来れば、あとはコンタクトプラグから上の配線層の形成工程を残すだけです。

ちなみに、コンタクトプラグと1層目の配線はデュアルダマシンで形成するのでは?と思われた方がいらっしゃるかもしれませんが、180nmプロセスではシングルダマシンで作られていたようです。

デュアルダマシンの方がちょっと手が込んでいて、プロセス的には複雑になりますが、やっていることは穴と溝を掘って金属を埋めることなので本質的には変わりません。

配線工程

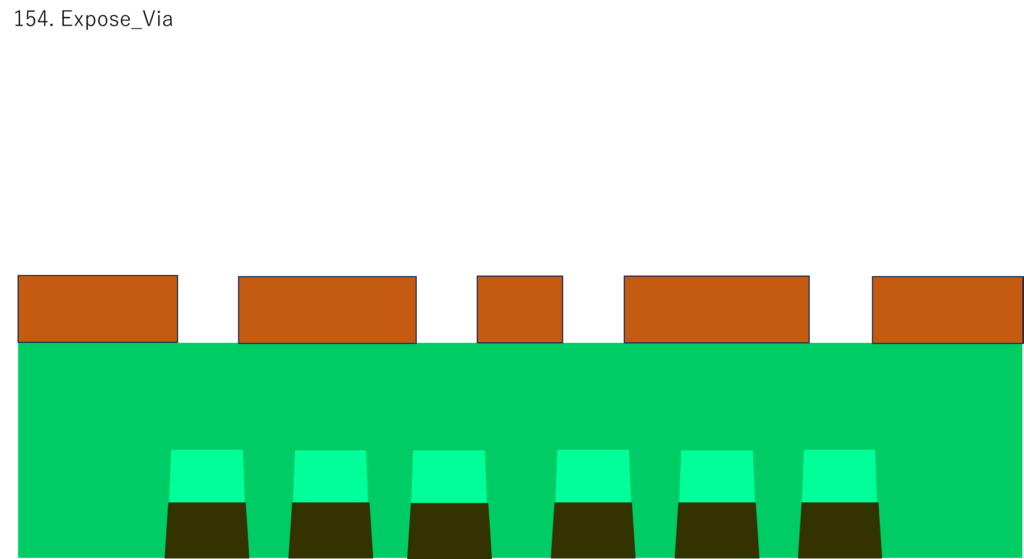

ここからは、トランジスタの電極から引き上げたコンタクトをつなげる配線を作っていく工程です。

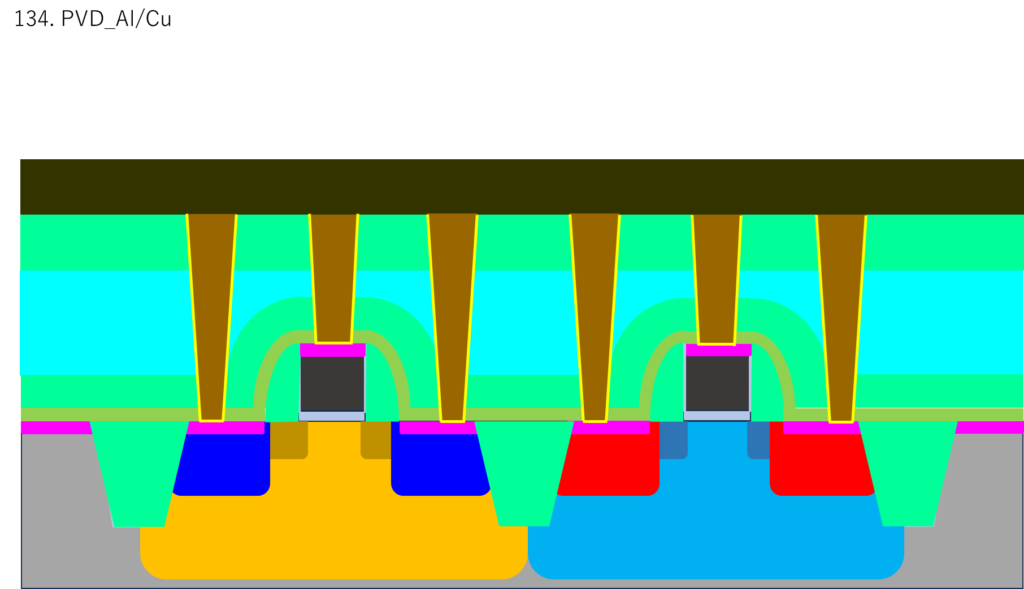

180nmプロセスでは、Al/Cuの配線が使われていたようです。

コンタクトプラグから引き上げた1層目の配線には、Al/Cuを使っています。

PVDで積んでいるようです。Al/CuのPVD配線は、イマイチ理解できていない部分がありますが、とりあえずPVDで積んでいきます。

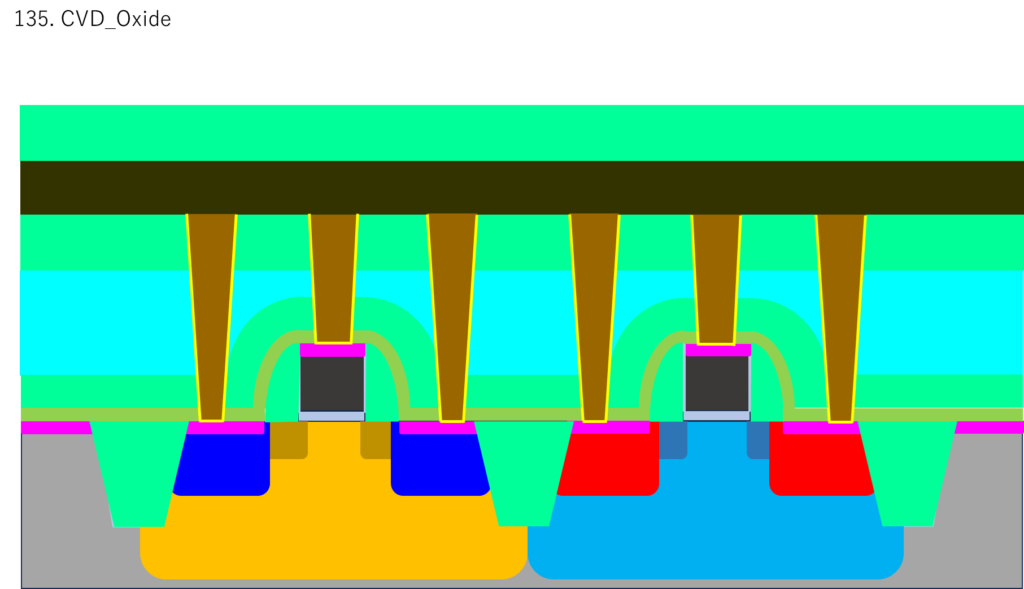

Al/Cuを積んだあと、CVD-SiO2を積みます。おそらく、エッチング時のハードマスクとしてSiO2を使っているんだと思われます。

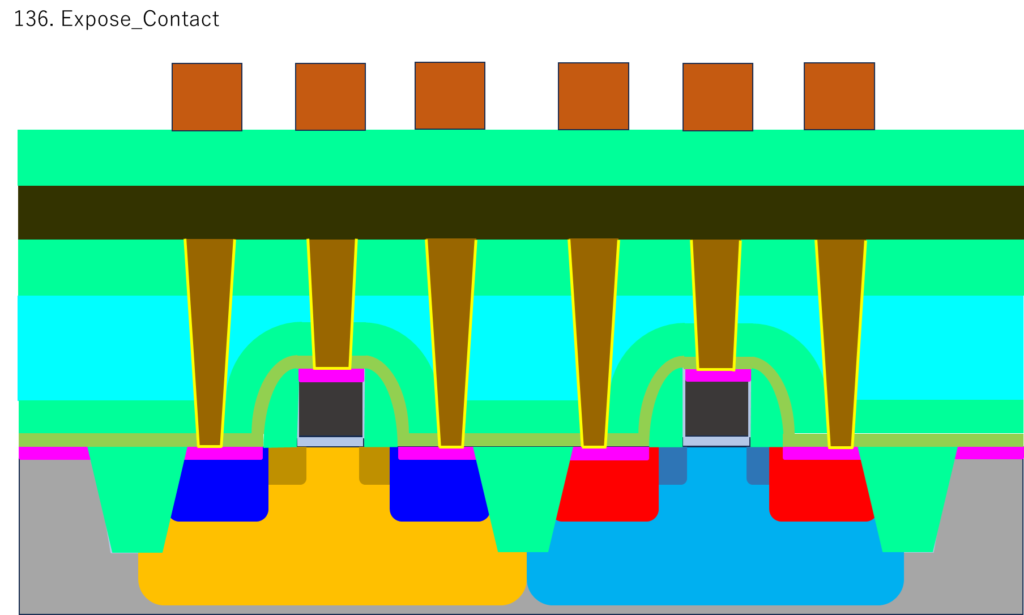

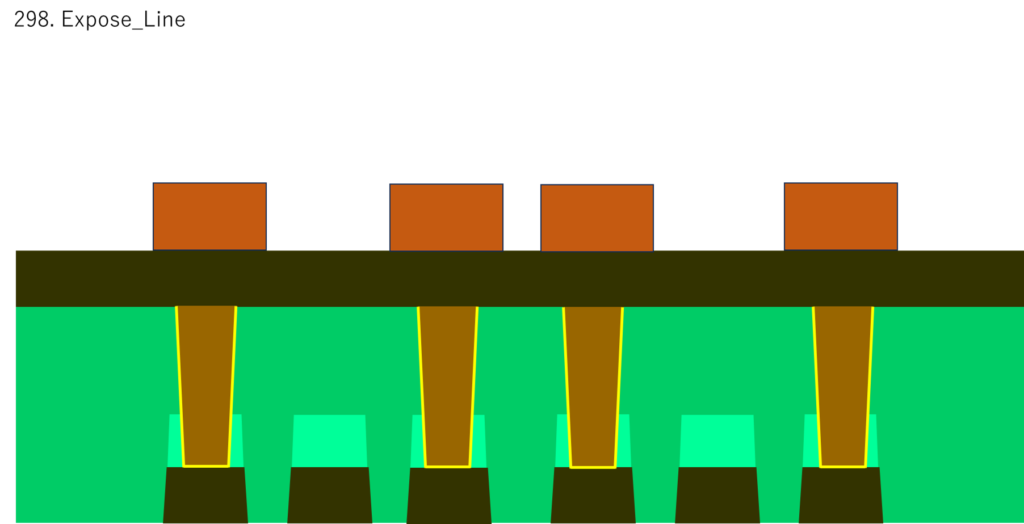

ハードマスクとしてのSiO2を積んだら、リソグラフィーで配線の幅に露光していきます。

SiO2ハードマスクを使うので、配線の部分にレジストが残る形で露光する必要があります。

デュアルダマシンだと、配線の部分がレジストだと開口になるので、逆のパターンです。

(なぜこんなことを書くかというと、ダマシンプロセスだと基本的にエッチングする部分が開口なので配線部分=開口のイメージがあって、何度も図を描き直す羽目になったからです。。。)

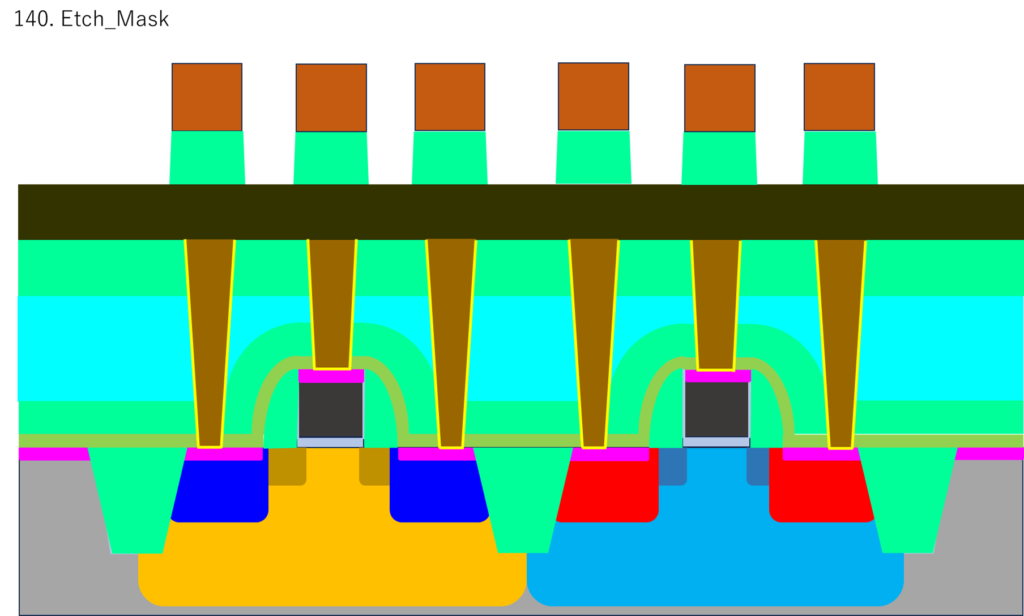

レジスト越しにSiO2ハードマスクをエッチングすると、このようになります。

そして、今度はSiO2ハードマスク越しにAl/Cuをエッチングしていきます。

図としては、下地の絶縁膜にビタ止めで描いていますが、エッチング残りがあると、配線間がショートしてしまうので、オーバーエッチを掛けて、絶対に抜け残りがない条件にしないと、えらいことになるのが見えます。

ここで、なぜレジストマスクでAl/Cuを直接エッチングしないのか?と思われる方もいらっしゃると思います。

理由は簡単で、Al/Cuがエッチングしにくいので、レジストだと持たないからです。要は、Al/Cuをエッチングしようと思っているのに、Al/Cuより先にマスクにしていたレジストが無くなってしまったら、配線を切ることができないわけです。

お気づきの方はお気づきかと思いますが、特にアッシングはしていませんが、エッチング終了時点でレジストが無くなっている図にしています。(細かい芸です。本当はレジスト残渣が残っているので、こんなにきれいに取れるわけではないですが。)

配線のエッチングのあとに、wet処理が入っています。ここで、ハードマスクにしたSiO2をどうしているのかよくわからないんですが、仮にエッチングしてしまうと、下地のSiO2系の膜も溶けてしまうので、そのまま残しているのではないかと思って、図のような表記にしました。

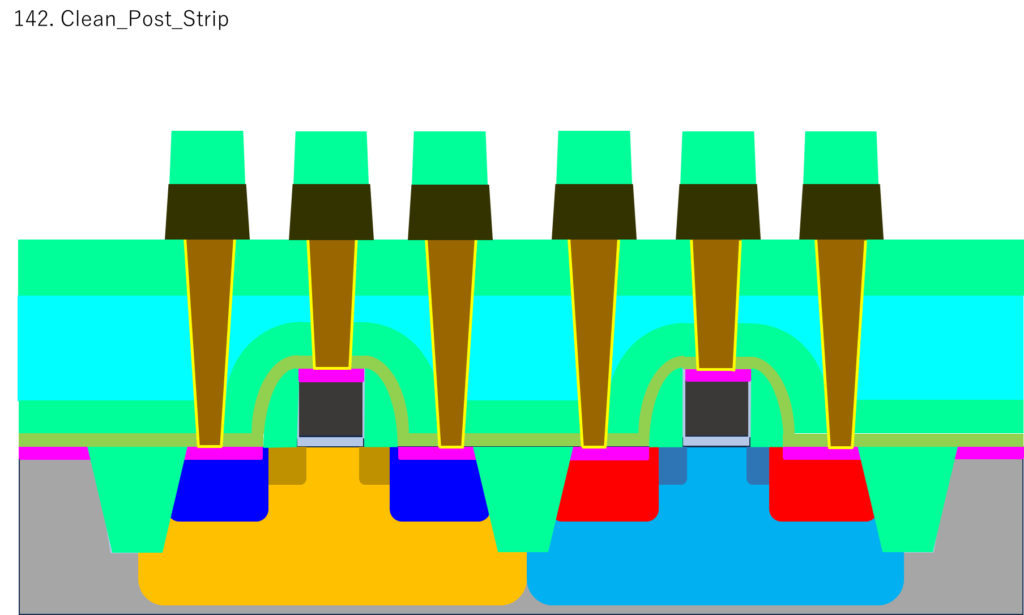

そして、Al/Cuの配線にアニールを掛けて、薬液処理で洗浄してやることで配線を切ることができました。

配線と配線をつなぐ縦の穴をVia(ビア)と呼ぶんですが、次の工程ではViaを作っていきます。

やっていることは、コンタクトを形成した時とほとんど同じです。

ここからは、スペースが無くなってきたので(私が図を描いているppt上の話です)、直下の配線だけ描くようにしています。

配線の上に、CVDで成膜を行います。ILDと書かれているのは、Inter Level Dielectricの略で、日本語だと層間絶縁膜です。

(Inter Layer Dielectricかと思っていましたが、Semi-netにはLevelの方が書いてありました。)

そして、絶縁膜をCMPしてやります。(図を描くときに手を抜いてしまいましたが、配線が形成されている以上、ILDの表面にも凹凸があるはずですね・・・)

CMPして、平坦化してやったら、Viaを形成していきます。Via向けに、リソグラフィーで穴をあけていきます。

模式的に描いているので、Viaを落とす場所は適当です。本当は、配線がつながるように設計されています。

Viaの穴をレジスト越しにエッチングしていきます。ここは、コンタクトプラグの時と同じです。

ここまであまり触れていませんでしたが、リソグラフィーの時に、位置合わせをしなければいけない下層とのずれをどの程度許容するかということも、各工程で必要になるんですよね。

配線工程は、配線同士がちゃんと接続できていないと、オープンになってしまうので、リソの合わせをどこまで許容するのか?というのも実際上は重要になってくると思われます。

Viaのエッチングが終わったら、レジストを除去してやります。

この時、下の配線層の金属との接続を確実にするために、金属の洗浄工程が入っています。

このあとは、Ti/TiN/Wの埋め込みを行って、CMPしてやればViaの完成です。

コンタクトの部分とプロセスは全く同じなので、CMP後の図を描いています。

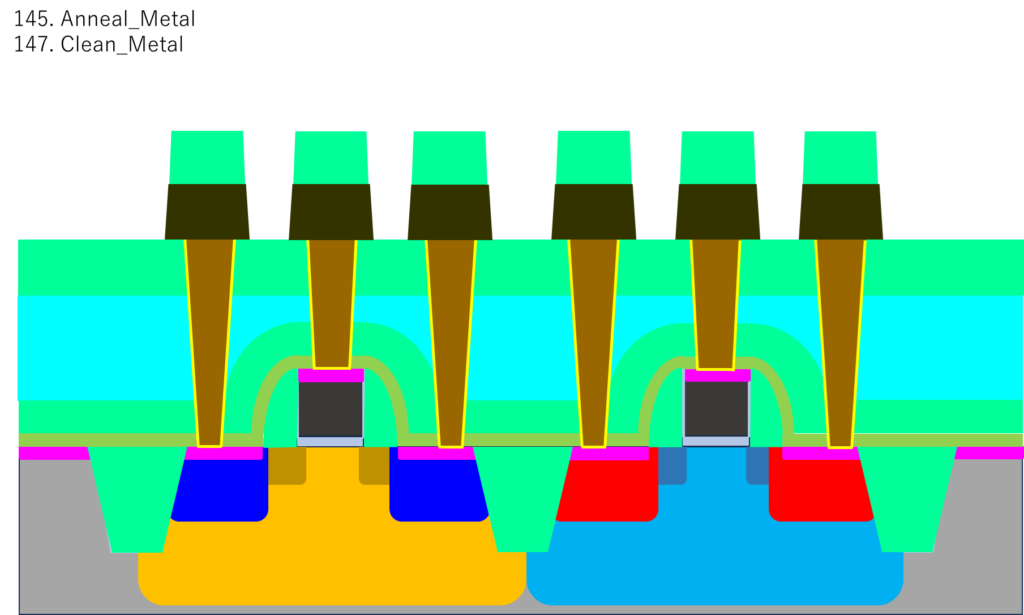

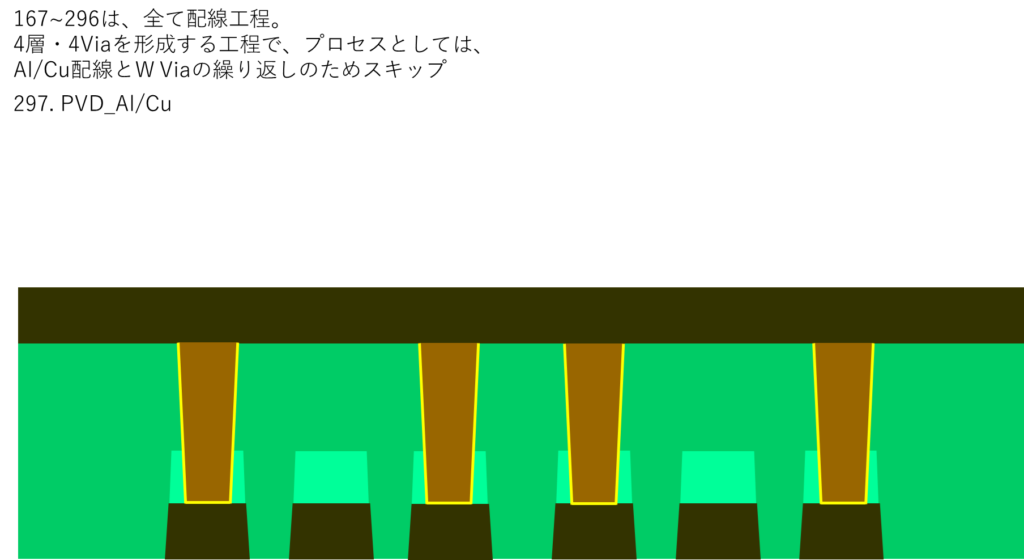

ここからも、配線工程は続くんですが、Ti/TiN/WのVia形成とAl/Cuの配線形成の繰り返しなので、プロセスとしてはスキップします。

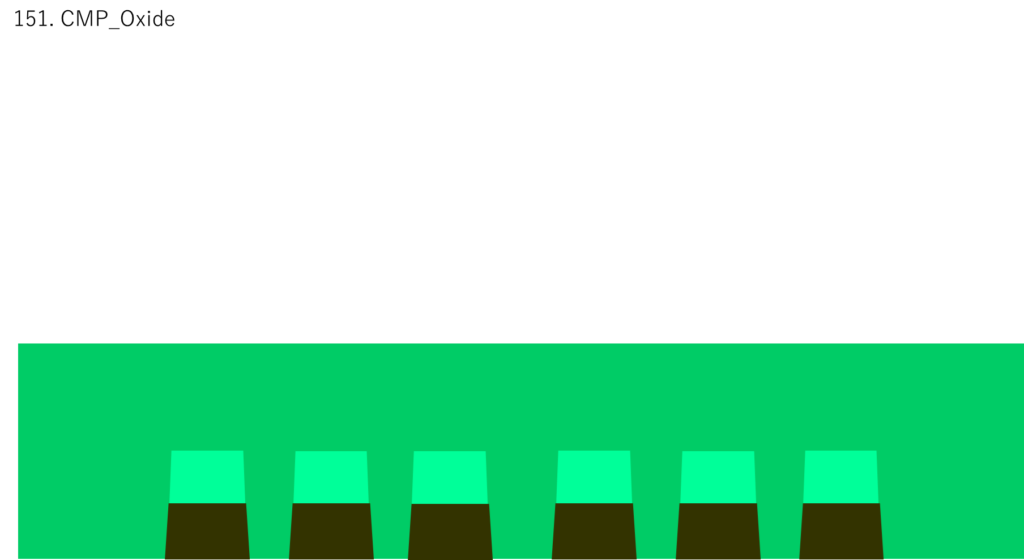

167工程目から296工程目までは、全て配線工程です。4層・4Viaのプロセスです。

配線工程にも意味はありますし重要なんですが、プロセスとしては繰り返しになるので、変化がある297工程目に飛びます。

297工程目は、最後のViaの上にPadを作る工程です。

Al/CuをPVDで成膜しています。

その後、Al/Cu上に直接レジスト塗布して、Padを形成するようにしています。

この部分だけ、SiO2ハードマスクを使っていないのは不思議に思われるかもしれません。

おそらくですが、Padのサイズ感が大きいので、ラフな線幅の露光工程が使われていて、厚膜のレジストが使われているからではなかろうかと推定しています。

Al/Cuの上に直接レジストで開口しているので、エッチングするとこのようになります。

これで、コンタクト用のPadを切ることができました。

レジストを除去したあと、金属配線用の熱処理を行って、金属配線の洗浄を行います。

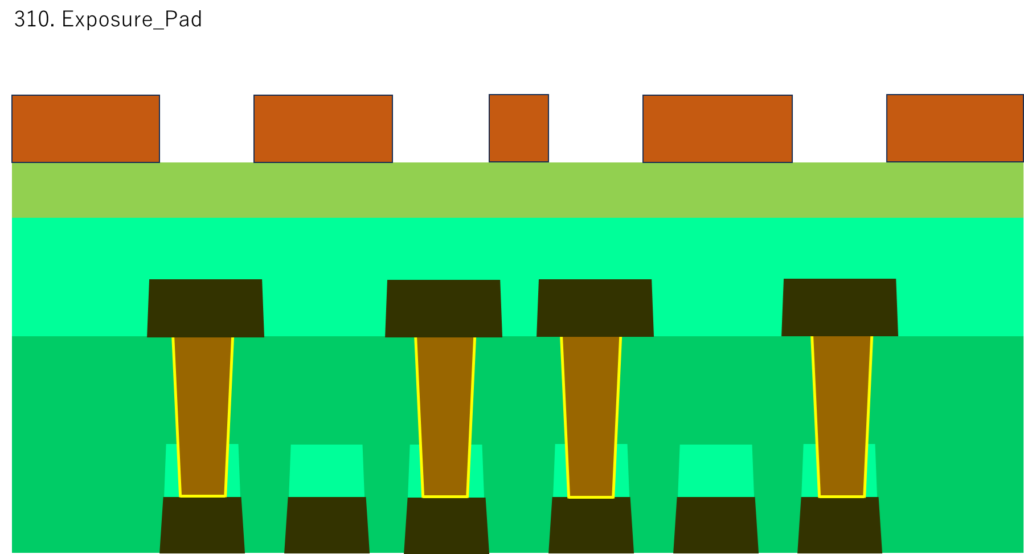

最後に、SiNとSiO2の積層膜でPad部の開口を作ります。

Pad開口用のパターンをレジストであけます。

Pad部分の絶縁膜をエッチングしてやると、Pad部分が開口することができます。

その後、レジストを除去してやって洗浄を掛けてやると、最後のプロセスにたどりつきます。

315工程目のアニールは、通常FGA(フォーミングガスアニール)が行われます。

シリコンを使う場合は、よく使われています。

これで、315工程の全てが完了しました。読者の皆様から見ると、長かったでしょうか、短かったでしょうか。

私は、図を描きながら、300工程でも長いなぁと感じました。途中の配線工程を飛ばしたので、実質150~200工程くらいですが、1つ1つプロセスを追っていくと長いですが面白かったです。

プロセス自体の解説は、ここまでです。

20年前のプロセスだと思って侮ることなかれ

さて、180nmのモデルプロセスに沿って、1工程目から最後の工程まで断面を考えてみました。

1から描いて感じましたが、1つ1つのプロセスには意味があるということです。

あとは、前工程と言っても、フロントエンドと配線工程では、毛色がかなり違いますね。

フロントエンド側は、シリコン基板に対してアプローチしていく方向性ですが、配線工程は絶縁膜や金属をどう扱っていくのかという方向性の考え方になっているような気がします。

また、180nmプロセスは20年以上前のプロセスなので、現代ではレガシーと扱われる世代ではありますが、CMOS製造の基本的な考え方は変わっていないなと感じました。

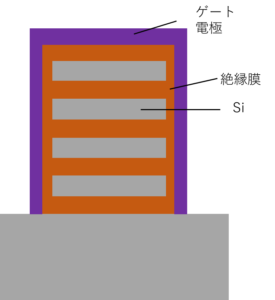

先端ロジック半導体は、FinFETやナノシート構造になっているので、もはやプレーナー型とは似ても似つかぬ構造になっています。

しかし、STIを用いる構造や、配線領域をどう作るかなどは、前の世代のコンセプトを引き継いでいる部分が大いにあると思います。

先端ロジックのプロセスは1000近くあると言われていて、理解するだけでも大変なので、180nmくらいのプロセスで基本のコンセプトを学んだ方がいいのではないか?と思いました。

最後に、これは半導体デバイスメーカーで働かれている方がもしみていたら、という仮定の上でのメッセージです。

今回の記事は、180nm世代のモデルプロセスの概要を簡単に解説することを目的にしています。

本当は、成膜する膜の膜厚・エッチング加工する場合の形状寸法・イオン注入条件・成膜する膜の処理温度等々、考えなければいけないパラメータはたくさんあります。

あくまでも全体の流れはこんな感じですという意味合いだけです。少しでもためになったと思っていただけたら幸いです。

まとめ

この記事では、180nm世代のCMOSプロセスを断面に焼き直していくことで、CMOSのプロセスを解説しました。

いや、図描くだけで大変でした。それでも、これが役に立ったと思っていただける方が1人でもいらしたら、幸いです。

記事の内容に明らかな間違いや、誤植、誤解を招く表現等がありましたら、コメントかお問い合わせフォームでご連絡いただけるとありがたいです。(基本的に、頂いたコメント等には全てお返事しております。)

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント

コメント一覧 (2件)

LDDのイオン種、間違ってますね…

ステップを追ってて分かりやすかったです!是非3Dのロジックとかメモリの作り方も紹介してほしいです!