みなさんこんにちは、このブログを書いている東急三崎口です。

この記事では、ラピダスが量産しようとしている2nmプロセスが難しいと言われる理由を、ざっくりわかりやすく解説していきます。

「2nmプロセス」と検索しても、半導体の専門家じゃないとわからないんじゃないかと思われる記事しか出てこなかったので、自分で書いて見ようと思って書き始めたわけです。

わかりやすさを重視しているので、細かい部分の厳密さは目をつぶっていただだけると幸いです。

この記事が好評だったら、専門家向けに細かい部分を議論する記事を書きたい思います。

2nmプロセスとは

そもそも、2nmプロセスと言われて、半導体のプロセスがある程度頭に思い描ける方は、専門家だと思います。

2nmプロセスは、ロジック半導体の最先端プロセス(2023年現在)を指す言葉です。半導体のプロセスは、○○nmと名前が付けられることが多いです。

昔のムーアの法則を引きずっている部分があるんだと思いますが、2nmプロセスはそれ以前(3nmより大きい数字の世代)と大きく変わる点があります。

3nmより大きい世代についてご存じない方は、こちらの記事を読んでみてください。

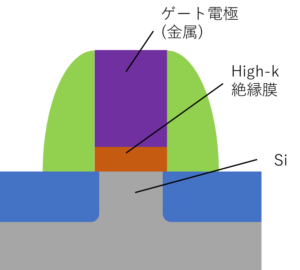

22nmプロセスより前は、プレーナー型と言われるトランジスタの形をしていました。

プレーナー型は、はるか昔からトランジスタを作るために使われてきた形です。プレーナー型のトランジスタは、トランジスタの電流をオンオフするために使われるゲートの長さをひたすら短くすることで、性能向上を図ってきました。

しかし、ゲートの長さを短くするのが限界に達してしまい、22nmプロセスの次の14nmプロセスからは、FinFETと呼ばれる型のトランジスタに移行しました。

FinFETは、断面を見ると魚のヒレ(Fin)のように見えることから、FinFETと名付けられています。

FinFETが導入されてからは、しばらくFinFETを使って性能向上が図られてきました。FinFETは、Finの幅を縮めて高さを高くすると性能が上げられるので、しばらくFinを細く高くすることが行われてきました。

しかし、FinFETでももう限界というレベルまで達してしまったので、FinFETとは違う2nmプロセスに移行することになったわけです。

FinFETと何が違うのか

2nmプロセスは、FinFETと何が違うのかというと、Finではなくシリコンのシートに電流を流します。

何を言っているのかよくわからないですよね。簡単に書いた図がこちらです。

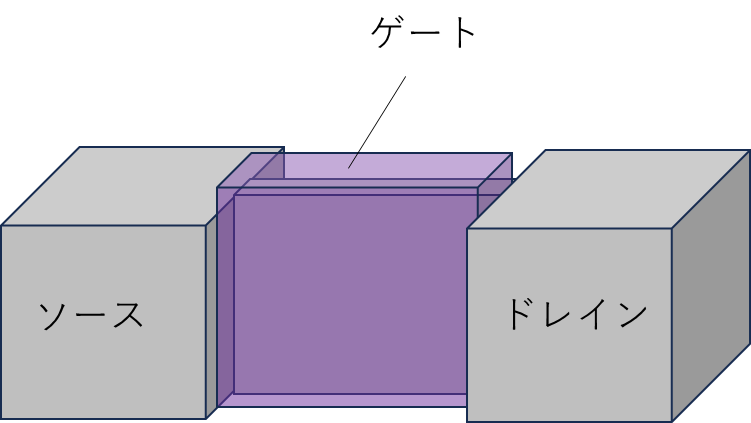

まず、FinFETの簡単な図を書くとこのようになります。

ソースからドレインに向かって電流が流れます。真ん中で細くなっているのがFinです。Finの部分を電流が流れるんですね。

Finの部分は、電流のオンオフを制御するゲートになっていて、Finの部分がシリコンでFinの外側に絶縁膜がついて、絶縁膜の外側に電極がついています。図の中では、ゲートの絶縁膜を紫色で示しています。

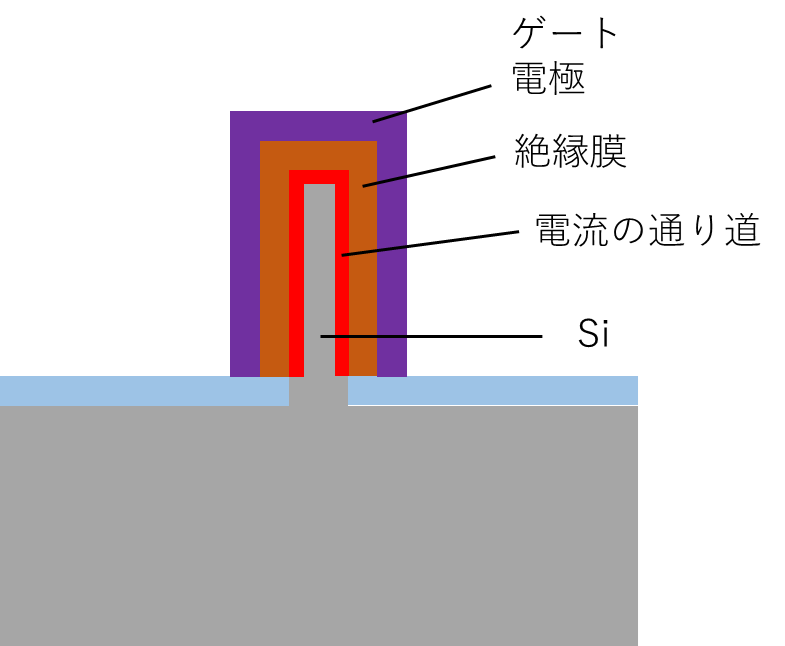

実際に電流が流れる時の模式図を、ドレイン側から見た図を書くとこのようになります。

ゲート電極に電圧をかけると、Finに電流が流れるようになります。(正確には、ゲートがオンになるように電圧をかけると、Finのシリコン表面に反転層が形成され、電流が流れるようになります。細かいことを言うとややこしくなるので、今回はゲートに電圧をかけるとFinに電流が流れるという書き方をしています。)

実際に電流が流れる部分を図の中では赤色で示しています。直感的に、Finを高くしていけば赤色の部分が増えて電流が流れやすくなるのがわかると思います。

FinFETでは、Finを高くすることで電流を稼ごうとしたわけです。

しかし、Finを無限に高くすることはできません。なぜなら、Finがちゃんと加工できて、直立してくれないとトランジスタとしての役割を果たさなくなってしまうからです。

例えば、Finをものすごい高く加工できたとしても、あとから倒れてしまったら「Fin」ではなくなってしまいます。

(半導体プロセスは非常に微細な加工をしていて、Finの高さや幅はnmオーダーです。)

というわけで、出てきたのが2nmプロセスです。

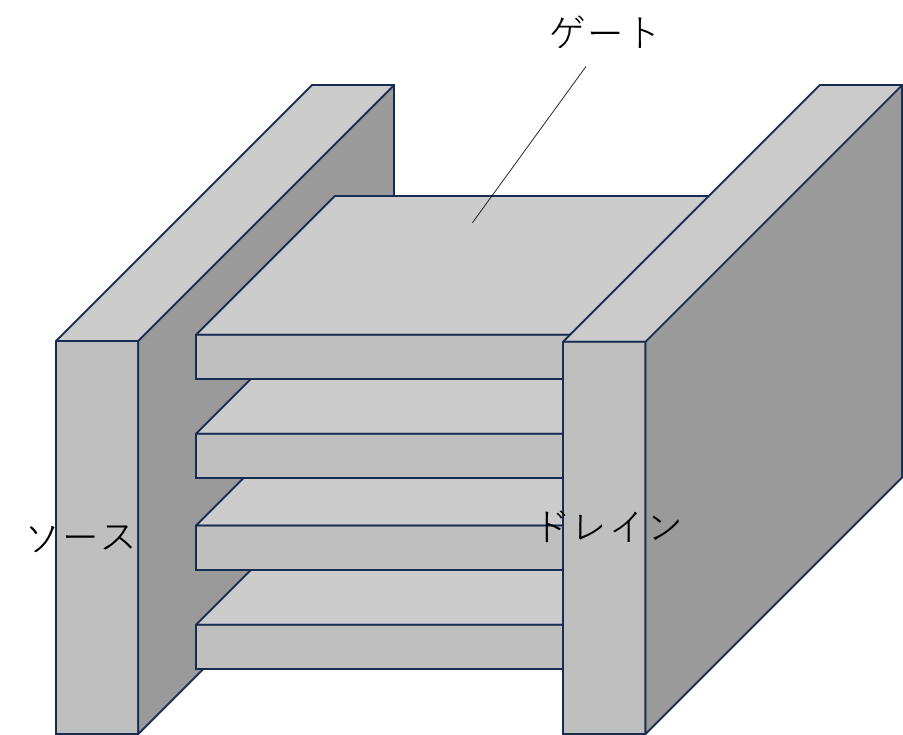

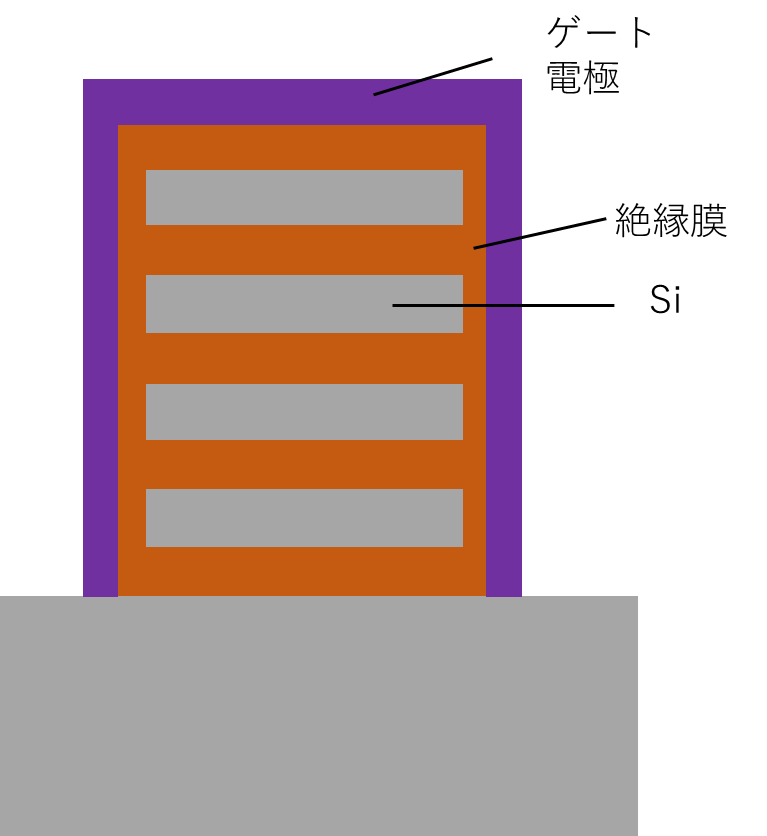

2nmプロセスの構造がどうなっているのか模式的に表したのがこちらの図です。

ややこしくなるので、ゲート絶縁膜とゲート電極の構造は省略していますが、雰囲気はこんな感じです。

ソースからドレインに向かって電流が流れるわけですが、従来の構造と違って、ゲートが薄いシートのようなものがいくつか重なった構造をしています。2nmプロセスでも、ゲートのシリコンの表面に電圧をかけることで、電流が流れるようになります。

この2nmプロセスの構造の断面をドレイン方向から見ると、このようになります。

この図では、絶縁膜とゲート電極を書き足しています。

こんな感じで、2nmプロセスのゲートは薄いシートのようなものがいくつか重なった構造になっています。

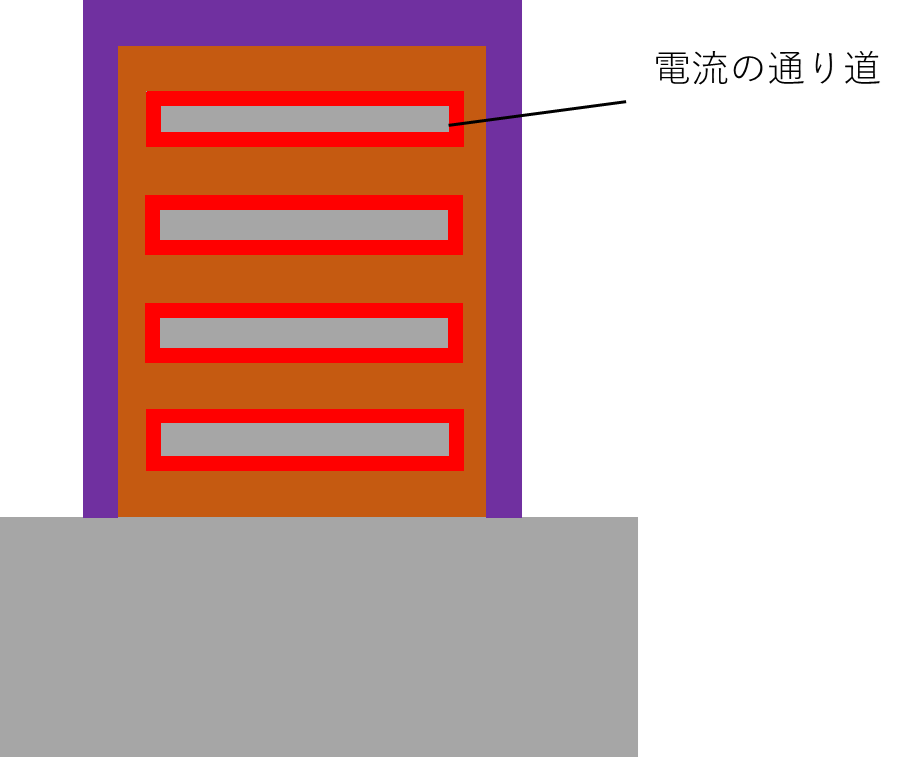

ゲートに電圧をかけて、電流を流すとこのようになります。

図中の赤い部分が、電流が流れる部分です。

お気づきの方もいらっしゃるかもしれませんが、2nmプロセスはシートを積み重ねれば積み重ねるほど、電流を流す部分を増やすことができるんです。かつては、ナノシート構造とかフォークシート構造とか呼ばれていた構造です。

FinFETとの違いを説明するだけで長くなってしまいましたが、やっとラピダスが導入しようとしているIBMのプロセスの写真にたどりつくことができます。

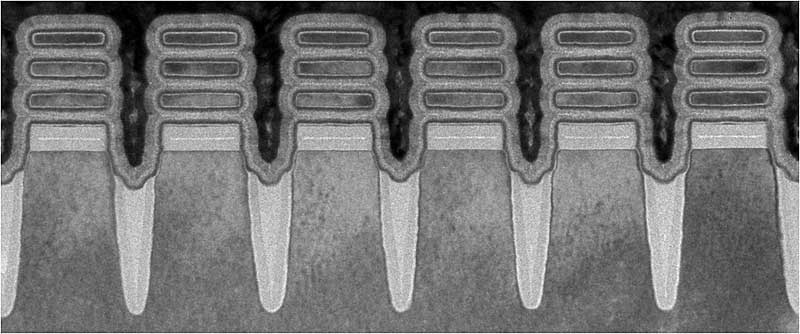

IBMの発表より引用

細かい部分は省きますが、IBMが発表した2nmプロセスで作ったトランジスタの断面写真です。

シート状のゲート部が並んでいるのが、おわかりいただけると思います。シートの部分は、シリコンで作られていて、その周りに高誘電率ゲート絶縁膜がついていて、外側をゲート電極がカバーしていることが、見受けられます。

この構造を、模式的に簡単に書き出したのが、2nmプロセスの説明に使った図です。

この断面写真を見るだけでも、色々な技術が詰め込まれていることがわかるんですが、細かいプロセスはわからない部分も多いので、とりあえず2nmプロセスはゲートがシートになっていて、シートがいくつか重なった構造になっていると理解してもらえればOKです。

2nmプロセスの難しいポイント3点

さて、ここからが本題です。ラピダスが導入予定の2nmプロセスが難しいと考えられる理由は、3つあります。

・シートの加工

・リプレイス

・周辺回路の形成

専門的な内容もありますが、1つずつ説明していきます。

シートの加工

1つ目の難しさは、シートの加工です。

ゲート部のシートは、厚さが10-20nm程度のシリコンが10nm間隔くらいで積み重ねられています。

2nmプロセスの解説の時には省きましたが、端的に言うと「どうやってこんな構造作るんだよ??」って話です。

IBMの写真からだけではわかりませんが、少し論文を読んでみると、この構造を作るためにはSiとSiGe(シリコンゲルマニウム)の層を積み重ねてあとからSiGeを抜くという方法を取るようです。

「どうやってSiGeだけ抜くんだよ?」という話は、次のリプレイスのところで解説します。

そして、SiとSiGe層を作ったあと、シートを横と分断するための加工が入ります。

この加工も、難しそうです。というのは、50nm幅くらいの溝を数100nm掘らないといけないんです。

半導体プロセスを扱ったことが無い方からすると、よくわからないと思いますが、めちゃくちゃ大変です。

一か所だけ作ればいいのであれば話は別ですが、半導体プロセスでは300mmウエハの中にチップを作らないといけません。直径30cmのシリコンの板の上に、50nm幅の溝を無数に掘るわけです。

これを、すべてのトランジスタに対して行うので、相当精密な制御が必要になります。

溝を掘るだけでも、とても大変なんだと思ってもらえればOKです。

リプレイス

2つ目の難しさは、リプレイスです。

一般的には、リプレイスというと「取り替える」という意味で使うことが多いと思います。半導体プロセスでリプレイスと呼ぶ時には、もともとあった層や膜を抜く時に使われます。

「抜く」とはどういうことかというと、2つの違う膜があった時に、一方の膜はエッチングされるけど、もう一方の膜はエッチングされない薬液などを使って、抜きたい膜や層を取り除くことを言います。

例えば、シリコンとSiO2の2つの膜から一方を抜きたいとします。この時、SiO2を抜きたい時には、フッ化水素酸を使うとSiO2だけ抜くことができます。その理由は、シリコンはフッ化水素酸にはほとんど溶けませんが、SiO2はフッ化水素酸に溶けるので、フッ化水素酸の中に入れておけば、SiO2のみを取り除くことができます。

フッ化水素酸は、通称フッ酸と呼ばれています。毒物であり、人体に触れると骨が侵される非常に危険な薬品なので、絶対使わないように気を付けてください。(半導体に関わる人以外はほとんど目に触れることはないと思いますが。)

このように、膜の種類をうまく使い分けることで、層を抜くことができるようになります。抜きたい膜と、抜きたくない膜のエッチング比率を、選択比といいます。つまり、選択比が無限大であれば一番良いわけです。(逆に1だと全然ダメです。)

本題に戻ると、SiとSiGeはあるガス(ウエットエッチングかもしれないですが)に対して選択比が取れるので、SiGeを後から抜くつもりでSiと重ねておくことで、Siのシート構造を作っているようです。

周辺回路の形成

3つ目が、周辺回路の形成です。

これは、少し専門的な話になってしまいます。IBMの写真のような2nmプロセスのトランジスタは、非常にゲート絶縁膜が薄く、シート同士の距離が短いので、掛ける電圧を低くしないといけません。(高い電圧をかけると、電圧に耐えられずトランジスタ自体が破壊してしまいます。)

しかし、2nmプロセスを使ったチップを作ろうとすると、外部から受ける電圧は、規格で決まっているので規格の電圧を受ける必要があります。

そうすると、2nmプロセスよりも高い電圧を扱えるトランジスタを同じ基板上に作る必要があります。

つまり、2nmプロセスを使ったトランジスタと同じチップ上に、FinFETやプレーナー型のトランジスタを作らないといけないわけです。

これが、非常に難しいんじゃないかと思います。トランジスタを形成するうえで、熱がかかる工程や絶縁膜の特性を維持したまま、2nmプロセス・FinFET・プレーナー型トランジスタを作りこんでいくのは至難の業になるはずです。

実際にどんなトランジスタを使うかは、チップの回路設計次第ですが、2nmプロセスのトランジスタだけですべての回路を作ることは難しいでしょうから、少なくともFinFETとの両立は必要になるのではないかと思います。

FinFETと2nmプロセスのトランジスタは、形も違いますし作るためのプロセスも違います。

そうすると、両方のトランジスタの性能を確保したうえで、1つのチップ上に両方のトランジスタを作りこんでいかないといけないと思うと、かなり難しいでしょうし、FinFETやプレーナー型トランジスタを作るときのノウハウが必要になるポイントでしょう。

試作と量産は別物

さて、ここまで2nmプロセスの難しいポイントを3つ解説しました。

IBMの断面写真は、1点モノであったとしても「開発に成功」といえるので、研究・開発の段階では問題ないです。

しかし、あの構造で製品を量産すると考えると恐ろしくなります。

というのは、あのサイズのトランジスタは直径300mmのシリコンウエハ上に一体いくつあるんだ?という話になるからです。

数nmレベルの精度が必要な加工を直径30cmのウエハ上で、一定の寸法以内に入れろというのは、どうやって管理すればいいのかがわからなくなるレベルで難しいです。

細かいことですが、少しでもSiGeの抜け残りがあってもダメですし、ゲート絶縁膜が付いていない部分があれば、回路はショートしてしまいます。

1点モノで作れるということと、製品として量産できることには大きな違いがあります。

ラピダスは、IBMから2nmプロセスのプロセスを開示してもらって、開示してもらったプロセスに準じた形で2nmプロセスの量産体制を敷く方向性のようです。

それでうまくいけば話は早いですが、うまくいかないことは目に見えています。

なぜなら、IBMのプロセスは量産適用されていないからです。つまり、とりあえず開発ラインで作れるプロセスは作ったよというのが、IBMの2nmプロセスであり、量産時の問題に関しては量産側で対応というのが実際のところでしょう。

少なくとも、IBMの2nmプロセスが手に入ったらすぐに量産出来て良品がバンバン作れるというのは、絶対に無いわけです。

2nmプロセスに着手している、TSMC・Samsung・(Intel)は開発段階は終えて、量産のための対策に移っているでしょうから、今から工場を立ち上げて2nmプロセスの量産に着手するラピダスが実際に2nmプロセスのチップを量産できる頃には、2nmプロセスより先のプロセスに着手しているでしょう。

ラピダスのプロジェクトは、経産省肝いりで国の補助金も投入されるんでしょうが、楽観的な見方をしていると、いつまでたっても量産体制が作れないことになりかねないと個人的には感じています。

まとめ

今回の記事では、ラピダスが量産しようとしている2nmプロセスが難しいと言われる理由について簡単に解説しました。

少し専門的な内容も入っていますが、ざっくり形をつかんでいただけるように気を付けたつもりです。

わからない部分があったり、もう少し専門的に書いてほしいというご希望・ご意見がありましたら、コメント欄かお問い合わせフォームからご連絡いただけると幸いです。必ずお返事するようにいたします。

このブログでは、半導体に関する記事を他にも書いています。半導体メモリ業界が中心ですが、興味がある記事があれば読んでみてください。

この記事はここまでです。最後まで読んでくださってありがとうございました。

コメント

コメント一覧 (5件)

たいへん良く分かりました。

解説有難うございました。

私はパッケージ開発エンジニアですので、ウエハープロセスは概略程度にしか分かりませんが、NANDフラッシュメモリはキオクシアの前身の東芝メモリ(東芝)が開発したものですが、200何層に3次元化されて大容量化されています。

ところが、DRAMにおいては3次元化による大容量化がされておらず、TSV(シリコン貫通電極)を使用した積層化により大容量化を実現しょうとしている様に身受けられます。

ここで、質問ですがお分かりでありましたらご回答いただければ嬉しく思います。

なぜNANDフラッシュメモリではウエハー上での3次元化プロセスが可能であり、DRAMプロセスではウエハー上での3次元化が出来なく、わざわざTSVを使った積層でしか3次元化が出来ないのか、ご教授下さい。

また、ウエハー上での3次元化として、かつて回路形成後のウエハー上に多結晶シリコンを堆積し、この多結晶シリコンにレーザーを当て、単結晶化してウエハー上での3次元化が試みられた様に思いますが、この試みは現在成功しているのかどうか、不成功であれば何が課題であったのか、お分かりでありましたらご教授頂ければ嬉しく思います。

どうそ宜しくお願い致します。

中島さん。コメントありがとうございます。東急三崎口です。

DRAMとNANDの違いと、ウエハ上の多結晶シリコンのレーザーによる単結晶化の2点についてご質問ありがとうございます。

当方、DRAMと後工程はあまり詳しくないんですが、回答できる範囲でお答えします。

>なぜNANDフラッシュメモリではウエハー上での3次元化プロセスが可能であり、DRAMプロセスではウエハー上での3次元化が出来なく、わざわざTSVを使った積層でしか3次元化が出来ないのか

「NANDフラッシュは3次元化できるのに、DRAMがTSVをわざわざやっているのか?」というところが、この質問の内容だと思います。

この理由は、NANDフラッシュとDRAMの構造の違いが原因です。

NANDフラッシュは、1つのセルで1つのデータを記憶することができます。(もちろん、セルを動かすための回路などは必要ですが。)

一方、DRAMは1つのデータを記憶するために、キャパシタとトランジスタが1つずつ必要です。

つまり、NANDフラッシュはセルさえ作れれば、いくらでも積み上げることができるわけです。

(周辺回路などが必要なのと、積層数が上がると実際にモノを作るときの難易度が上がるので、どこかで限界は来ますが。)

DRAMは、キャパシタだけなら積層することも可能だと思いますが、キャパシタを作るとトランジスタも必ずついてきます。

3次元的な構造でDRAMの電圧に対応できるトランジスタを作るのが難しいので、DRAMは3次元的な積層ではなくTSVで基板を重ねたような積層になっているんだと思われます。

DRAMはNANDフラッシュよりは高いですが、あくまでもメモリとして使われるので、先端ロジック半導体ほどチップコストを上げられないという背景もあると思います。

(3次元的にトランジスタを積層することも技術的には可能だとしても、非常に高価なプロセスになってしまい、DRAMの価格帯だと使えないという結論になるということです。)

>ウエハー上での3次元化として、かつて回路形成後のウエハー上に多結晶シリコンを堆積し、この多結晶シリコンにレーザーを当て、単結晶化してウエハー上での3次元化が試みられた様に思いますが、この試みは現在成功しているのかどうか、不成功であれば何が課題であったのか、お分かりでありましたらご教授頂ければ嬉しく思います

回路形成後のウエハに、多結晶シリコンを積みレーザーアニールして単結晶化するプロセスに関しては、やったことが無くどういう結論になっているのか存じ上げていないです。

ただ、レーザーアニールでシリコンの単結晶化をやろうとした場合の課題としては、「膜厚制御の難しさ」と「単結晶化できるのか?」があると思います。

膜厚制御の難しさという面では、レーザーアニールを使う以上、一度レーザーでシリコンの融点まで温度を上げる必要があり、そこから急冷するプロセスになるので、膜厚がばらつきやすくなります。

膜厚ばらつきが大きいと、単結晶シリコンとして使うような用途だと、性能的に難しい面があるのではないかと感じます。

単結晶化できるのかということに関しては、下地がSiO2のような絶縁膜の場合、レーザーアニールを行うと一般的には多結晶シリコンができてしまいます。

種結晶のような部分を作ってやるなどの工夫があれば、単結晶に近いものを作ることは可能だとは思いますが、大面積の基板上で形成するのは一般的には難しいです。

シリコン基板が出ている部分に対して単結晶シリコンを形成するのであれば、エピタキシャル成長を使うのが一般的です。

ちゃんとお答えしきれているかわかりませんが、ご質問いただいた2点に関してはこのとおりです。

わからない部分や、回答になっていない部分があれば、コメントいただければお返事します。

今後も半導体に関して解説記事を書いていきますので、今後ともよろしくお願いいたします。

東急三崎口さま

初めまして。

全くの門外漢ですが興味深く読ませて頂きました。

技術的な難しさは理解できたのですが、量産化に成功している(するであろう)他社との圧倒的な差はリソースにもあると思います。

ヒト、モノ、カネとよく言われますが、量産化に成功している(するであろう)ベンチマークとなる他社に比べて圧倒的にリソースが不足していると思います。

この状況でラピダスがライバル?に追いつき、同じ土俵に立てると算段できる根拠は何だと思われますでしょうか?

自分には過去の同じような失敗が繰り返されるだけなのではと憂慮しています。

MRJさん。コメントありがとうございます。東急三崎口です。

2nmに関して、ラピダスと競合他社であるTSMC・Samsung・Intelとの差をリソース(ヒト・モノ・カネ)の観点から見ると、歴然とした差があります。

ヒト・モノ・カネの中でも、ラピダスに一番不足しているのは、ヒトでしょう。

2nmより前のプロセスのノウハウが無いことも大きいですが、何よりも日本で先端ロジック半導体の研究開発をやっている人自体が非常に少ないからです。

そんな中、ラピダスが2nmプロセスを技術的に立ち上げられる可能性は、私としては非常に低いと考えています。

(理由については、こちらの記事で解説しています。https://trs-ch.blog/post-3449/)

ただ、ラピダスは補助金を投入していて補助金の原資は税金ですから、「実現できるかわからない」とは言えないのは明らかでしょう。

私の予測としては、MRJさんがおっしゃるとおり、過去の失敗を繰り返すだけになると考えています。

税金を投入したけれども、結果的に2nmプロセスの量産化ができず、会社を続けていくことができない未来になる可能性は高いです。

これからも半導体に関して解説記事を書いていきますので、今後ともよろしくお願いいたします。

[…] https://notebookpc.jp/archives/6438https://www.semiconportal.com/archive/editorial/technology/process/210507-ibm2nm.htmlhttps://trs-ch.blog/post-4763/https://www.odt.co.jp/trends/20230403/https://texal.jp/2022/06/20/what-is-gaa-fet-the-most-important-technology-for-next-generation-semiconductors/https://news.mynavi.jp/techplus/article/20221228-2548260/https://community.ibm.com/community/user/japan/viewdocument/2nm-ai?CommunityKey=4a8dd069-484f-4fec-bb5e-1da713015c48&tab=librarydocumentshttps://jp.newsroom.ibm.com/2021-05-07-IBM-unveils-worlds-first-2-nm-chip-technology-pioneering-unknown-territory-in-semiconductors […]